PROCESADOR DE SEÑAL DIGITAL CON UNIDADES MULTIPLICADORAS ACUMULADORAS ACOPLADAS.

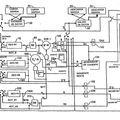

Un circuito electrónico (200) para realizar selectivamente varias operaciones independientes de multiplicación acumulación en un solo ciclo de reloj o una operación de adición de dos productos en un solo ciclo de reloj,

el circuito electrónico (200) comprende: un archivo de registro (202) que tiene una primera y una segunda entrada (PI1, PI2) y en primera instancia a través de seis salidas (PO1 a PO6); un primer multiplicador (206) que recibe la segunda y la tercera salida (PO2, PO3) del archivo de registro (202) y que tiene una salida; y un segundo multiplicador (208) que recibe la cuarta y la quinta salida (PO4, PO5) del archivo de registro (202) y que tiene una salida; un primer conmutador (204) que recibe la primera salida (PO1) del archivo de registro (202); un segundo conmutador (210) que recibe la salida del primer multiplicador (206) y que tiene una salida; un tercer conmutador (212) que recibe la salida del segundo multiplicador (208) y que tiene una salida; un multiplexor de redondeo (214) que recibe la salida del primer conmutador (204) y que tiene una salida; una primera sumadora (216) que recibe, en una primera entrada, la salida del segundo conmutador (210) y que tiene una salida; un multiplexor (218) configurado para proporcionar, de acuerdo con la operación seleccionada, un cero o la salida del tercer conmutador (212) y que aplica una salida a una segunda entrada de la primera sumadora (216); una segunda sumadora (220) que recibe las salidas del multiplexor de redondeo (214) y la primera sumadora (216), y que tiene una salida que se realimenta a la primera entrada del archivo de registro (202); y una tercera sumadora (222) que recibe las salidas del tercer conmutador (212) y la sexta salida del registro (PO6), y que tiene una salida que se realimenta a la segunda entrada (PI2) del archivo de registro (202).

Tipo: Resumen de patente/invención.

Solicitante: QUALCOMM INCORPORATED.

Nacionalidad solicitante: Estados Unidos de América.

Dirección: 5775 MOREHOUSE DRIVE,SAN DIEGO, CA 92121-1714.

Inventor/es: SIH, GILBERT, C., CHEN, XUFENG, HSU, DE, D.

Fecha de Publicación: .

Fecha Solicitud PCT: 23 de Febrero de 2001.

Fecha Concesión Europea: 18 de Enero de 2006.

Clasificación Internacional de Patentes:

- G06F7/544 FISICA. › G06 CALCULO; CONTEO. › G06F PROCESAMIENTO ELECTRICO DE DATOS DIGITALES (sistemas de computadores basados en modelos de cálculo específicos G06N). › G06F 7/00 Métodos o disposiciones para el procesamiento de datos actuando sobre el orden o el contenido de los datos tratados (circuitos lógicos H03K 19/00). › para la evaluación de funciones por cálculo.

Países PCT: Austria, Bélgica, Suiza, Alemania, Dinamarca, España, Francia, Reino Unido, Grecia, Italia, Liechtensein, Luxemburgo, Países Bajos, Suecia, Mónaco, Portugal, Irlanda, Eslovenia, Finlandia, Rumania, Chipre, Oficina Europea de Patentes, Lituania, Letonia, Ex República Yugoslava de Macedonia, Albania, Armenia, Azerbayán, Bielorusia, Ghana, Gambia, Kenya, Kirguistán, Kazajstán, Lesotho, República del Moldova, Malawi, Mozambique, Federación de Rusia, Sudán, Sierra Leona, Tayikistán, Turkmenistán, República Unida de Tanzania, Uganda, Zimbabwe, Burkina Faso, Benin, República Centroafricana, Congo, Costa de Marfil, Camerún, Gabón, Guinea, Malí, Mauritania, Niger, Senegal, Chad, Togo, Organización Regional Africana de la Propiedad Industrial, Swazilandia, Guinea-Bissau, Organización Africana de la Propiedad Intelectual, Organización Eurasiática de Patentes.

Patentes similares o relacionadas:

Método para crear una representación de un resultado de cálculo dependiente linealmente de un cuadrado de un valor, del 3 de Agosto de 2016, de FRAUNHOFER-GESELLSCHAFT ZUR FORDERUNG DER ANGEWANDTEN FORSCHUNG E.V.: Codificador de audio con un dispositivo implementado en un procesador de coma fija para el cálculo de energías de grupos espectrales de una señal de audio con […]

CIRCUITO DE PRODUCTOS POR PUNTOS PARA RECEPTORES DE MULTIPLES VIAS., del 16 de Mayo de 2006, de QUALCOMM INCORPORATED: SE PRESENTA UN METODO Y APARATO PARA CALCULAR LA PROYECCION ESCALAR DE UN VECTOR SOBRE OTRO. EL APARATO COMPRENDE UN CIRCUITO MULTIPLICADOR Y […]

PROCEDIMIENTO SIMILAR A CORDIC, DE VALORES COMPLEJOS, PARA TAREAS DE PROCESAMIENTO DE SEÑALES., del 16 de Marzo de 2004, de SIEMENS AKTIENGESELLSCHAFT: Procedimiento similar a CORDIC de valor complejo para tareas de procesamiento de señales que pueden reducirse a un problema de cuadrado mínimo […]

UN CONTROL DE GANANCIA PARA CIRCUITOS DE LINEA TELEFONICA DIGITALES, del 16 de Agosto de 1981, de STANDARD ELECTRICA, S.A.: CIRCUITO DE CONTROL DE GANANCIA PARA CONSEGUIR EL NIVEL SONORO ADECUADO EN LINEAS DE TRANSMISION DIGITALES. EN EL CIRCUITO DE TRANMISION DE ABONADO […]

PERFECCIONAMIENTOS EN SISTEMAS DE TRATAMIENTO DE SEÑALES DIGITALES, del 16 de Mayo de 1980, de FUJITSU LIMITED: Perfeccionamientos en sistemas de tratamiento de señales digitales, del tipo que ejecuten la misma función aritmética de una forma repetida, que comprende: una unidad aritmética […]

MÉTODO Y DISPOSITIVO PARA MEDIR LA POTENCIA ELÉCTRICA DE UN MOTOR ELÉCTRICO UNIVERSAL ALIMENTADO POR TENSIÓN ALTERNA SINUSOIDAL, del 13 de Octubre de 2011, de ELECTROLUX HOME PRODUCTS CORPORATION N.V.: Un método de medición de la potencia eléctrica de un motor eléctrico universal conectado a una red de alimentación de potencia eléctrica por medio de conmutación […]

APARATO Y METODO MEJORADOS PARA LA MULTIPLICACION Y EXPONENCIACION MODULARES BASADAS EN LA MULTIPLICACION DE MONTGOMERY, del 16 de Marzo de 2008, de FORTRESS U & T LTD.: Unidad aritmético lógica (ALU) microelectrónica para realizar una multiplicación modular de tipo Montgomery de P(A·B)N, donde P(P·B)N es modularmente […]

APARATO Y METODO MEJORADOS PARA LA MULTIPLICACION Y EXPONENCIACION MODULARES BASADAS EN LA MULTIPLICACION DE MONTGOMERY, del 16 de Marzo de 2008, de FORTRESS U & T LTD.: Unidad aritmético lógica (ALU) microelectrónica para realizar una multiplicación modular de tipo Montgomery de P(A·B)N, donde P(P·B)N es modularmente […]

SUPERPOSICION DE ONDAS EL ALGORITMO CORDIC., del 16 de Abril de 2007, de KONINKLIJKE PHILIPS ELECTRONICS N.V.: Método para crear una señal electrónica compuesta mediante la superposición de N ondas usando un CORDIC (Coordinate Rotation Digital Computer, ordenador digital de rotación […]