CIRCUITO INTEGRADO INVIOLABLE.

UN APARATO DE CIRCUITO INTEGRADO (IC) RESISTENTE A MANIPULACIONES SE ADAPTA PARA UTILIZARLO CON UN IC QUE INCLUYE UN COMPONENTE ACTIVO,

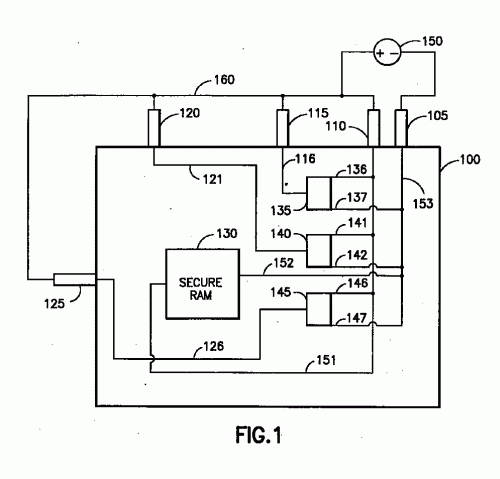

TAL COMO UN PROCESADOR DE SEGURIDAD, QUE NECESITA UNA SEÑAL DE POTENCIA CONSTANTE PARA FUNCIONAR. SI SE INTERRUMPE LA SEÑAL DE POTENCIA, SE BORRAN LOS DATOS DE UNA MEMORIA VOLATIL DEL PROCESADOR DE SEGURIDAD. LA MEMORIA SE ENCUENTRA DENTRO DEL PAQUETE DEL IC. UNA SEÑAL DE POTENCIA EXTERNA SE ACOPLA A LA MEMORIA POR MEDIO DE UNA RUTA CONDUCTORA, QUE SE LLEVA FUERA DEL CONTENEDOR Y QUE PUEDE ESTAR INCRUSTADA EN UNA TARJETA DECODIFICADORA, EN UN SUBSTRATO DE MICROMODULO O EN EL CUERPO DE UNA TARJETA INTELIGENTE EN LA QUE SE INCLUYE EL IC. LA RUTA CONDUCTORA PUEDE LLEVAR LA SEÑAL DE POTENCIA DIRECTAMENTE A LA MEMORIA, O BIEN PUEDE LLEVARLA A CONTROLAR UN TRANSISTOR. LA RETIRADA DEL PAQUETE DEL IC DE LA PLACA DECODIFICADORA, DEL SUBSTRATO DE MICROMODULO O DE LA TARJETA INTELIGENTE ABRIRA LA RUTA CONDUCTORA E INTERRUMPIRA LA SEÑAL DE POTENCIA QUE LLEGA A LA MEMORIA, CAUSANDO UN CORTOCIRCUITO O LA APERTURA DEL CIRCUITO. COMO RESULTADO, SE PERDERAN LOS DATOS QUE SE ALMACENABAN EN LA MEMORIA. DE ESTA FORMA, EL APARATO IMPIDE QUE LOS PIRATAS MANIPULEN EL INTERIOR DEL IC.

Tipo: Resumen de patente/invención.

Solicitante: GENERAL INSTRUMENT CORPORATION.

Nacionalidad solicitante: Estados Unidos de América.

Dirección: 101 TOURNAMENT DRIVE,HORSHAM, PENNSYLVANIA 19044.

Inventor/es: CANDELORE, BRANT.

Fecha de Publicación: .

Clasificación Internacional de Patentes:

- G06F1/00 FISICA. › G06 CALCULO; CONTEO. › G06F PROCESAMIENTO ELECTRICO DE DATOS DIGITALES (sistemas de computadores basados en modelos de cálculo específicos G06N). › Detalles no cubiertos en los grupos G06F 3/00 - G06F 13/00 y G06F 21/00 (arquitecturas de computadores con programas almacenados de propósito general G06F 15/76).

- G06F12/14 G06F […] › G06F 12/00 Acceso, direccionamiento o asignación en sistemas o arquitecturas de memoria (entrada digital a partir de, o salida digital hacia soportes de registro, p. ej. hacia unidades de almacenamiento de disco G06F 3/06). › Protección contra la utilización no autorizada de la memoria.

- G11C7/00 G […] › G11 REGISTRO DE LA INFORMACION. › G11C MEMORIAS ESTATICAS (dispositivos semiconductores para memorias H01L, p. ej. H01L 27/108 - H01L 27/11597). › Disposiciones para escribir una información o para leer una información en una memoria digital (G11C 5/00 tiene prioridad; circuitos auxiliares para memorias que utilizan dispositivos semiconductores G11C 11/4063, G11C 11/413, G11C 11/4193).

- H01L23/58 ELECTRICIDAD. › H01 ELEMENTOS ELECTRICOS BASICOS. › H01L DISPOSITIVOS SEMICONDUCTORES; DISPOSITIVOS ELECTRICOS DE ESTADO SOLIDO NO PREVISTOS EN OTRO LUGAR (utilización de dispositivos semiconductores para medida G01; resistencias en general H01C; imanes, inductancias, transformadores H01F; condensadores en general H01G; dispositivos electrolíticos H01G 9/00; pilas, acumuladores H01M; guías de ondas, resonadores o líneas del tipo guía de ondas H01P; conectadores de líneas, colectores de corriente H01R; dispositivos de emisión estimulada H01S; resonadores electromecánicos H03H; altavoces, micrófonos, cabezas de lectura para gramófonos o transductores acústicos electromecánicos análogos H04R; fuentes de luz eléctricas en general H05B; circuitos impresos, circuitos híbridos, envolturas o detalles de construcción de aparatos eléctricos, fabricación de conjuntos de componentes eléctricos H05K; empleo de dispositivos semiconductores en circuitos que tienen una aplicación particular, ver la subclase relativa a la aplicación). › H01L 23/00 Detalles de dispositivos semiconductores o de otros dispositivos de estado sólido (H01L 25/00 tiene prioridad). › Disposiciones eléctricas estructurales no previstas en otra parte para dispositivos semiconductores.

Patentes similares o relacionadas:

Arquitectura e instrucciones flexibles para el estándar de cifrado avanzado (AES), del 27 de Mayo de 2020, de INTEL CORPORATION: Un procesador que comprende: una pluralidad de núcleos; una caché de instrucciones de nivel 1, L1, para almacenar una pluralidad de instrucciones […]

Procedimiento de control sistemático de direcciones de zonas de memoria en el marco de una transferencia por acceso directo, del 1 de Abril de 2020, de THALES: Procedimiento de control sistemático por un dispositivo de control de al menos un mensaje de configuración de transferencia, siendo el mensaje de configuración […]

Servidor de seguridad de soporte lógico, del 19 de Febrero de 2020, de Idemia Identity & Security France: Procedimiento de verificación de ejecución de applets (AA1, AB1) desarrolladas en un lenguaje orientado objeto y compiladas en código intermedio, siendo el procedimiento […]

Múltiples conjuntos de campos de atributos dentro de una única entrada de tabla de páginas, del 25 de Septiembre de 2019, de QUALCOMM INCORPORATED: Un procedimiento que comprende: traducir , por una primera unidad de procesamiento , una dirección de memoria virtual a una […]

Procedimiento para proteger datos relevantes para la seguridad en una memoria caché, del 14 de Agosto de 2019, de SIEMENS AKTIENGESELLSCHAFT: Procedimiento para proteger datos relevantes para la seguridad en una memoria caché, archivándose una copia de los datos relevantes para la seguridad […]

Archivo seguro, del 7 de Agosto de 2019, de Waterfall Security Solutions Ltd: Aparato de almacenamiento, que comprende: una memoria ; un procesador de encriptado , que está configurado para recibir y encriptar datos transmitidos desde uno […]

Sistemas y métodos para proporcionar como salida un resultado de una instrucción de procesador vigente tras su salida de una máquina virtual, del 3 de Abril de 2019, de Bitdefender IPR Management Ltd: Un sistema anfitrión que comprende al menos un procesador hardware configurado para ejecutar una máquina virtual y un programa de seguridad informática, en donde el al menos […]

Sistema y método para la gestión distribuida de ordenadores compartidos, del 20 de Febrero de 2019, de Zhigu Holdings Limited: Método para operar una arquitectura de gestión informática de múltiples niveles, teniendo dicho método los siguientes pasos: operar un ordenador […]