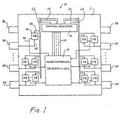

ORDENADOR DE ARQUITECTURA HARVARD SUPERESCALAR MASIVAMENTE MULTIPLEXADO.

SE PRESENTA UNA UNIDAD CENTRAL DE PROCESAMIENTO (CPU) MASIVAMENTE MULTIPLEXADO QUE TIENE UNA PLURALIDAD DE CIRCUITOS COMPUTACIONALES INDEPENDIENTES,

UN BUS DE RESULTADOS INTERNOS SEPARADO PARA TRANSMITIR LA SALIDA RESULTANTE DE CADA UNO DE ESTOS CIRCUITOS COMPUTACIONALES, Y UNA PLURALIDAD DE REGISTROS DE PROPOSITO GENERAL ACOPLADOS A CADA UNO DE LOS CIRCUITOS COMPUTACIONALES. CADA UNO DE LOS REGISTROS DE PROPOSITOS GENERAL TIENEN PUERTOS DE ENTRADA MULTIPLEXADOS QUE ESTAN CONECTADOS A CADA UNO DE LOS BUSES DE RESULTADOS. CADA UNO DE LOS REGISTROS DE PROPOSITO GENERAL TAMBIEN TIENE UN PUERTO DE SALIDA QUE ESTA CONECTADO A UN PUERTO DE ENTRADA MULTIPLEXADO DE AL MENOS UNO DE LOS CIRCUITOS COMPUTACIONALES. CADA UNO DE LOS CIRCUITOS COMPUTACIONALES ESTA DEDICADO A AL MENOS UNA FUNCION MATEMATICA UNICA, Y AL MENOS UNO DE LOS CIRCUITOS COMPUTACIONALES INCLUYE AL MENOS UNA FUNCION LOGICA. AL MENOS UNO DE LOS CIRCUITOS COMPUTACIONALES INCLUYE UNA PLURALIDAD DE CIRCUITOS DE PROCESAMIENTO MATEMATICOS Y LOGICOS CONCURRENTEMENTE ACCIONABLES, Y UN MULTIPLEXADOR DE SALIDA PARA SELECCIONAR UNA DE LAS SALIDAS RESULTANTES PARA SU TRANSMISION SOBRE SU BUS DE RESULTADOS. LA CPU TAMBIEN INCORPORA UNA PALABRA DE INSTRUCCION MUY LARGA QUE UTILIZA UNA SERIE DE UBICACION DE BITS ASIGNADAS PARA REPRESENTAR LOS CODIGOS DE SELECCION PARA CADA UNO DE LOS COMPONENTES DE LA CPU. ESTOS CODIGOS DE SELECCION SON DIRECTAMENTE TRANSMITIDOS A CADA UNO DE LOS COMPONENTES DE LA CPU MEDIANTE UN CIRCUITO DE CONTROL DE PROGRAMA. SE SUMINISTRA ADEMAS UN CIRCUITO DE CONTROL DE DATOS SEPARADO EN UN DISEÑO DE ESTRUCTURA HARVARD PARA LA CPU.

Tipo: Resumen de patente/invención.

Solicitante: THE DOW CHEMICAL COMPANY.

Nacionalidad solicitante: Estados Unidos de América.

Dirección: 2030 DOW CENTER, ABBOTT ROAD,MIDLAND, MICHIGAN 48640.

Inventor/es: ROOT, LARRY, A., DUPREE, WAYNE, P., CHURCHILL, STEPHEN, G., GALLANT, JEFFRY, R., BRESSETTE, WILLIAM, J., ORR, ROBERT, A., III, RAMASWAMY, SRIKALA, LUCAS, JEFFREY, A., BLECK, JAMES, A.

Fecha de Publicación: .

Fecha Solicitud PCT: 10 de Enero de 1995.

Fecha Concesión Europea: 16 de Agosto de 2000.

Clasificación Internacional de Patentes:

- G06F15/78 FISICA. › G06 CALCULO; CONTEO. › G06F PROCESAMIENTO ELECTRICO DE DATOS DIGITALES (sistemas de computadores basados en modelos de cálculo específicos G06N). › G06F 15/00 Computadores digitales en general (detalles G06F 1/00 - G06F 13/00 ); Equipo de procesamiento de datos en general. › que comprenden una sola unidad central.

- G06F9/30 G06F […] › G06F 9/00 Disposiciones para el control por programa, p. ej. unidades de control (control por programa para dispositivos periféricos G06F 13/10). › Disposiciones para ejecutar instrucciones de máquinas, p. ej. decodificación de instrucciones (para ejecutar microinstrucciones G06F 9/22).

- G06F9/38 G06F 9/00 […] › Ejecución simultánea de instrucciones, p. ej. segmentación, anticipación.

Países PCT: Austria, Bélgica, Suiza, Alemania, Dinamarca, España, Francia, Reino Unido, Grecia, Italia, Liechtensein, Luxemburgo, Países Bajos, Mónaco, Irlanda, Oficina Europea de Patentes.

Patentes similares o relacionadas:

Red y método para sistemas informáticos escalables accionados por eventos, del 8 de Julio de 2020, de UNIVERSITAT ZURICH: Una red que comprende una pluralidad de circuitos de núcleo interconectados , en la que cada circuito de núcleo comprende: - una matriz […]

Procedimiento de diseño de una arquitectura reconfigurable de tratamiento de un conjunto de operaciones multinivel de seguridad, del 8 de Enero de 2020, de THALES: Procedimiento de diseño de una arquitectura de tratamiento de un conjunto de operaciones efectuadas sobre datos, en el que algunos datos requieren un nivel […]

Dominios de potencia controlados por hardware con potencia automática a petición, del 28 de Agosto de 2019, de TELEFONAKTIEBOLAGET LM ERICSSON (PUBL): Un sistema de hardware que comprende: una pluralidad de bloques de hardware que comprenden, cada uno, uno o más componentes de hardware; […]

Canalización de recursos de cálculo en unidad de procesamiento de gráficos de propósito general, del 24 de Julio de 2019, de QUALCOMM INCORPORATED: Una unidad de procesamiento de gráficos de propósito general, GPGPU, que comprende: una pluralidad de unidades de procesamiento en paralelo […]

Configuración de modo arquitectónico en un sistema informático, del 27 de Febrero de 2019, de INTERNATIONAL BUSINESS MACHINES CORPORATION: Un método para reconfigurar un entorno informático, dicho método que comprende: determinar, mediante un procesador, que un indicador de instalación de facilidad […]

Sistema y procedimiento para proporcionar una canalización de gráficos mejorada, del 3 de Enero de 2018, de Microsoft Technology Licensing, LLC: Un procedimiento de procesamiento de datos, que comprende: programar un elemento (184'-1a1, 184'-1a2, 184'-1a3, 184'-1a4) de núcleo común de una unidad (184') de […]

Procedimiento para proporcionar un microcontrolador que tiene una anchura de bus de datos en n-bit y un número de clavijas igual o inferior a N, del 21 de Agosto de 2013, de MICROCHIP TECHNOLOGY INCORPORATED: Un procedimiento para dotar a un paquete de Circuito Integrado (IC) con una funcionalidad de microcontrolador,que comprende:

dotar a un chip […]

Procedimiento para proporcionar un microcontrolador que tiene una anchura de bus de datos en n-bit y un número de clavijas igual o inferior a N, del 21 de Agosto de 2013, de MICROCHIP TECHNOLOGY INCORPORATED: Un procedimiento para dotar a un paquete de Circuito Integrado (IC) con una funcionalidad de microcontrolador,que comprende:

dotar a un chip […]

SISTEMA DE CONTROL DE AUTOMOVIL Y METODO CAPAZ DE REVISAR LA FUNCION DE TRANSMISION DE DATOS DE CONTROL., del 1 de Abril de 2007, de DENSO CORPORATION: Un sistema de control de automóvil dotado de una unidad de procesamiento de la información adaptada para realizar un proceso aritmético para […]