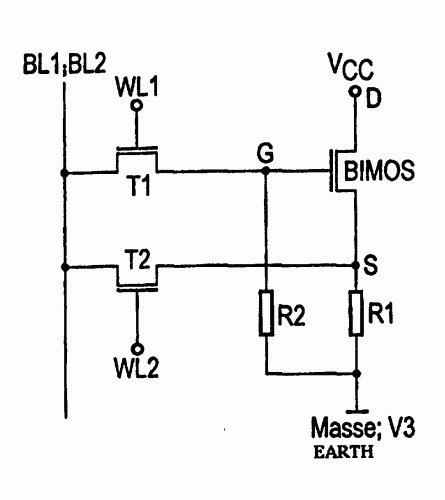

CELULA DE MEMORIA SRAM.

LA INVENCION SE REFIERE A UNA CELULA DE ALMACENAMIENTO DE 3 TRANSISTORES QUE CONTIENE UN TRANSISTOR BIESTABLE DE EFECTO CAMPO BIMOS CON UNA REGION DE CANAL FLOTANTE TOTALMENTE VACIA QUE PRESENTA UNA CARACTERISTICA DE VOLTAJE DE COMPUERTA CONDICIONADA POR HISTERESIS.

A EFECTOS DE GRABACION, LA COMPUERTA (G) DE LA CELULA DE ALMACENAMIENTO PUEDE CONECTARSE A UN PRIMER CONDUCTOR DE BIT (BL1) Y, A EFECTOS DE LECTURA, SU SEGUNDA CONEXION DE CANAL (S) PUEDE UNIRSE A UN SEGUNDO CONDUCTOR DE BIT (BL2), PUDIENDO SER AMBOS CONDUCTORES DE BIT (BL1, BL2) IDENTICOS. LA CONEXION ENTRE LOS CONDUCTORES DE BIT (BL1, BL2) Y EL TRANSISTOR BIESTABLE BIMOS PUEDE REALIZARSE POR MEDIO DE UN PRIMER TRANSISTOR (T1) O UN SEGUNDO TRANSISTOR (T2), ESTANDO CADA TRANSISTOR CONTROLADO POR UNA LINEA DE PALABRA (WL1, WL2).

Tipo: Resumen de patente/invención.

Solicitante: SIEMENS AKTIENGESELLSCHAFT.

Nacionalidad solicitante: Alemania.

Dirección: WITTELSBACHERPLATZ 2,80333 MUNCHEN.

Inventor/es: WITTMANN, FRANZ, GOSSNER, HARALD, DR., EISELE, IGNAZ, PROF., RAMGOPAL RAO, VALIPE.

Fecha de Publicación: .

Fecha Solicitud PCT: 16 de Septiembre de 1996.

Fecha Concesión Europea: 16 de Junio de 1999.

Clasificación Internacional de Patentes:

- G11C11/40 FISICA. › G11 REGISTRO DE LA INFORMACION. › G11C MEMORIAS ESTATICAS (dispositivos semiconductores para memorias H01L, p. ej. H01L 27/108 - H01L 27/11597). › G11C 11/00 Memorias digitales caracterizadas por la utilización de elementos de almacenamiento eléctricos o magnéticos particulares; Elementos de almacenamiento correspondientes (G11C 14/00 - G11C 21/00 tienen prioridad). › que utilizan transistores.

Países PCT: Austria, Suiza, Alemania, España, Francia, Reino Unido, Italia, Liechtensein, Oficina Europea de Patentes.

Patentes similares o relacionadas:

PERFECCIONAMIENTOS EN MEMORIAS DE CIRCUITOS INTEGRADOS, del 16 de Febrero de 1981, de MOSTEK CORPORATION: CIRCUITO PARA CELULA DE MEMORIA DISPUESTA EN CIRCUITO INTEGRADO. UNA CELULA DISPONE DE DOS LINEAS DE ENTRADA DE DATOS COMPLEMENTARIOS (D, D); DOS RESISTENCIAS (R1, […]

PERFECCIONAMIENTOS EN CELULAS DE MEMORIAS DE CIRCUITO INTEGRADO, del 16 de Septiembre de 1980, de MOSTEK CORPORATION: La presenta invención consigue una reducción de área debido a la alimentación de la línea de datos a nivel del substrato. Esta línea de datos se forma […]