MECANISMO EN UN MICROPROCESADOR PARA EJECUTAR INSTRUCCIONES NATIVAS DIRECTAMENTE DESDE LA MEMORIA.

Un aparato en un microprocesador para ejecutar las instrucciones nativas que se proporcionan directamente al microprocesador a través de un canal principal de instrucciones externas,

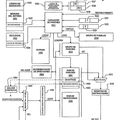

el aparato que comprende: la lógica de traducción de instrucciones, configurada para recuperar las macroinstrucciones proporcionadas a través del canal principal de instrucciones externas, y configurado para traducir cada una de dichas macroinstrucciones en instrucciones nativas asociadas para la ejecución, en donde, si se recupera una primera forma de una primera macroinstrucción, dicha lógica de traducción de instrucciones dirige el microprocesador a habilitar un modo de desviación nativo e indica tal mediante la afirmación de un primer bit dentro de un registro de control; y la lógica de desviación, acoplada a dicha lógica de traducción de instrucciones, configurada para acceder dicho primer bit dentro de dicho registro de control para determinar si se ha habilitado dicho modo de desviación nativo, y detectar las macroinstrucciones de envoltura y, tras la detección de dichas macroinstrucciones de envoltura, deshabilitar dicha lógica de traducción de instrucciones, y proporcionar las instrucciones nativas para la ejecución por el microprocesador, desviando por ello dicha lógica de traducción de instrucciones, caracterizado porque: cada una de dichas macroinstrucciones de envoltura comprende una macroinstrucción de acuerdo con las especificaciones de arquitectura que tienen una instrucción nativa codificada allí dentro; y dichas macroinstrucciones de envoltura son macroinstrucciones existentes que se traducen por dicha lógica de traducción de instrucciones de acuerdo con las especificaciones de arquitectura si no ha sido habilitado dicho modo de desviación nativo

Tipo: Patente Europea. Resumen de patente/invención. Número de Solicitud: E04255589.

Solicitante: IP-FIRST LLC.

Nacionalidad solicitante: Estados Unidos de América.

Dirección: 1045 MISSION COURT FREMONT, CA 94539 ESTADOS UNIDOS DE AMERICA.

Inventor/es: PARKS,TERRY, HENRY,G. GLENN, MARTIN-DE-NICOLAS,ARTURO.

Fecha de Publicación: .

Fecha Solicitud PCT: 15 de Septiembre de 2004.

Fecha Concesión Europea: 11 de Agosto de 2010.

Clasificación Internacional de Patentes:

- G06F9/318 FISICA. › G06 CALCULO; CONTEO. › G06F PROCESAMIENTO ELECTRICO DE DATOS DIGITALES (sistemas de computadores basados en modelos de cálculo específicos G06N). › G06F 9/00 Disposiciones para el control por programa, p. ej. unidades de control (control por programa para dispositivos periféricos G06F 13/10). › con extensión o modificación de operaciones.

- G06F9/318T

Clasificación PCT:

- G06F9/30 G06F 9/00 […] › Disposiciones para ejecutar instrucciones de máquinas, p. ej. decodificación de instrucciones (para ejecutar microinstrucciones G06F 9/22).

Clasificación antigua:

- G06F9/30 G06F 9/00 […] › Disposiciones para ejecutar instrucciones de máquinas, p. ej. decodificación de instrucciones (para ejecutar microinstrucciones G06F 9/22).

Países PCT: Austria, Bélgica, Suiza, Alemania, Dinamarca, España, Francia, Reino Unido, Grecia, Italia, Liechtensein, Luxemburgo, Países Bajos, Suecia, Mónaco, Portugal, Irlanda, Eslovenia, Finlandia, Rumania, Chipre, Lituania, Letonia, Ex República Yugoslava de Macedonia, Albania.

Fragmento de la descripción:

REFERENCIA CRUZADA A LAS SOLICITUDES RELACIONADAS

Esta solicitud es una continuación parcial de la Solicitud de Patente de EE.UU. co-pendiente Nº de Serie 09/640118 (Nº Legajo CNTR. 1356) titulada MODO DE DESVIACIÓN DE TRADUCTOR PARA INSTRUCCIONES NATIVAS, que fue solicitada el 16/06/2000.

ANTECEDENTES DE LA INVENCIÓN

CAMPO DE LA INVENCIÓN

Esta invención se refiere en general al campo del procesamiento de instrucciones en sistemas informáticos, y más concretamente a un aparato que permite a un microprocesador ejecutar programas de aplicaciones directamente desde la memoria, donde los programas de aplicaciones se codifican usando microinstrucciones nativas.

DESCRIPCIÓN DE LA TÉCNICA RELACIONADA

Los microprocesadores ejecutan programas de aplicaciones para automatizar ciertas tareas tales como la regulación de la temperatura de un elemento de calentamiento dentro de una cafetera, el control de la distribución de dinero de un cajero automático, o procesar números en una hoja de cálculo de acuerdo con una fórmula de operador de entrada en un ordenador de sobremesa.

Las instrucciones de programación usadas para escribir los programas de aplicaciones para los primeros microprocesadores eran únicas para el microprocesador particular. Por ejemplo, el microprocesador Intel® 4004, producido a principios de los 1970, tenía 46 instrucciones a partir de las cuales un programador podría elegir escribir los programas de aplicaciones. Y los programas que estaban escritos para el 4004 solamente se ejecutarían en el 4004.

Desde los inicios de los 1970, han sido desarrollados cientos de diseños de microprocesadores distintos. Y mientras que muchos de estos microprocesadores eran diseños originales, algunos fabricantes intentaron capturar segmentos de mercado desarrollado microprocesadores clónicos que eran capaces de ejecutar programas de aplicaciones que eran codificados originalmente para ejecutarse en un microprocesador distinto. La importancia de ser capaz de ejecutar aplicaciones “heredadas” llegaron a ser extremadamente predominantes en la técnica en 1979 cuando el Departamento de Defensa (DoD) afirmó su significativa inversión en programación de aplicaciones publicando la MIL-STD-1750, un estándar militar que documenta las características del diseño de alto nivel de un microprocesador conceptual de 16 bit para uso en todos los sistemas de armamento y aerotransportados futuros. La MIL-STD-1750 se conocía como una arquitectura de conjunto de instrucciones (ISA) porque, además de especificar las características de la arquitectura de un microprocesador tales como los tipos y números de registros internos direccionables, también se documentan de manera precisa un conjunto de instrucciones de programación a ser ejecutadas en el microprocesador conceptual. De esta manera, con el estándar de arquitectura ya desarrollado por los militares, los fabricantes fueron libres de diseñar microprocesadores adecuados que implementaban la arquitectura de la 1750 usando el diseño y las técnicas de fabricación que optimizaban sus productos hacia ciertas características deseables. Por ejemplo, un fabricante podía implementar la arquitectura de la 1750 de tal manera que maximiza la velocidad de un microprocesador de la 1750. Otro fabricante podía optimizar su producto para maximizar su resistencia a las señales de radiación electromagnéticas. Otro fabricante podía personalizar su producto para minimizar el coste del producto. Y a pesar de qué características fueran enfatizadas por una implementación de diseño particular, cada uno de las implementaciones de los microprocesadores de la 1750 eran capaces de ejecutar los programas de aplicaciones que estaban codificados de acuerdo con la ISA de la 1750.

Esta tendencia explotó en el mercado comercial durante los 1980 cuando los ordenadores de sobremesa comenzaron a proliferar en la comunidad de negocios. A medida que los programas de aplicaciones ganaban en popularidad, los usuarios comenzaron a requerir a la industria proporcionar microprocesadores tecnológicamente más avanzados y mejorados que aún fueran capaces de ejecutar estas populares aplicaciones de programas informáticos. Consecuentemente, los diseñadores de los microprocesadores desde entonces se han centrado en proporcionar diseños de microprocesadores más rápidos, más robustos, más fiables, más eficientes energéticamente, y menos costosos que son capaces de ejecutar tanto los nuevos programas informáticos como las aplicaciones heredadas. Dentro de la industria informática de sobremesa de hoy, quizás la ISA más ampliamente usada es la ISA de 32 bit de Intel®. La ISA de 32 bit, o ISA x86, documenta cientos de instrucciones de programación que se pueden usar en una amplia variedad de formas de direccionamiento para el procesamiento de los datos dentro de un ordenador de sobremesa de hoy en día. Hoy, muchos fabricantes distintos producen microprocesadores compatibles con x86. Y el diseño de cada uno de estos microprocesadores compatibles con x86, como era el caso de los microprocesadores de la 1750, se personaliza a características particulares subrayadas tales como la complejidad, potencia, velocidad, o coste.

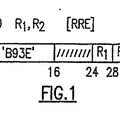

Para implementar un microprocesador físico conforme a una ISA particular, los diseñadores de hoy emplean una serie de técnicas, todas ellas son completamente transparentes a un programador de aplicaciones. Mientras que el programador de aplicaciones está preocupado de que un microprocesador conforme proporcione los tipos documentados y número de registros internos, y que el microprocesador sea capaz de ejecutar las instrucciones ISA de acuerdo con la especificación, generalmente no es consciente de cómo se proporcionan tales capacidades de conformidad. Los componentes físicos y los dispositivos lógicos internos documentados dentro de una ISA que deben estar disponibles para la programación de aplicaciones se conocen generalmente como “recursos arquitectónicos”. Los componentes físicos y la lógica proporcionada dentro de un diseño de microprocesador para implementar estos recursos arquitectónicos de una manera que favorece algún aspecto particular del diseño se llaman a menudo “recursos nativos”. Por ejemplo, la ISA x86 documenta ocho registros arquitectónicos internos que se pueden ordenar explícitamente por las macroinstrucciones x86. Aún, un experto en la técnica apreciará que un microprocesador compatible con x86 de hoy en día tiene cientos de registros nativos que se usan para una amplia variedad de propósitos. Pero aunque el uso de recursos nativos en un microprocesador de hoy en día es prolífico, el ejercicio de estos recursos nativos y la manera en que se ordenan para usar no es típicamente observable a un programador de aplicaciones ni puede ordenar explícitamente su uso dentro de un programa de aplicaciones. Esto es porque sus aplicaciones se codifican usando macroinstrucciones de acuerdo con una ISA particular y las macroinstrucciones no se proporcionan para direccionar o emplear registros nativos y otros recursos.

Consecuentemente, un microprocesador de hoy en día ejecuta programas desde la memoria que se codifican usando macroinstrucciones de acuerdo con una ISA particular. Estas macroinstrucciones dirigen el uso de varios rasgos, funciones, y recursos arquitectónicos dentro del microprocesador. Pero dentro unos pocos ciclos de reloj de búsqueda de una macroinstrucción desde la memoria, los microprocesadores de hoy traducen la macroinstrucción en una secuencia de instrucciones nativas correspondientes. Las instrucciones nativas se diseñan para utilizar eficientemente y efectivamente los recursos nativos dentro del microprocesador para llevar a cabo las operaciones de la arquitectura ordenadas por la macroinstrucción. Por ejemplo, una macroinstrucción que ordena un cambio de contenidos de dos registros arquitectónicos se puede traducir en una secuencia de tres instrucciones nativas: una primera instrucción nativa que recupera los contenidos de un primer registro arquitectónico y que almacena los contenidos en un registro nativo, una segunda instrucción nativa que mueve el contenido de un segundo registro arquitectónico al primer registro arquitectónico, y una tercera instrucción nativa que mueve los contenidos del registro nativo al segundo registro arquitectónico.

Pero mientras que las funciones para ejercitar los recursos arquitectónicos dentro de un microprocesador de hoy en día se pueden programar y ejecutar usando macroinstrucciones, lo mismo no se puede decir para el ejercicio de los recursos nativos. Y desde el punto de vista de un ingeniero de pruebas...

Reivindicaciones:

1. Un aparato en un microprocesador para ejecutar las instrucciones nativas que se proporcionan directamente al microprocesador a través de un canal principal de instrucciones externas, el aparato que comprende:

la lógica de traducción de instrucciones, configurada para recuperar las macroinstrucciones proporcionadas a través del canal principal de instrucciones externas, y configurado para traducir cada una de dichas macroinstrucciones en instrucciones nativas asociadas para la ejecución, en donde, si se recupera una primera forma de una primera macroinstrucción, dicha lógica de traducción de instrucciones dirige el microprocesador a habilitar un modo de desviación nativo e indica tal mediante la afirmación de un primer bit dentro de un registro de control; y la lógica de desviación, acoplada a dicha lógica de traducción de instrucciones, configurada para acceder dicho primer bit dentro de dicho registro de control para determinar si se ha habilitado dicho modo de desviación nativo, y detectar las macroinstrucciones de envoltura y, tras la detección de dichas macroinstrucciones de envoltura, deshabilitar dicha lógica de traducción de instrucciones, y proporcionar las instrucciones nativas para la ejecución por el microprocesador, desviando por ello dicha lógica de traducción de instrucciones, caracterizado porque: cada una de dichas macroinstrucciones de envoltura comprende una macroinstrucción de acuerdo con las especificaciones de arquitectura que tienen una instrucción nativa codificada allí dentro; y dichas macroinstrucciones de envoltura son macroinstrucciones existentes que se traducen por dicha lógica de traducción de instrucciones de acuerdo con las especificaciones de arquitectura si no ha sido habilitado dicho modo de desviación nativo.

2. El aparato como se expone en la reivindicación 1, en donde las instrucciones nativas se integran dentro de dichas instrucciones de envoltura y se proporcionan desde una memoria al canal principal de instrucciones externas.

3. El aparato como se expone en la reivindicación 1, en donde el microprocesador emplea un segundo bit dentro de un registro de banderas para indicar la ocurrencia de un evento de interrupción.

4. El aparato como se expone en la reivindicación 3, que además comprende:

la lógica de interrupción/excepción/conmutación, configurada para borrar dicho primer bit dentro de dicho registro de control tras la ocurrencia de dicho evento de interrupción y antes de transferir el control a una rutina de servicio de evento de interrupción, deshabilitando por ello dicho modo de desviación nativo, y configurada para afirmar dicho segundo bit dentro de dicho registro de banderas, indicando por ello la ocurrencia de dicho evento de interrupción.

5. El aparato como se expone en la reivindicación 4, en donde dicho registro de banderas comprende un registro EFLAGS x86, y en donde dicho segundo bit comprende el bit 31 dentro de dicho registro EFLAGS x86.

6. El aparato como se expone en la reivindicación 1, en donde dicha lógica de desviación comprende:

un encaminador de instrucciones nativas, acoplado a la lógica de detección de modo, configurado para recibir dichas macroinstrucciones de envoltura, y configurado para quitar las instrucciones nativas de dentro de dichas macroinstrucciones de envoltura, y configurado para encaminar las instrucciones nativas a un canal principal de instrucciones nativas.

7. El aparato como se expone en la reivindicación 1, si se recupera una segunda forma de dicha primera macroinstrucción, dicha lógica de traducción de instrucciones dirige al microprocesador a deshabilitar dicho modo de desviación nativo e indica tal borrando dicho primer bit dentro de dicho registro de control.

8. Un método para proporcionar una pluralidad de instrucciones nativas almacenadas en una memoria directamente a un microprocesador para la ejecución, el método que comprende:

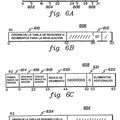

habilitar un modo de desviación de instrucciones dentro del microprocesador; integrar la pluralidad de instrucciones nativas dentro de una correspondiente pluralidad de instrucciones de envoltura y proporcionar la pluralidad correspondiente de instrucciones de envoltura al microprocesador; y dentro del microprocesador, detectar el modo de desviación de instrucciones nativo y extraer la pluralidad de instrucciones nativas de dentro de la pluralidad correspondiente de instrucciones de envoltura, caracterizado porque: la correspondiente pluralidad de instrucciones de envoltura son macroinstrucciones existentes de acuerdo con dichas especificaciones de arquitectura que tienen una instrucción nativa codificada allí dentro, tal que dicha instrucción de envoltura se puede traducir por la lógica de traducción de instrucciones de acuerdo con las especificaciones de arquitectura cuando no está habilitado dicho modo de desviación de instrucciones nativas.

9. El método como se expone en la reivindicación 8, en donde dicha habilitación comprende:

detectar una primera forma de una macroinstrucción de otra manera inválida; y afirmar un bit dentro del registro de control para indicar que el microprocesador está en el modo de desviación de instrucciones nativas.

10. El método como se expone en la reivindicación 8, en donde dicha integración comprende:

codificar cada una de la pluralidad de instrucciones nativas dentro de un campo de la correspondiente pluralidad de instrucciones de envoltura, en donde cada una de la correspondiente pluralidad de instrucciones de envoltura comprende una macroinstrucción de otra manera válida.

11. El método como se expone en la reivindicación 10, en donde la macroinstrucción de otra manera válida comprende una instrucción de dirección efectiva de carga x86, y en donde el campo comprende un campo de desplazamiento.

12. El método como se expone en la reivindicación 8, que además comprende: tras la detección de un evento de interrupción, afirmar un bit dentro de un registro de banderas y deshabilitar el modo de desviación de instrucciones nativas; y tras volver de un evento de interrupción, evaluar el bit dentro del registro de banderas y volver a habilitar el modo de desviación de instrucciones nativas.

13. El método como se expone en la reivindicación 9, en donde el registro de banderas comprende un registro EFLAGS x86, y donde el bit comprende el bit 31 dentro del registro EFLAGS x86.

Patentes similares o relacionadas:

Microprocesador o microcontrolador potenciado, del 27 de Febrero de 2013, de MICROCHIP TECHNOLOGY INCORPORATED: Un dispositivo de microprocesador de n bits que comprende: una unidad central de procesamiento de n bits (CPU); una pluralidad de registros […]

MICROPROCESADOR CON SELECCIÓN AUTOMÁTICA DE PARALELISMO SIMD, del 9 de Junio de 2011, de QUALCOMM INCORPORATED: Un procedimiento para controlar el paralelismo de operaciones en un procesador de datos en paralelo, que comprende: monitorizar una o más condiciones […]

SISTEMA DE PROCESAMIENTO DE DATOS CON EJECUCION CONDICIONAL DE INSTRUCCIONES COMPUESTAS EXTENDIDAS., del 16 de Diciembre de 2004, de MOTOROLA, INC.: Un sistema para dar órdenes a un procesador de datos, el sistema incluye una raíz de instrucción que tiene un campo de selección de operación para seleccionar […]

SISTEMA INFORMATICO., del , de COMMUNICATE LTD.: EN UN SISTEMA DE ORDENADOR CON UN PROCESADOR RISC QUE UTILIZA INSTRUCCIONES DE 32 BITS, CIERTAS INSTRUCCIONES SE ALMACENAN EN FORMA COMPRIMIDA DE 16 BITS Y SE EXPANDEN […]

MICROPROCESADOR QUE UTILIZA UN CAMPO DE INSTRUCCION PARA ESPECIFICAR FUNCIONALIDAD EXTENDIDA, del 1 de Junio de 1999, de ADVANCED MICRO DEVICES INC.: SE DESCRIBE UN MICROPROCESADOR QUE EXPANDE LA FUNCIONALIDAD O RENDIMIENTO DE UNA ARQUITECTURA IMPLEMENTADA DE MANERA TRANSPARENTE O NO TRANSPARENTE. EL […]

MECANISMO DE FUSIBLE CONFIGURABLE PARA IMPLEMENTAR PARCHES DE MICROCÓDIGOS, del 24 de Enero de 2011, de VIA TECHNOLOGIES, INC.: Un aparato de parches en un microprocesador, que comprende: una pluralidad de bancos de fusibles , configurada para almacenar registros de parches […]

MECANISMO DE FUSIBLE CONFIGURABLE PARA IMPLEMENTAR PARCHES DE MICROCÓDIGOS, del 24 de Enero de 2011, de VIA TECHNOLOGIES, INC.: Un aparato de parches en un microprocesador, que comprende: una pluralidad de bancos de fusibles , configurada para almacenar registros de parches […]

INVALIDACION DE ALMACENAMIENTO, BORRADO DE ELEMENTOS DE LA MEMORIA INTERMEDIA, del 23 de Octubre de 2009, de INTERNATIONAL BUSINESS MACHINES CORPORATION: Un método para invalidar una gama de dos o más elementos de una tabla de traducción de direcciones en un sistema informático que tiene tablas de traducción […]

INVALIDACION DE ALMACENAMIENTO, BORRADO DE ELEMENTOS DE LA MEMORIA INTERMEDIA, del 23 de Octubre de 2009, de INTERNATIONAL BUSINESS MACHINES CORPORATION: Un método para invalidar una gama de dos o más elementos de una tabla de traducción de direcciones en un sistema informático que tiene tablas de traducción […]

TRATAMIENTO DE INSTRUCCIONES DE RESUMEN DE MENSAJE, del 16 de Agosto de 2007, de INTERNATIONAL BUSINESS MACHINES CORPORATION: Un método para ejecutar una instrucción de resumen de mensaje en un sistema de ordenador, comprendiendo la instrucción de resumen de mensaje una función […]

TRATAMIENTO DE INSTRUCCIONES DE RESUMEN DE MENSAJE, del 16 de Agosto de 2007, de INTERNATIONAL BUSINESS MACHINES CORPORATION: Un método para ejecutar una instrucción de resumen de mensaje en un sistema de ordenador, comprendiendo la instrucción de resumen de mensaje una función […]