COMPONENTE DE UNA RED NEURONAL.

Un componente de una red neuronal, comprendiendo el componente una pluralidad de entradas (1),

al menos un elemento procesador (3), al menos una salida (4), y una memoria digital (2) que almacena valores en direcciones respectivamente correspondientes con el al menos un elemento procesador (3), en el cual el al menos un elemento procesador (3) está dispuesto para recibir un valor que comprende una instrucción desde la memoria digital (2) en respuesta a una señal de entrada desde un elemento procesador (3) de un componente adicional de la red neuronal, y obtiene instrucciones del valor que se recibe desde la memoria digital (2) para ejecutar una de entre una pluralidad de operaciones

Tipo: Patente Internacional (Tratado de Cooperación de Patentes). Resumen de patente/invención. Número de Solicitud: PCT/GB00/03957.

Solicitante: THE VICTORIA UNIVERSITY OF MANCHESTER.

Nacionalidad solicitante: Reino Unido.

Dirección: OXFORD ROAD,MANCHESTER M13 9PL.

Inventor/es: FURBER,STEPHEN BYRUN.

Fecha de Publicación: .

Fecha Concesión Europea: 10 de Febrero de 2010.

Clasificación Internacional de Patentes:

- G06N3/063 FISICA. › G06 CALCULO; CONTEO. › G06N SISTEMAS DE COMPUTADORES BASADOS EN MODELOS DE CALCULO ESPECIFICOS. › G06N 3/00 Sistemas de computadores basados en modelos biológicos. › utilizando medios electrónicos.

Clasificación PCT:

- G06N3/063 G06N 3/00 […] › utilizando medios electrónicos.

Clasificación antigua:

- G06N3/063 G06N 3/00 […] › utilizando medios electrónicos.

Fragmento de la descripción:

Componente de una red neuronal.

La presente invención se refiere a un componente de una red neuronal.

Las redes neuronales son arquitecturas de cómputo inspiradas en la biología para procesar información. Cada vez se usan más para resolver problemas que son difíciles de resolver con programas de algoritmos convencionales que se ejecutan en ordenadores convencionales con programas almacenados. Éstos son típicamente problemas de asociación de patrones tales como predicciones del mercado de valores, reconocimiento facial y reconocimiento del habla. Algunas aplicaciones para redes neuronales son comercialmente significativas. Por ejemplo, el touchpad de muchos ordenadores portátiles usa una red neuronal para mejorar la fiabilidad (los sistemas neuronales son relativamente insensibles al ruido).

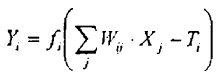

Las neuronas son generalmente dispositivos con entradas múltiples, y una única salida. La fuerza de la señal de salida de una neurona es una función de la suma ponderada de las entradas de dicha neurona y puede representarse mediante la siguiente ecuación:

En donde Xj son las entradas a la neurona (posiblemente desde otras neuronas), Wij son los pesos aplicados a las entradas,

la suma

Un peso asociado a una entrada dada puede ser positivo, en cuyo caso una señal recibida en dicha entrada provocará un aumento del nivel de activación. Un peso positivo puede por lo tanto considerarse como una entrada excitadora. En algunos casos un peso asociado con una entrada dada puede ser negativo, en cuyo caso una señal recibida en dicha entrada provocará una disminución del nivel de activación. Un peso negativo puede considerarse por lo tanto como una entrada inhibidora.

Las conexiones entre las neuronas se refuerzan o se debilitan mediante el ajuste de los valores de los pesos. Por ejemplo, el peso asociado con una entrada concreta de una neurona dada puede aumentarse cada vez que esa entrada recibe una señal. Una señal de entrada recurrente (es decir, una señal recibida varias veces en la misma entrada) aumentará gradualmente el peso asociado con dicha entrada. Una señal recibida en dicha entrada causará por lo tanto un aumento mayor del nivel de activación de la neurona.

La función de activación es normalmente la misma para todas las neuronas y es fija; a menudo se usa una función sigmoidea.

La actividad de la neurona i-ésima en las redes neuronales conocidas está limitada a ser una función monotónica de sus entradas Xi, determinada por los valores de los pesos Wij. Esto restringe la capacidad de las redes neuronales conocidas para emular comportamientos más complejos, y no monotónicos.

La Patente Estadounidense n° 5.278.945 (American Neurological, Inc) describe un aparato procesador neuronal. El aparato procesador neuronal implementa una red neuronal mediante el procesamiento simultáneo de una pluralidad de neuronas usando las mismas entradas sinápticas. Una memoria RAM de pesos externa accede secuencialmente al peso de los datos. Los datos de entrada y los datos de peso pueden configurarse tanto como una única entrada o como una pluralidad de entradas procesadas simultáneamente. El aparato procesador neuronal puede usarse para implementar una red neuronal completa, o puede implementarse usando una pluralidad de dispositivos, implementando cada uno de los dispositivos un número predeterminado de capas neuronales.

Un objetivo de la presente invención es proporcionar un componente de una red neuronal que supere la desventaja mencionada anteriormente.

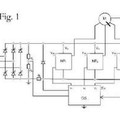

De acuerdo con un primer aspecto de la invención se proporciona un componente de una red neuronal, comprendiendo el componente una pluralidad de entradas, al menos un elemento procesador, al menos una salida, y una memoria digital que almacena valores en unas direcciones respectivamente correspondientes con el al menos un elemento procesador, en el cual el al menos un elemento procesador está dispuesto para recibir un valor que comprende una instrucción desde la memoria digital en respuesta a una señal de entrada desde un elemento procesador de un componente adicional de la red neuronal, y obtiene instrucciones del valor que se recibe desde la memoria digital para ejecutar una de entre una pluralidad de operaciones.

La invención contrasta con las redes neuronales de la técnica anterior, en las que siempre se suma un valor recibido por un elemento procesador a un nivel de activación del elemento procesador (el valor siempre es un peso). El elemento procesador de la invención es capaz de ejecutar una pluralidad de operaciones, y por lo tanto el valor recibido debe actuar como una instrucción para que el elemento procesador elija una de las instrucciones para su ejecución.

El nivel de activación de un elemento procesador es un valor interno indicativo de la excitación de ese elemento procesador.

Convenientemente, la operación es la suma del valor a un nivel de activación del al menos un elemento procesador.

Convenientemente, la operación es una atenuación de un nivel de activación del al menos un elemento procesador hasta cero, mediante el aumento del nivel de activación si es negativo o la disminución del nivel de activación si es positivo.

Convenientemente, la tasa de atenuación es dependiente del valor recibido desde la memoria digital.

Preferiblemente, la atenuación está controlada por un reloj.

Convenientemente, la operación comprende la generación de una salida por el al menos un elemento procesador, y luego la reposición de un nivel de activación del al menos un elemento procesador a un nivel mínimo predeterminado.

Convenientemente, la operación comprende reposicionar un nivel de activación del al menos un elemento procesador a un nivel mínimo predeterminado sin que el al menos un elemento procesador genere una salida.

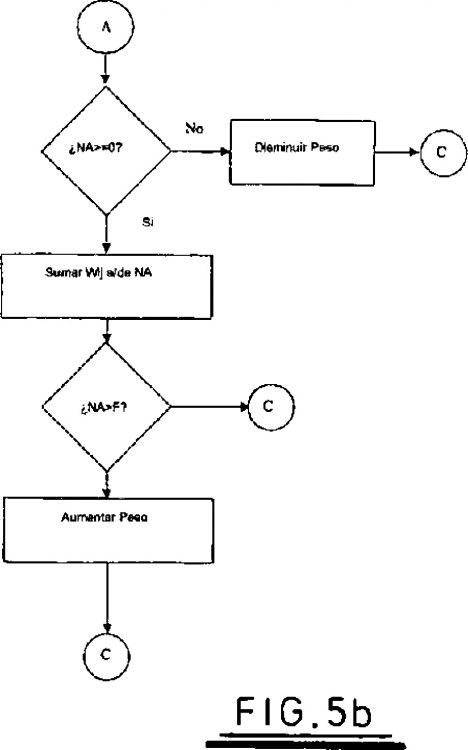

Convenientemente, la operación comprende modificar un nivel de activación del al menos un elemento procesador de acuerdo con un algoritmo de aprendizaje automático.

Convenientemente, la operación comprende modificar el valor retenido en la memoria digital de acuerdo con un algoritmo de aprendizaje automático.

Convenientemente, el algoritmo de aprendizaje automático comprende un algoritmo de aprendizaje de Hebbian.

Convenientemente, la salida generada por el componente de una red neuronal comprende un número representativo de la dirección del elemento procesador desde el cual se emitió la salida.

Convenientemente, el componente de una red neuronal está provisto de unos medios de arbitraje y codificación dispuestos para determinar el orden cronológico de los impulsos de señal recibidos desde los elementos procesadores, y para representar cada impulso de señal como un número. Esto es ventajoso porque supera el problema de restricción de pines en la comunicación off-chip, reemplazando por ejemplo 256 pines, si cada salida neuronal tiene su propio pin, por 8 pines (donde se usa codificación de dirección binaria de 8 bits).

Convenientemente, el componente de una red neuronal comprende adicionalmente un procesador convencional con acceso de lectura/escritura a la memoria digital.

Convenientemente, los accesos del procesador convencional a la memoria digital se someten a arbitraje asíncronamente con los accesos requeridos por los elementos procesadores neuronales.

Convenientemente, un gran número de componentes de una red neuronal son supervisados por una red paralela de procesadores convencionales.

Preferiblemente, la memoria digital es una Memoria de Acceso Aleatorio (RAM).

Convenientemente, el componente funciona de manera asíncrona. Alternativamente, el componente de una red neuronal puede funcionar de manera temporizada.

De acuerdo con un segundo aspecto de la invención se proporciona un procedimiento para operar un componente de una red neuronal, comprendiendo el procedimiento almacenar valores en una memoria digital en direcciones que corresponden...

Reivindicaciones:

1. Un componente de una red neuronal, comprendiendo el componente una pluralidad de entradas (1), al menos un elemento procesador (3), al menos una salida (4), y una memoria digital (2) que almacena valores en direcciones respectivamente correspondientes con el al menos un elemento procesador (3), en el cual el al menos un elemento procesador (3) está dispuesto para recibir un valor que comprende una instrucción desde la memoria digital (2) en respuesta a una señal de entrada desde un elemento procesador (3) de un componente adicional de la red neuronal, y obtiene instrucciones del valor que se recibe desde la memoria digital (2) para ejecutar una de entre una pluralidad de operaciones.

2. Un componente de una red neuronal de acuerdo con la reivindicación 1, en el cual la operación es la suma del valor a un nivel de activación del al menos un elemento procesador (3).

3. Un componente de una red neuronal de acuerdo con la reivindicación 1, en el cual la operación es una atenuación de un nivel de activación del al menos un elemento procesador (3) hasta cero, mediante el aumento del nivel de activación si es negativo o la disminución del nivel de activación si es positivo.

4. Un componente de una red neuronal de acuerdo con la reivindicación 3, en el cual la tasa de atenuación es dependiente del valor recibido desde la memoria digital (2).

5. Un componente de una red neuronal de acuerdo con la reivindicación 3 ó 4, en el cual la atenuación está controlada por un reloj.

6. Un componente de una red neuronal de acuerdo con la reivindicación 1, en el cual la operación comprende la generación de una salida por el al menos un elemento procesador (3), y luego la reposición de un nivel de activación del al menos un elemento procesador (3) a un nivel mínimo predeterminado.

7. Un componente de una red neuronal de acuerdo con la reivindicación 1, en el cual la operación comprende reposicionar un nivel de activación del al menos un elemento procesador (3) a un nivel mínimo predeterminado sin que el al menos un elemento procesador (3) genere una salida.

8. Un componente de una red neuronal de acuerdo con la reivindicación 1, en el cual la operación comprende modificar un nivel de activación del al menos un elemento procesador (3) de acuerdo con un algoritmo de aprendizaje automático.

9. Un componente de una red neuronal de acuerdo con la reivindicación 1 o la Reivindicación 8, en el cual la operación comprende modificar el valor retenido en la memoria digital (2) de acuerdo con un algoritmo de aprendizaje automático.

10. Un componente de una red neuronal de acuerdo con la reivindicación 8 o la Reivindicación 9, en el cual el logaritmo de aprendizaje automático comprende un logaritmo de aprendizaje de Hebbian.

11. Un componente de una red neuronal de acuerdo con cualquier reivindicación precedente, en el cual la salida (4) generada por el componente de una red neuronal comprende un número representativo de la dirección del elemento procesador (3) desde el cual se emitió la salida (4).

12. Un componente de una red neuronal de acuerdo con la reivindicación 11, en el cual el componente de una red neuronal está provisto de unos medios (6) de arbitraje y codificación dispuestos para determinar el orden cronológico de los impulsos de señal recibidos desde los elementos procesadores, y para representar cada impulso de señal como un número.

13. Un componente de una red neuronal de acuerdo con cualquier reivindicación precedente, comprendiendo adicionalmente un procesador convencional con acceso de lectura/escritura a la memoria digital (2).

14. Un componente de una red neuronal de acuerdo con la reivindicación 13, en el cual los accesos del procesador convencional a la memoria digital (2) son sometidos a un arbitraje asíncrono con los accesos requeridos por los elementos procesadores (3) neuronales.

15. Un componente de una red neuronal de acuerdo con las reivindicaciones 13 ó 14, en el cual un gran número de componentes de una red neuronal son supervisados por una red paralela de procesadores convencionales.

16. Un componente de una red neuronal de acuerdo con cualquier reivindicación anterior, en el cual la memoria digital (2) es una Memoria de Acceso Aleatorio (RAM) (2).

17. Un componente de una red neuronal de acuerdo con cualquier reivindicación anterior, en el cual el componente trabaja de manera asíncrona.

18. Un procedimiento para operar un componente de una red neuronal, comprendiendo el procedimiento almacenar valores en una memoria digital (2) en direcciones respectivamente correspondientes a al menos un elemento procesador (3), transfiriendo un valor que comprende una instrucción hasta el al menos un elemento procesador (3) en respuesta a una señal de entrada (1) desde un elemento procesador (3) de un componente adicional de la red neuronal y ejecutando una de entre una pluralidad de operaciones en el elemento procesador (3) en respuesta al valor que se recibe desde la memoria digital (2).

Patentes similares o relacionadas:

Red y método para sistemas informáticos escalables accionados por eventos, del 8 de Julio de 2020, de UNIVERSITAT ZURICH: Una red que comprende una pluralidad de circuitos de núcleo interconectados , en la que cada circuito de núcleo comprende: - una matriz […]

Sistema de red neuronal artificial de tipo asincrónico, del 10 de Julio de 2019, de THE UNIVERSITY OF BATH: Un sistema de red neuronal artificial asíncrono que comprende una pluralidad de neuronas, cada una de las cuales se utiliza para recibir señales de entrada que representan […]

NÚCLEO IP, ARQUITECTURA QUE COMPRENDE UN NÚCLEO IP Y PROCEDIMIENTO DE DISEÑO DE UN NÚCLEO IP, del 31 de Enero de 2019, de UNIVERSIDAD DEL PAÍS VASCO - EUSKAL HERRIKO UNIBERTSITATEA (UPV/EHU): Un núcleo IP configurable y programable de procesamiento para la computación de una pluralidad de productos matriciales, en el que tanto los datos a procesar como los resultados […]

AMPLIFICADOR PARA VARIADOR DE FRECUENCIA, del 25 de Octubre de 2012, de RUANO MOYANO, José: Variador de frecuencia.

La presente invención propone un variador de frecuencia para motor eléctrico. Este variador se caracteriza por el hecho […]

AMPLIFICADOR PARA VARIADOR DE FRECUENCIA, del 25 de Octubre de 2012, de RUANO MOYANO, José: Variador de frecuencia.

La presente invención propone un variador de frecuencia para motor eléctrico. Este variador se caracteriza por el hecho […]

ELEMENTO DE PROCESAMIENTO NEURONAL PAR AUTILIZAR EN UNA RED NEURONAL., del 16 de Junio de 2006, de AXEON LIMITED: Un elemento de tratamiento neural destinado a ser utilizado en una red neural, cuyo elemento de tratamiento comprende: - medios lógicos […]