PROCEDIMIENTO DE ASIGNACION DINAMICA DE MEMORIA POR BLOQUES DE MEMORIA ELEMENTALES EN UNA ESTRUCTURA DE DATOS, Y SISTEMA INTEGRADO CORRESPONDIENTE.

Método de asignación dinámica de memoria en una o varias estructuras de datos (ID_Aj) identificada(s) por un número de identificación y memorizada(s) en forma de paquetes de información numérica en una zona de memoria de un sistema integrado,

la cual está subdividida en bloques de memoria elementales (BL1) y siendo aplicado dicho método de asignación dinámica a partir de al menos una instrucción de borrado (E) de un bloque de memoria elemental y una instrucción de asignación (A) de un bloque memoria elemental, por la cual en dicho bloque de memoria elemental se ha asociado una referencia en tal número de identificación; el método consta de una serie de etapas que consisten en:

para asignar un bloque de memoria elemental:

- atribuir en dicha referencia de dicho número de identificación el valor de dicho número de identificación, y,

para borrar un bloque de memoria elemental:

- atribuir en dicha referencia de dicho número de identificación un valor arbitrario, distinto a cualquier valor de número de identificación

Tipo: Patente Internacional (Tratado de Cooperación de Patentes). Resumen de patente/invención. Número de Solicitud: PCT/FR01/04126.

Solicitante: CP8 TECHNOLOGIES.

Nacionalidad solicitante: Francia.

Dirección: 36-38, RUE DE LA PRINCESSE, B.P. 45,78431 LOUVECIENNES.

Inventor/es: FOUGEROUX,NICOLAS, HAMEAU,PATRICE, LANDIER,OLIVIER.

Fecha de Publicación: .

Fecha Concesión Europea: 14 de Octubre de 2009.

Clasificación Internacional de Patentes:

- G06F12/02D2

Clasificación PCT:

- G06F12/02 FISICA. › G06 CALCULO; CONTEO. › G06F PROCESAMIENTO ELECTRICO DE DATOS DIGITALES (sistemas de computadores basados en modelos de cálculo específicos G06N). › G06F 12/00 Acceso, direccionamiento o asignación en sistemas o arquitecturas de memoria (entrada digital a partir de, o salida digital hacia soportes de registro, p. ej. hacia unidades de almacenamiento de disco G06F 3/06). › Direccionamiento o asignación; Traslado (secuenciación de direcciones de programa G06F 9/00; disposiciones para seleccionar una dirección en una memoria digital G11C 8/00).

Clasificación antigua:

- G06F9/00 G06F […] › Disposiciones para el control por programa, p. ej. unidades de control (control por programa para dispositivos periféricos G06F 13/10).

Fragmento de la descripción:

Procedimiento de asignación dinámica de memoria por bloques de memoria elementales en una estructura de datos, y sistema integrado correspondiente.

El invento se refiere a un método de asignación dinámica de memoria por bloques de memoria elementales en una estructura de datos, en un sistema informático integrado, todavía designado por sistema integrado, y al sistema integrado correspondiente.

Los sistemas integrados, u objetos portátiles actuales, como las tarjetas con microprocesador o de chip, las PCMCIA y los asistentes electrónicos tienden a efectuar funciones cada vez más complejas, especialmente en base a la implantación de programas de aplicación múltiples, siendo las tarjetas con microprocesador o microcontrolador, según el caso, designadas por tarjetas multi aplicación.

Debido a la polivalencia de los actuales lenguajes de alto nivel y de su adaptabilidad a los elementos materiales más variados en la aplicación concreta de máquinas virtuales, las aplicaciones implantadas en este tipo de objeto pueden ser muy diversas. Especialmente, y en el marco de la evolución de las tarjetas electrónicas con microprocesador o microcontrolador, en este tipo de tarjeta se ha previsto la instalación de un número considerable de aplicaciones tales como portamonedas electrónico PME, control de acceso físico, control de acceso a servicios, así como emisiones televisadas de pago o análogos.

La instalación de múltiples aplicaciones en estos objetos portátiles es posible, por un lado, debido a la miniaturización de los circuitos electrónicos y al aumento continuado de la capacidad de memoria de las tarjetas chip y, por otro lado, debido al incremento de la potencia de cálculo de las unidades centrales de tratamiento.

La añadidura de las aplicaciones instaladas en estos tipos de materiales plantea, no obstante, el inconveniente principal de una asignación dinámica de memoria optimizada.

Efectivamente, como se muestra en la figura 1, se recuerda que el objeto portátil, formado p. ej. de una tarjeta con micro procesador de referencia 10, habitualmente comprende los circuitos de entrada/salida, I/O, referencias 12, de las fuentes de tratamiento de información, referencia 14, formadas por un microcontrolador y unidos a los circuitos de entrada/salida 12. Asimismo, se prevé una memoria no volátil 18 formada por una memoria programable 18a y una memoria de tipo ROM, o memoria de tipo de acceso solo lectura 18b. Estas memorias están vinculadas al microcontrolador o microprocesador 14. Por último, también se ha previsto una memoria de trabajo, memoria RAM, referencia 16, vinculada al microprocesador. Se entiende que dichas conexiones o vínculos son enlaces por BUS.

El conjunto es administrado por un sistema de explotación OS, el cual puede implantarse en memoria no volátil 18. Igualmente, en determinados casos, el objeto portátil multiaplicación puede comportar una unidad de cálculo criptográfico SI, referencia 20, unida por sí misma al microprocesador 14.

El propio microprocesador puede reemplazarse o completarse por los circuitos lógicos implantados en un chip de semiconducción, pudiendo ser esos circuitos lógicos, circuitos de tipo ASIC (del inglés: Application Specific Integrated Circuit.)

En la patente WO 01/16759, registrada previamente a la presente demanda pero publicada a posteriori, se describe un método de asignación de memoria dividida en bloques de datos en una tarjeta chip.

El documento EP-A-0 686 918 describe una técnica de atribución, verificación y liberación de objeto que se considera muy cercana al invento.

El invento está definido en el repertorio adjunto de reivindicaciones.

En el marco de racionalización de la gestión del espacio de memoria disponible en todo el sistema informático, en concreto para un sistema integrado como una tarjeta con microprocesador o microcontrolador, como representado en el figura 1, el invento tiene por objeto la aplicación de un método de asignación dinámica de memoria por bloques de memoria elementales en una estructura de datos; dichas estructuras de datos corresponden ya sea a las aplicaciones como tal, ya sea a los datos del sistema que permiten la aplicación del sistema de explotación, o incluso de los datos específicos de seguridad, como las claves de acceso de cifrado/descifrado u otros. La noción de asignación dinámica recupera la atribución y/o la supresión de memoria atribuida.

Otro objetivo del invento, en el marco de la racionalización comentada, es igualmente el acceso más rápido al conocimiento de la pertenencia de cada octeto memorizado en zona memoria en la aplicación o estructura de datos a la que pertenece dicho octeto.

Otro objetivo del presente invento es también la disposición de un método dinámico de memoria por bloques de memoria elementales en una estructura de datos que permite evitar o minimizar cualquier fenómeno de diseminación, todavía designado fenómeno de fragmentación, durante el proceso de asignación/borrado de la memoria.

Otro objeto del presente invento es, finalmente, la aplicación de un método de asignación dinámica de memoria por bloques de memoria elementales en el cual la integridad de la memoria está asegurada por una verificación del valor de cada bloque de memoria elemental asignado.

El método de asignación dinámico de memoria en una estructura de datos identificado por un número de identificación y memorizado en formato de paquetes de información numérica en la zona de memoria de un sistema integrado, objeto del presente invento, prevé que, al estar la zona de memoria subdividida en bloques de memoria elementales, este sea aplicado a partir de, al memos, una instrucción de borrado de un bloque de memoria elemental y una instrucción de asignación de un bloque de memoria elemental, por la cual este bloque de memoria elemental está asociado a una referencia de este número de identificación. Para asignar un bloque de memoria elemental, este proceso consiste en atribuir en la referencia del número de identificación el valor de este número de identificación. Para designar un bloque de memoria elemental, el proceso consiste en atribuir en la referencia del número de identificación el valor de este número de identificación. Para borrar un bloque de memoria elemental, este proceso consiste en atribuir un valor arbitrario establecido a priori, distinto de cualquier valor de número de identificación.

Un sistema integrado multiaplicación, objeto del presente invento, comporta un sistema de explotación que asegure la gestión de los circuitos de entrada/salida, de la memoria viva y de la memoria no volátil mediante un microprocesador. Según la reivindicación 2, puede incluir en memoria no volátil una tabla de gestión de la zona memoria por bloques de memoria elementales, incluyendo dicha tabla, al menos, por cada bloque de memoria elemental, una referencia a un número de identificación de la estructura de datos en la cual el bloque de memoria elemental correspondiente ha sido asignado y un valor de espacio de memoria ocupado en el bloque de memoria elemental asignado correspondiente.

El proceso objeto del invento es aplicable en la asignación dinámica de memoria de cualquier sistema informático integrado, más concretamente de cualquier objeto portátil como una tarjeta de micro procesador o micro controlador, en el cual las fuentes de memoria son reducidas, en razón de la medida y el volumen limitados de este último.

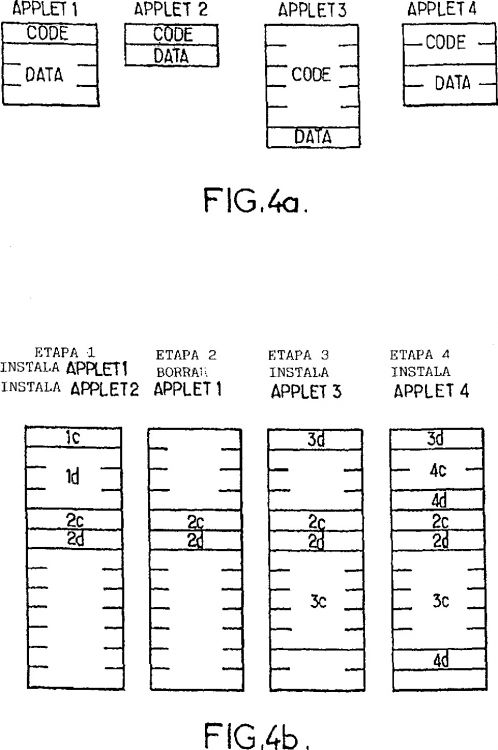

El proceso y el sistema integrado multi aplicación objetos del invento se entienden mejor tras efectuar una lectura de la descripción y los dibujos indicados a continuación en los cuales, además de la figura 1 referente al asunto anterior:

- la figura 2 representa un organigrama funcional ilustrativo de las etapas que permiten la aplicación del proceso de asignación dinámica de memoria objeto del presente invento;

- la figura 2b representa, a título informativo, un organigrama funcional de una variante preferencial de aplicación del proceso de asignación dinámica de memoria, objeto del presente invento, como ilustrado en la figura 2;

- la figura 2c representa, a título informativo, un modo de realización concreto del proceso de cálculo de un valor de verificación (checksum);

- la figura 3 representa, a título ilustrativo, una variante preferencial de aplicación del procedimiento objeto del presente invento, en el caso de una operación de borrado de una estructura de datos, como una aplicación;

Reivindicaciones:

1. Método de asignación dinámica de memoria en una o varias estructuras de datos (ID_Aj) identificada(s) por un número de identificación y memorizada(s) en forma de paquetes de información numérica en una zona de memoria de un sistema integrado, la cual está subdividida en bloques de memoria elementales (BL1) y siendo aplicado dicho método de asignación dinámica a partir de al menos una instrucción de borrado (E) de un bloque de memoria elemental y una instrucción de asignación (A) de un bloque memoria elemental, por la cual en dicho bloque de memoria elemental se ha asociado una referencia en tal número de identificación; el método consta de una serie de etapas que consisten en:

para asignar un bloque de memoria elemental:

- atribuir en dicha referencia de dicho número de identificación el valor de dicho número de identificación, y,

para borrar un bloque de memoria elemental:

- atribuir en dicha referencia de dicho número de identificación un valor arbitrario, distinto a cualquier valor de número de identificación.

2. Método según la reivindicación 1, por el cual, para asignar un bloque de memoria elemental, este está formado además, y anteriormente a la etapa que consiste en atribuir en susodicha referencia de dicho número de identificación el valor de dicho número de identificación, para cualquier bloque de memoria elemental asignado, de las etapas que consisten en:

- comprobar (A1) la identidad de dicha referencia en dicho número de identificación y de dicho número de de identificación, y en caso de resultado positivo de esta comprobación de identidad, susodicho bloque de memoria elemental corriente está al menos parcialmente asignado a esta estructura de datos,

- verificar (A2) que existe espacio de memoria suficiente de dicho bloque de memoria elemental corriente, para memorizar dicha información numérica; y llamar una instrucción de asignación de un bloque de memoria elemental siguiente, en caso contrario.

3. Método según la reivindicación 1 o 2, mediante el cual, para borrar una estructura de datos identificada por un número de identificación (ID_Ae), se trata de atribuir el valor arbitrario (AAAA), antes comentado, en dicha referencia de dicho número de identificación del conjunto de los bloques de memoria elementales asignados a esta estructura de datos.

4. Método según la reivindicación a, en el cual, después de la asignación de un bloque de memoria elemental en una estructura de datos y después de la memorización por escritura de dicha información numérica en dicho bloque de memoria elemental asignado, consiste además en calcular un valor de verificación (CKS) del bloque de memoria elemental.

5. Método según la reivindicación 1, en el cual, independientemente de cualquier asignación de un bloque de memoria elevental en una estructura de datos, este comprende además las etapas que consisten en:

- seleccionar (A51), según un criterio de selección aleatorio, uno de los bloques de memoria elemental asignado, y

- calcular (A53) un valor de verificación (CKS(X)) de dicho bloque de memoria elemental asignado.

6. Método según la reivindicación 5, en el cual, dicha selección seguida de dicho cálculo de un valor de verificación ambos son activados periódicamente, con un periodo de valor determinado.

7. Sistema integrado formado por una zona memoria asignada de manera dinámica a una o varias estructuras de datos (ID_Aj) identificadas por un número de identificación y memorizadas en forma de paquetes de información numérica, estando dicha zona de memoria subdividida en bloques de memorias elementales (BL1), y habiendo asociado a cada bloque una referencia a dicho número de identificación, la cual (referencia) posee:

el valor de dicho número de identificación cuando el bloque de memoria elemental está asignado,

un valor arbitrario, distinto a cualquier valor de número de identificación, cuando el bloque de memoria elemental sea borrado.

8. Sistema integrado según reivindicación 7, caracterizado por el hecho de que en memoria programable no volátil (18a) comporta una tabla de gestión de la zona memoria por bloques de memoria elementales; y dicha tabla consta de, al menos para cada bloque de memoria elemental:

- una referencia a un número de identificación de una estructura de datos (ID_Ai) en la cual el bloque de memoria elemental correspondiente ha sido asignado;

- un valor de espacio de memoria ocupado (Lli) en dicho bloque de memoria elemental correspondiente asignado.

9. Sistema integrado según reivindicación 7, en el cual dicha tabla comporta además para cada bloque de memoria elemental, un valor de verificación (CKS1a a CKS2b) del correspondiente bloque de memoria elemental asignado.

Patentes similares o relacionadas:

SISTEMA DE GESTION DE MEMORIA PARA LA REDUCCION DE LA FRAGMENTACION DE MEMORIA, del 3 de Febrero de 2010, de INFOVISTA SA: Sistema de gestión de memoria de un proceso elaborado en lenguaje C/C++ en una unidad de tratamiento, comprendiendo este sistema: un asignador apropiado para asignar […]

SISTEMA DE GESTION DE MEMORIA PARA LA REDUCCION DE LA FRAGMENTACION DE MEMORIA, del 3 de Febrero de 2010, de INFOVISTA SA: Sistema de gestión de memoria de un proceso elaborado en lenguaje C/C++ en una unidad de tratamiento, comprendiendo este sistema: un asignador apropiado para asignar […]

Almacenamiento de datos gráficos comprimidos en ancho de banda, del 6 de Noviembre de 2019, de QUALCOMM INCORPORATED: Un procedimiento, que comprende: almacenar, mediante al menos un procesador, una pluralidad de datos gráficos comprimidos en ancho de banda en una pluralidad respectiva […]

Método de procesado de datos, aparato de almacenamiento, disco de estado sólido y sistema de almacenamiento, del 28 de Agosto de 2019, de HUAWEI TECHNOLOGIES CO., LTD.: Un método de procesado de datos, aplicado a un sistema de almacenamiento, en donde el sistema de almacenamiento comprende un anfitrión, un controlador y un […]

Gestión de memoria automática que usa una unidad de gestión de memoria, del 24 de Julio de 2019, de aicas GmbH: Método implementado por ordenador , para actuar sobre un módulo automático de gestión de memoria en un sistema informático que tiene una memoria de acceso […]

Uso de compresión de memoria para reducir la carga de compromiso de memoria, del 6 de Mayo de 2019, de Microsoft Technology Licensing, LLC: Un método de reducir una cantidad de compromiso de memoria para un programa en un dispositivo de cálculo , comprendiendo el método: determinar […]

Controlador de acceso a memoria, sistemas y procedimientos para optimizar los tiempos de acceso a memoria, del 9 de Enero de 2019, de QUALCOMM INCORPORATED: Un controlador de memoria , que comprende: un controlador configurado para acceder al menos a una ubicación de memoria correspondiente […]

Sistema de gestión de datos y método, del 30 de Noviembre de 2018, de LIFESCAN SCOTLAND LIMITED: Un sistema de gestión de datos que comprende: - una primera sección de memoria no volátil dividida en una pluralidad de ubicaciones […]

Método de obtención anticipada de datos para un sistema de almacenamiento de tabla hash distribuida DHT, nodo y sistema, del 21 de Noviembre de 2018, de HUAWEI TECHNOLOGIES CO., LTD.: Un método de obtención anticipada de datos para un sistema de almacenamiento de tabla hash distribuida DHT que comprende un primer nodo de almacenamiento y un segundo […]