Iniciación de ataques en componentes de tarjeta inteligente.

Sistema (21) de iniciación de ataques en un componente (30) de tarjeta inteligente (24),

que comprende un dispositivo informático (22), un lector (23) de tarjeta inteligente y un dispositivo de análisis (25), estando el lector (23) configurado para transmitir órdenes procedentes del dispositivo informático (22) hacia una tarjeta inteligente (24), estando el dispositivo de análisis (25) configurado para pasar de un estado desactivado a un estado activado en respuesta a la recepción de un mensaje de activación (M2) y, cuando está en su estado activado, para detectar un evento predeterminado en una señal de análisis (SA) procedente de una tarjeta inteligente (24) y para enviar una señal de iniciación (D) en respuesta a la detección de dicho evento, caracterizado porque el dispositivo de análisis (25) es un detector de motivo configurado para detectar dicho evento por digitalización de la señal de análisis (SA) en n bits, siendo n superior o igual a 3, y comparación de una porción de m muestras de la señal de análisis digitalizada, siendo m superior o igual a 3, con una señal de referencia.

Tipo: Patente Europea. Resumen de patente/invención. Número de Solicitud: E12180652.

Solicitante: OBERTHUR TECHNOLOGIES.

Nacionalidad solicitante: Francia.

Dirección: 50, QUAI MICHELET 92300 LEVALLOIS-PERRET FRANCIA.

Inventor/es: GIRAUD, CHRISTOPHE, MORIN,NICOLAS.

Fecha de Publicación: .

Clasificación Internacional de Patentes:

- G01R31/317 FISICA. › G01 METROLOGIA; ENSAYOS. › G01R MEDIDA DE VARIABLES ELECTRICAS; MEDIDA DE VARIABLES MAGNETICAS (indicación de la sintonización de circuitos resonantes H03J 3/12). › G01R 31/00 Dispositivos para ensayo de propiedades eléctricas; Dispositivos para la localización de fallos eléctricos; Disposiciones para el ensayo eléctrico caracterizadas por lo que se está ensayando, no previstos en otro lugar (ensayo o medida de dispositivos semiconductores o de estado sólido, durante la fabricación H01L 21/66; ensayo de los sistemas de transmisión por líneas H04B 3/46). › Ensayo de circuitos digitales.

PDF original: ES-2529722_T3.pdf

Fragmento de la descripción:

Iniciación de ataques en componentes de tarjeta inteligente Antecedentes de la invención

La invención se refiere al ámbito de los componentes seguros de tarjeta inteligente, o tarjeta de circuito integrado.

Para asegurar el funcionamiento de un componente de tarjeta inteligente, por ejemplo un microcontrolador, los constructores aplican pestillos de seguridad implantados en el código del componente.

Un ataque por inyección de fallo consiste en perturbar el componente para desviarlo de su comportamiento normal e intentar de este modo hacer "saltar" sus pestillos de seguridad. Tal ataque por inyección de fallo es por ejemplo realizada enviando un impulso luminoso al componente de tarjeta inteligente en un instante correspondiente a la ejecución de una instrucción determinada.

TOSHINORI FUKUNAGA ET ÁL.: "Practical Fault Attack on a Cryptographie LSI with ISO/IEC 18033-3 Block Ciphers" (FAULT DIAGNOSIS AND TOLERANCE IN CRYPTOGRAPHY (FDTC), 2009 WORKSHOP ON, IEEE, PISCATAWAY, NJ, USA, 6 septiembre 2009, páginas 84-92, ISBN: 978-1-4244-4972-9) describe un procedimiento de iniciación de ataques en un circuito criptográfico.

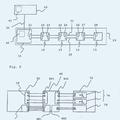

Para poner a prueba la seguridad de sus tarjetas inteligentes frente a tales ataques, un constructor de tarjetas inteligentes puede verse obligado a realizar él mismo ataques o a hacer que un tercero realice ataques, por ejemplo un organismo de certificación. La figura 1 representa un sistema de iniciación de ataques que se puede utilizar para realizar ataques por un constructor de tarjeta inteligente o un organismo de certificación.

El sistema 1 de la figura 1 comprende un ordenador 2, un lector 3 de tarjeta inteligente, una tarjeta inteligente 4, un osciloscopio 5 y un emisor láser 6.

El ordenador 2 está conectado al lector 3 por una conexión 7, por ejemplo un cable USB. El ordenador 2 puede enviar órdenes hacia el lector 3, por la conexión 7. El lector 3 es capaz de comunicarse con la tarjeta inteligente 4 por una conexión 8, por ejemplo conforme a la norma IS07816. Cuando recibe una orden del ordenador 2, el lector 3 transmite la orden recibida a la tarjeta inteligente 4. La tarjeta inteligente 4 comprende componentes electrónicos, especialmente un microcontrolador 10 configurado para ejecutar instrucciones predeterminadas en respuesta a la recepción de una orden.

El ordenador 2 está asimismo conectado al osciloscopio 5 por una conexión 9, por ejemplo una conexión GPIB (por «Genera/ Purpose Interface Bus»), que permite al ordenador enviar mensajes al osciloscopio 5, especialmente un mensaje que solicita al osciloscopio 5 pasar de un estado desarmado a un estado armado. El osciloscopio 5 está conectado al emisor láser 6 por una conexión 11.

Se ha demostrado que las interacciones físicas de un módulo electrónico embarcado, por ejemplo un módulo de microcontrolador de tarjeta inteligente, con su entorno exterior son dependientes de las operaciones efectuadas por el módulo así como de los valores de las variables manipuladas por estas operaciones. Ejemplos de tales interacciones son el consumo de corriente del módulo (señal PA), la radiación electromagnética (señal EMA) o bien la señal de radiofrecuencia (señal RFA) que permite a una tarjeta sin contacto alimentarse y comunicarse.

De este modo, en la figura 1, se denomina SA la señal de análisis medida para analizar las operaciones efectuadas por el microcontrolador 10. La señal de análisis SA puede ser por ejemplo el consumo de corriente, la radiación electromagnética o la señal de radiofrecuencia de la tarjeta inteligente 4. La señal SA es proporcionada al osciloscopio 5.

Cuando está armado, el osciloscopio 5 está configurado para detectar un evento particular en la señal de análisis SA y para enviar una señal de iniciación D hacia el emisor láser 6 en respuesta a la detección del evento particular. El evento particular es por ejemplo un pico de amplitud de la señal SA, que corresponde a un pico de consumo de corriente durante la ejecución, por el microcontrolador 10, de una instrucción que implica la transmisión de una variable en un bus.

La figura 2 representa la iniciación de un ataque en el sistema 1 de la figura 1, en función del tiempo.

Inicialmente, el osciloscopio 5 está desarmado y no efectúa ningún análisis de la señal SA. Cada orden emitida por el ordenador 2 es transmitida a la tarjeta inteligente 4 por el lector 3. La tarjeta inteligente 4 ejecuta las instrucciones que corresponden a las órdenes recibidas.

A continuación, antes del envío de una orden de atacar, el ordenador 2 envía un mensaje M de armado al osciloscopio 5 (en la etapa E1). En respuesta a la recepción del mensaje M, el osciloscopio 5 se arma (etapa E2), lo

cual requiere una duración AT de aproximadamente 200 ms. Cuando está armado, el osciloscopio 5 analiza permanentemente la señal de análisis SA para detectar un evento particular en la señal de análisis SA (etapa E6).

Después de transcurrir la duración AT, el ordenador 2 envía una orden CMD al lector 3 (etapa E3) y el lector 3 transmite la orden CMD a la tarjeta inteligente 4. En respuesta a la recepción de la orden CMD, el microcontrolador 10 de la tarjeta inteligente 4 ejecuta instrucciones predeterminadas correspondientes a la orden CMD (etapa E5).

La orden CMD es una orden cuya ejecución comprende una instrucción de atacar. De este modo, durante la etapa E5, una instrucción determinada genera el evento particular en la señal de análisis SA (etapa E5a). Este evento es detectado por el osciloscopio 5 (etapa E6a) que envía entonces la señal de iniciación D al emisor láser 6.

En respuesta a la recepción de la señal de iniciación D, el emisor láser 6 envía un impulso luminoso a la tarjeta inteligente 4 (etapa E7).

El sistema de la figura 1 permite entonces, durante la ejecución de instrucciones en respuesta a la recepción de una orden, iniciar un ataque en un instante preciso que corresponde a la ejecución de una instrucción predeterminada. La orden atacada es determinada por el ordenador 2 que arma el osciloscopio 5 antes del envío de la orden enviando el mensaje M de armado.

El sistema 1 de la figura 1 presenta sin embargo inconvenientes. En efecto, el armado del osciloscopio (etapa E2) necesita un tiempo AT relativamente importante, típicamente del orden de 200 ms a comparar con aproximadamente 30 ms para la ejecución de una orden (etapa E5). El número de ataques que es posible iniciar en un tiempo determinado es por lo tanto limitado. Además, un osciloscopio 5 es un equipo costoso.

Por lo tanto existe una necesidad de una solución que permita iniciar ataques de manera más eficaz y menos costosa.

El sistema 1 de la figura 1 se ha descrito para facilitar la comprensión de la invención y de sus ventajas. Sin embargo, no se ha de deducir que el sistema 1 forma parte de la técnica.

Objeto y sumario de la invención

La presente invención propone un sistema de iniciación de ataques en un componente de tarjeta inteligente, que comprende un dispositivo informático, un lector de tarjeta inteligente y un dispositivo de análisis, estando el lector configurado para transmitir órdenes procedentes del dispositivo informático hacia una tarjeta inteligente, estando el dispositivo de análisis configurado para pasar de un estado desactivado a un estado activado en respuesta a la recepción de un mensaje de activación y, cuando está en su estado activado, para detectar un evento predeterminado en una señal de análisis procedente de una tarjeta inteligente y para enviar una señal de iniciación en respuesta a la detección de dicho evento.

Este sistema se caracteriza porque el dispositivo de análisis es un detector de motivo configurado para detectar dicho evento por digitalización de la señal de análisis sobre n bits, siendo n superior o igual a 3, y comparación de una porción de m muestras de la señal de análisis digitalizada, siendo m superior o igual a 3, con una señal de referencia.

Preferiblemente, el lector está configurado para enviar dicho mensaje de activación hacia dicho dispositivo de análisis en respuesta a la recepción de una orden determinada.

Correlativamente, la invención propone un procedimiento de iniciación de ataques en un componente de tarjeta inteligente, que comprende:

- una etapa de transmisión, por un lector de tarjeta inteligente, de órdenes procedentes de un dispositivo informático hacia una tarjeta inteligente,

- una etapa de paso, por un dispositivo de análisis, de un estado desactivado a un estado activado en respuesta a la recepción de un mensaje de activación,

- una etapa de detección, por el dispositivo de análisis en el estado activado,... [Seguir leyendo]

Reivindicaciones:

1. Sistema (21) de iniciación de ataques en un componente (30) de tarjeta inteligente (24), que comprende un dispositivo informático (22), un lector (23) de tarjeta inteligente y un dispositivo de análisis (25), estando el lector (23) configurado para transmitir órdenes procedentes del dispositivo informático (22) hacia una tarjeta inteligente (24), estando el dispositivo de análisis (25) configurado para pasar de un estado desactivado a un estado activado en respuesta a la recepción de un mensaje de activación (M2) y, cuando está en su estado activado, para detectar un evento predeterminado en una señal de análisis (SA) procedente de una tarjeta inteligente (24) y para enviar una señal de iniciación (D) en respuesta a la detección de dicho evento, caracterizado porque el dispositivo de análisis (25) es un detector de motivo configurado para detectar dicho evento por digitalización de la señal de análisis (SA) en n bits, siendo n superior o igual a 3, y comparación de una porción de m muestras de la señal de análisis digitalizada, siendo m superior o igual a 3, con una señal de referencia.

2. Sistema (21) de iniciación según la reivindicación 1, en el que el lector (23) está configurado para enviar dicho mensaje de activación (M2) hacia dicho dispositivo de análisis (25) en respuesta a la recepción de una orden (CMD) determinada.

3. Sistema (21) de iniciación de ataques según la reivindicación 2, en el que el lector (23) está configurado para memorizar una información que designa una orden en respuesta a un mensaje (M1) procedente del dispositivo informático (22), y para enviar dicho mensaje de activación (M2) hacia dicho dispositivo de análisis (25) en respuesta a la recepción de la orden (CMD) designada por la información memorizada.

4. Sistema (21) de iniciación de ataques según la reivindicación 3, en el que dicha información es una variable (ET) que puede adoptar un valor activado y un valor desactivado, estando el lector (23) configurado para activar dicha variable en respuesta a la recepción del mensaje (M1) procedente del dispositivo informático (22) y para enviar dicho mensaje de activación (M2) hacia dicho dispositivo de análisis (25) en respuesta a la recepción de una orden (CMD) cuando la variable (ET) está activada.

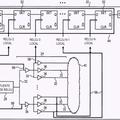

5. Sistema (21) de iniciación de ataques según una de las reivindicaciones 1 a 4, en el que el dispositivo de análisis (25) comprende un convertidor analógico/digital (32) capaz de digitalizar la señal de análisis (SA) sobre n bits, una memoria intermedia (34) configurada para memorizar una porción de m muestras de la señal de análisis digitalizada, una otra memoria (35) que memoriza un motivo de referencia y una unidad de comparación (36, 37) configurada para comparar la porción de la señal de análisis memorizada por la memoria intermedia (34) con dicho motivo de referencia.

6. Sistema (21) de iniciación de ataques según la reivindicación 5, en el que la unidad de comparación está configurada para determinar un grado de similitud entre la porción de la señal de análisis memorizada por la memoria intermedia (34) y dicho motivo de referencia utilizando un algoritmo de intercorrelación.

7. Sistema (21) de iniciación de ataques según la reivindicación 6, en el que el dispositivo de análisis comprende además otra una unidad de transformación configurada para efectuar una transformación de Fourrierde la señal de análisis digitalizada.

8. Sistema (21) de iniciación de ataques según una de las reivindicaciones 5 a 7, en el que la memoria intermedia (34), dicha otra memoria (35) y la unidad de comparación (36, 37) están incluidas en un circuito lógico programable

(33).

9. Sistema (21) de iniciación de ataques según una de las reivindicaciones 5 a 7, en el que la memoria intermedia

(34) , dicha otra memoria (35) y la unidad de comparación (36, 37) están incluidas en un procesador de señales digital.

10. Sistema (21) de iniciación de ataques según una de las reivindicaciones 1 a 9, que comprende además otro un emisor (26) capaz de enviar un impulso luminoso hacia una tarjeta inteligente (24) conectada al lector (23) en respuesta a la recepción de la señal de iniciación (D).

11. Procedimiento de iniciación de ataques en un componente (30) de tarjeta inteligente (24), que comprende:

- una etapa de transmisión, por un lector (23) de tarjeta inteligente, de órdenes procedentes de un dispositivo informático (22) hacia una tarjeta inteligente (24),

- una etapa de paso, por un dispositivo de análisis (25), de un estado desactivado a un estado activado en respuesta a la recepción de un mensaje de activación (M2),

- una etapa (S8a) de detección, por el dispositivo de análisis (25) en el estado activado, de un evento predeterminado en una señal de análisis (SA) procedente de una tarjeta inteligente (24), y

- una etapa de envío, por el dispositivo de análisis (25), de una señal de iniciación (D) en respuesta a la detección de dicho evento;

caracterizado porque la etapa de detección de dicho evento comprende la digitalización de la señal de análisis sobre 5 n bits, siendo n superior o igual a 3, y la comparación de una porción de m muestras de la señal de análisis digitalizada, siendo m superior o igual a 3, con una señal de referencia.

Patentes similares o relacionadas:

Circuito integrado digital protegido contra errores transitorios, del 9 de Octubre de 2019, de THALES: Circuito integrado digital que comprende un conjunto lógico que comprende un bloque lógico funcional, una unidad lógica de detección […]

Procedimiento de prueba de circuitos de criptografía, circuito de criptografía asegurado adecuado para ser probado y procedimiento de cableado de tal circuito, del 27 de Marzo de 2019, de Institut Mines-Telecom: Procedimiento de prueba de un circuito de criptografía que integra un secreto y que consta de registros y de puertas (10, 211, 212, […]

Dispositivo de medición de posición y método para verificar una señal de ciclo de trabajo, del 13 de Febrero de 2019, de DR. JOHANNES HEIDENHAIN GMBH: Dispositivo de medición de posición que comprende una unidad de detección de posición , una unidad de procesamiento , una unidad de interfaz […]

Medición eficiente del ruido de la fuente de alimentación basada en la incertidumbre de temporización, del 16 de Enero de 2019, de TELEFONAKTIEBOLAGET LM ERICSSON (PUBL): Un circuito integrado que comprende un dispositivo de medición de ruido de la fuente de alimentación, el circuito integrado que tiene un bloque funcional, comprendiendo […]

Método de protección para información de datos relativos a un dispositivo electrónico y su circuito de protección, del 25 de Abril de 2018, de Shenzhen Xinguodu Technology Co. Ltd: Un circuito para proteger información de datos de un equipo electrónico, que comprende un procesador y un dispositivo electrónico conectado con el procesador […]

Procedimiento para la prueba funcional de una unidad receptora PS15 de un aparato de mando de automóvil y unidad receptora PS15 correspondiente, del 26 de Octubre de 2016, de CONTINENTAL AUTOMOTIVE GMBH: Procedimiento para la verificación funcional de una unidad receptora PSI5 de un aparato de mando de automóvil, en donde la unidad receptora […]

Dispositivo de protección contra fallas en circuitos de árbol de reloj, del 10 de Febrero de 2016, de Winbond Electronics Corp: Un circuito integrado "CI", que comprende:

Un circuito de árbol de reloj configurado para distribuir una señal de reloj en el circuito […]

Dispositivo de protección contra fallas en circuitos de árbol de reloj, del 10 de Febrero de 2016, de Winbond Electronics Corp: Un circuito integrado "CI", que comprende:

Un circuito de árbol de reloj configurado para distribuir una señal de reloj en el circuito […]

Procedimiento, componente electrónico y sistema para diagnosticar enlaces de comunicación, del 6 de Enero de 2016, de PHOENIX CONTACT GMBH & CO. KG: Procedimiento para diagnosticar enlaces de comunicación en un sistema de comunicación , que incluye las etapas

a) aportación de una pluralidad de unidades […]

Procedimiento, componente electrónico y sistema para diagnosticar enlaces de comunicación, del 6 de Enero de 2016, de PHOENIX CONTACT GMBH & CO. KG: Procedimiento para diagnosticar enlaces de comunicación en un sistema de comunicación , que incluye las etapas

a) aportación de una pluralidad de unidades […]