Circuito integrado de silicio que incluye una función físicamente no reproducible, procedimiento y sistema de test de dicho circuito.

Circuito integrado de silicio que incluye una función físicamente no reproducible LPUF que permite la generación de una firma propia a dicho circuito,

estando dicha función caracterizada porque incluye:

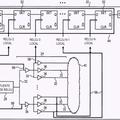

- un oscilador en anillo compuesto por un bucle (502) recorrido por una señal e, estando formado dicho bucle por N cadenas de retardo (500, 501) topológicamente idénticas, conectadas en serie entre ellas, y una compuerta de inversión (503), estando compuesta una cadena de retardo (500, 501) por M elementos de retardo (506, 507) conectados en serie entre ellos;

- un módulo de control (505) que genera N palabras de control (C1, C2), estando utilizadas dichas palabras para configurar el valor del los retardos introducidos por las cadenas de retardo en la señal e que les recorre;

- un módulo de medición (504) que mide la frecuencia de la señal a la salida de la última cadena de retardo (501) tras la actualización de las palabras de control;

- medios para deducir de las medidas de frecuencia los bits que componen la firma del circuito.

Tipo: Patente Internacional (Tratado de Cooperación de Patentes). Resumen de patente/invención. Número de Solicitud: PCT/EP2011/050234.

Solicitante: Institut Telecom - Telecom Paris Tech.

Inventor/es: DANGER,Jean-Luc.

Fecha de Publicación: .

Clasificación Internacional de Patentes:

- G01R31/317 FISICA. › G01 METROLOGIA; ENSAYOS. › G01R MEDIDA DE VARIABLES ELECTRICAS; MEDIDA DE VARIABLES MAGNETICAS (indicación de la sintonización de circuitos resonantes H03J 3/12). › G01R 31/00 Dispositivos para ensayo de propiedades eléctricas; Dispositivos para la localización de fallos eléctricos; Disposiciones para el ensayo eléctrico caracterizadas por lo que se está ensayando, no previstos en otro lugar (ensayo o medida de dispositivos semiconductores o de estado sólido, durante la fabricación H01L 21/66; ensayo de los sistemas de transmisión por líneas H04B 3/46). › Ensayo de circuitos digitales.

- G06F21/31 G […] › G06 CALCULO; CONTEO. › G06F PROCESAMIENTO ELECTRICO DE DATOS DIGITALES (sistemas de computadores basados en modelos de cálculo específicos G06N). › G06F 21/00 Disposiciones de seguridad para la protección de computadores, sus componentes, programas o datos contra actividades no autorizadas. › autenticación del usuario.

- G06F21/73 G06F 21/00 […] › mediante la creación o la determinación de identificación de hardware, p. ej.: números de serie.

PDF original: ES-2502442_T3.pdf

Fragmento de la descripción:

Circuito integrado de silicio que incluye una función físicamente no reproducible, procedimiento y sistema de test de dicho circuito [0001] La invención hace referencia a un circuito integrado de silicio que incluye una función físicamente no 5 reproducible y un procedimiento de selección mediante un test de fiabilidad de dicho circuito. Se aplica, especialmente, en el campo de los circuitos de criptografía y autentificación de componentes electrónicos.

Para numerosas aplicaciones, resulta útil poder identificar de manera precisa un chip electrónico o un circuito integrado. En la técnica anterior se propusieron soluciones que permiten, especialmente, distinguir un circuito dado de entre una serie de circuitos procedentes de la misma cadena de producción. De este modo,

incorporar en un circuito integrado una función físicamente no reproducible de tipo PUF, acrónimo procedente de la expresión anglosajona “Physically Unclonable Function”, permite la generación de una firma única propia a dicho circuito. Esta firma puede ser utilizada con el fin de poner en marcha un mecanismo de autentificación de sistema electrónico.

Esta firma única puede igualmente ser utilizada como clave de cifrado única propia al circuito. En este 15 caso, no se requiere la memorización de la clave dentro del circuito integrado.

Las firmas son generadas directamente por los circuitos. Al no ser requerida la intervención humana, se ha visto mejorada la resistencia a ataques, especialmente ataques tales como la observación.

En el estado de la técnica existen diferentes maneras de aplicar funciones PUF. Así, el artículo de R. Pappu titulado Physical One-Way Functions, PhD Thesis, Massachussetts Institute of Technology, Marzo 2001,

describe qué es una PUF óptica. Las PUF ópticas están compuestas de un material transparente que contiene partículas dispersadas aleatoriamente permitiendo la desviación de la luz láser.

Las PUF peliculares, designadas por la expresión anglosajona “coating PUF”, son igualmente utilizadas. Este tipo de PUF viene descrito en el artículo de P. Tuyls, B. Skoric y T. Kevenaar titulado Security with Noisy Data: Private Biometrics, Secure Key Storage and Anti-Counterfeiting, Secaucus, NJ USA: Springer-Verlag New

York, 2007. En este caso, un material opaco es estimulado aleatoriamente con partículas dieléctricas y posicionado por encima del circuito integrado.

Una familia de PUF denominadas PUF de silicio utiliza las incoherencias estructurales introducidas por los procedimientos de fabricación de los circuitos integrados. La diferencia de dispersión entre los hilos y los transistores que constituyen dichos circuitos es en efecto significativa de un circuito a otro, aun formando parte 30 del mismo grupo. Esa familia comprende, especialmente, las PUF árbitros, las PUF de oscilador en anillo y las SRAM PUF. Las PUF de silicio pueden aplicarse en circuitos ASIC o FPGA sin ninguna modificación tecnológica.

Las PUF árbitros vienen descritas en el artículo de B. Gassend, D. E. Clarke, M. van Dijk, y S. Devadas, titulado Silicon physical random functions, ACM Conference on Computer and Communications Security, 2002, páginas 148-160. En este tipo de PUF, una misma señal se propaga tomando dos caminos de un circuito de retardo, siendo los dos circuitos distintos y pudiendo ser configurados con la ayuda de palabras de control. Un árbitro compara el retardo entre las dos señales que resultan de estas dos propagaciones, y el resultado de esta comparación desemboca en la firma del circuito integrado. Uno de los inconvenientes de este tipo de PUF es que los elementos que permiten la parametrización de los caminos deben estar equilibrados en términos de retardos, lo que implica una dificultad a la hora de su diseño.

Las PUF de pares de osciladores en anillo son también PUF de silicio. Aparecen descritas en el artículo de G. E. Suh y S. Devadas titulado Physical unclonable functions for device authentication and secret key generation, DAC, 2007, páginas 9-14. Aquí se comparan las frecuencias generadas por un par de osciladores en anillo idénticos. El resultado de esta comparación desemboca en la firma del circuito integrado. Un inconveniente de los osciladores en anillo es que dichos osciladores son sensibles a los efectos denominados de segundo 45 orden como, por ejemplo, los efectos vinculados al acoplamiento mutuo entre los osciladores o las perturbaciones introducidas en un oscilador en el momento de un ataque.

Un objeto de la invención es, especialmente, paliar los inconvenientes descritos anteriormente.

A tal fin, la invención tiene como objeto un circuito integrado de silicio que incluye una función físicamente no reproducible LPUF que permite la generación de una firma propia a dicho circuito. Dicha función incluye un 50 oscilador en anillo compuesto por un bucle recorrido por una señal e, estando formado dicho bucle por N cadenas de retardo topológicamente idénticas, conectadas en serie entre ellas, y una compuerta de inversión, estando compuesta una cadena de retardo por M elementos de retardo conectados en serie entre ellos.

Asimismo, incluye un módulo de control que genera N palabras de control, estando utilizadas dichas palabras para configurar el valor de los retardos introducidos por las cadenas de retardo en la señal e que les recorre. Incluye igualmente un módulo de medición que mide la frecuencia de la señal a la salida de la última cadena de retardo tras la actualización de las palabras de control. Asimismo, incluye medios para deducir de las medidas de frecuencia los bits que componen la firma del circuito.

El circuito es, por ejemplo, un circuito ASIC o un FPGA.

Según un modo de realización, la firma es utilizada como clave de cifrado.

Según otro modo de realización, la firma es utilizada para su autentificación.

Los elementos de retardo incluyen, por ejemplo, medios para bifurcar la señal que les recorre según al 10 menos dos caminos distintos, introduciendo un camino un valor de retardo que le es propio, estando controlada esta separación por al menos un bit que pertenece a una palabra de control.

Según un aspecto de la invención, se presentan palabras de desafío compuestas por una concatenación de palabras de control a la entrada del módulo de control, generando dicho módulo combinaciones a partir de dichas palabras con el fin de configurar las cadenas de retardo.

Los bits de la firma se determinan, por ejemplo, en función de la clase de las frecuencias medidas por las diferentes combinaciones de palabras de control.

Los bits de la firma se determinan, por ejemplo, en función de las diferencias estimadas entre dos valores de frecuencia medidos, correspondiendo un valor de frecuencia medido a una combinación de palabras de control.

Los bits de la firma se determinan, por ejemplo, en función del valor de la relación entre dos diferencias de frecuencia estimadas.

En un modo de realización, el circuito incluye un generador de números aleatorios, siendo utilizados los números aleatorios con el fin de seleccionar el orden en el que son medidas las frecuencias correspondientes a las combinaciones de las palabras de control.

El circuito contiene, por ejemplo, al menos un bit de paridad, siendo utilizado dicho bit para corregir un bit de la firma generada con un error.

La invención tiene igualmente como objeto un procedimiento de test de circuitos integrados que contiene una función físicamente no reproducible LPUF. Se aplica una sucesión de etapas a los circuitos testados de modo que se seleccionen los circuitos que permiten generar una firma propia a dicho circuito con un nivel de 30 fiabilidad elegido, correspondiendo dichas etapas a una selección de los parámetros T y Th de configuración del test, así como de B combinaciones de palabras de control con una distancia de Hamming al menos igual a un valor predefinido HD, y seguidamente a una fase de mediciones durante la cual se miden cantidades representativas de los bit de firma del circuito, realizándose hasta T mediciones por bit de firma, estando acumuladas esas T mediciones de modo que se decida si el bit correspondiente es indeterminado, habiendo tomado la decisión tras la comparación con al menos un valor deducido del valor del parámetro Th, estando seleccionados los circuitos testados en función del número de bits indeterminados detectados.

Según un modo de aplicación, el procedimiento incluye una etapa de determinación de la probabilidad para que un circuito no sea seleccionado, estando determinada dicha probabilidad utilizando la expresión:

en la que:

erf () es la función... [Seguir leyendo]

Reivindicaciones:

1. Circuito integrado de silicio que incluye una función físicamente no reproducible LPUF que permite la generación de una firma propia a dicho circuito, estando dicha función caracterizada porque incluye:

-un oscilador en anillo compuesto por un bucle (502) recorrido por una señal e, estando formado dicho bucle por N cadenas de retardo (500, 501) topológicamente idénticas, conectadas en serie entre ellas, y una compuerta de inversión (503) , estando compuesta una cadena de retardo (500, 501) por M elementos de retardo (506, 507) conectados en serie entre ellos; -un módulo de control (505) que genera N palabras de control (C1, C2) , estando utilizadas dichas palabras para configurar el valor del los retardos introducidos por las cadenas de retardo en la señal e que les recorre; -un módulo de medición (504) que mide la frecuencia de la señal a la salida de la última cadena de retardo

(501) tras la actualización de las palabras de control; -medios para deducir de las medidas de frecuencia los bits que componen la firma del circuito.

2. Circuito según la reivindicación 1, caracterizado porque el circuito es un ASIC o un FPGA.

3. Circuito según una de las reivindicaciones 1 o 2, caracterizado porque la firma es utilizada como clave de cifrado.

4. Circuito según una de las reivindicaciones 1 o 2, caracterizado porque la firma es utilizada para su autentificación.

5. Circuito según una de las reivindicaciones precedentes, caracterizado porque los elementos de retardo incluyen medios para bifurcar (400) la señal que les recorre (ei, j) según al menos dos caminos distintos (403, 404) , introduciendo un camino un valor de retardo (di, j0, di, j1) que le es propio, estando controlada esta separación por al menos un bit (Ci, j) que pertenece a una palabra de control.

6. Circuito según una de las reivindicaciones precedentes, caracterizado porque las palabras de desafío compuestas por una concatenación de palabras de control son presentadas a la entrada del módulo de control (505) , generando dicho módulo combinaciones a partir de dichas palabras con el fin de configurar las cadenas de retardo (500, 501) .

7. Circuito según una de las reivindicaciones precedentes, caracterizado porque los bits de la firma se determinan en función de la clase de las frecuencias medidas por las diferentes combinaciones de palabras de control.

8. Circuito según una de las reivindicaciones 1 a 6, caracterizado porque los bits de la firma se

determinan en función de las diferencias estimadas ( ) entre dos valores de frecuencia medidos, ^

correspondiendo un valor de frecuencia medido a una combinación de palabras de control.

δj

9. Circuito según una de las reivindicaciones 1 a 6, caracterizado porque los bits de la firma se determinan en función del valor de la relación entre dos diferencias de frecuencia estimadas (δj) .

10. Circuito según una de las reivindicaciones precedentes, caracterizado porque incluye un generador de números aleatorios, siendo utilizados los números aleatorios con el fin de seleccionar el orden en el que son medidas las frecuencias correspondientes a las combinaciones de palabras de control.

11. Circuito según una de las reivindicaciones precedentes, caracterizado porque contiene al menos un bit de paridad, siendo utilizado dicho bit para corregir un bit de la firma generado con un error.

12. Procedimiento de test de circuitos integrados que incluye una función físicamente no reproducible LPUF según una de las reivindicaciones 1 a 11, caracterizado porque se aplica una sucesión de etapas a los circuitos testados de modo que se seleccionen los circuitos permitiendo generar una firma propia a dicho circuito con un nivel de fiabilidad elegido, correspondiendo dichas etapas a:

-una selección de los parámetros T y Th (1000) de configuración del test, así como de B combinaciones de palabras de control con una distancia de Hamming al menos igual a un valor predefinido HD; -una fase de mediciones (1003) durante la cual se miden cantidades representativas ( δj. ^ ) de los bit de firma del circuito, realizándose hasta T mediciones por bit de firma, estando acumuladas esas T mediciones de modo que se decida si el bit correspondiente es indeterminado, habiendo tomado la decisión tras la comparación con al menos un valor deducido del valor del parámetro Th, estando seleccionados los circuitos testados en función del número de bits indeterminados detectados.

13. Procedimiento según la reivindicación 12, caracterizado porque incluye una etapa de determinación de la probabilidad para que un circuito no sea seleccionado, estando determinada dicha probabilidad utilizando la expresión:

en la que:

erf () es la función de error de Gauss; σes la varianza de las mediciones de las cantidades representativas de los bits de firma del circuito.

14. Procedimiento según una de las reivindicaciones 12 o 13, caracterizado porque incluye una etapa de determinación de la probabilidad de error por bit de firma, estando determinada dicha probabilidad utilizando la 10 expresión:

en la que:

δj es una diferencia de frecuencia medida entre dos frecuencias que corresponden a la aplicación de dos combinaciones de palabras de control distintas;

s, definida como s2 , es la varianza del ruido de medición.

15. Procedimiento según una de las reivindicaciones 12 a 14, caracterizado porque un circuito es seleccionado si ningún bit de la firma es indeterminado.

16. Procedimiento según una de las reivindicaciones 12 a 14, caracterizado porque cuando la función

LPUF de un circuito testado está asociada a un bit de paridad cuyo valor está determinado a partir de la firma de 20 dicho circuito, dicho circuito es seleccionado si el número de bit indeterminado es estrictamente inferior a 2.

17. Procedimiento según una de las reivindicaciones 12 a 16, caracterizado porque los valores de s2 y σ2son medidos (1002) para una temperatura sensiblemente igual a +70Cº y una tensión de alimentación de los circuitos sensiblemente inferior al 5% con respecto a la tensión de alimentación nominal, estando efectuada la fase de mediciones (1003) en las mismas condiciones.

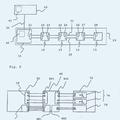

18. Sistema de test que aplica el procedimiento según una de las reivindicaciones 13 a 17, caracterizado porque está compuesto por un ordenador (1105) provisto de una interfaz de usuario (1104) , un equipo (1101) que permite controlar las sondas de medición (1106, 1107) , teniendo dichas sondas la función de recopilar las mediciones de las cantidades representativas ( ^

δj. ) de los bits de firma producidas por los circuitos testados (1103) , estando a continuación efectuados los tratamientos asociados a esta fase por el ordenador (1105) y 30 mostrados en su interfaz (1104) .

Dibujos

PALABRA

MÓDULO DE CONTROL

DE

RESPUESTA

DESAFÃ?O

Patentes similares o relacionadas:

Circuito integrado digital protegido contra errores transitorios, del 9 de Octubre de 2019, de THALES: Circuito integrado digital que comprende un conjunto lógico que comprende un bloque lógico funcional, una unidad lógica de detección […]

Procedimiento de prueba de circuitos de criptografía, circuito de criptografía asegurado adecuado para ser probado y procedimiento de cableado de tal circuito, del 27 de Marzo de 2019, de Institut Mines-Telecom: Procedimiento de prueba de un circuito de criptografía que integra un secreto y que consta de registros y de puertas (10, 211, 212, […]

Dispositivo de medición de posición y método para verificar una señal de ciclo de trabajo, del 13 de Febrero de 2019, de DR. JOHANNES HEIDENHAIN GMBH: Dispositivo de medición de posición que comprende una unidad de detección de posición , una unidad de procesamiento , una unidad de interfaz […]

Medición eficiente del ruido de la fuente de alimentación basada en la incertidumbre de temporización, del 16 de Enero de 2019, de TELEFONAKTIEBOLAGET LM ERICSSON (PUBL): Un circuito integrado que comprende un dispositivo de medición de ruido de la fuente de alimentación, el circuito integrado que tiene un bloque funcional, comprendiendo […]

Método de protección para información de datos relativos a un dispositivo electrónico y su circuito de protección, del 25 de Abril de 2018, de Shenzhen Xinguodu Technology Co. Ltd: Un circuito para proteger información de datos de un equipo electrónico, que comprende un procesador y un dispositivo electrónico conectado con el procesador […]

Procedimiento para la prueba funcional de una unidad receptora PS15 de un aparato de mando de automóvil y unidad receptora PS15 correspondiente, del 26 de Octubre de 2016, de CONTINENTAL AUTOMOTIVE GMBH: Procedimiento para la verificación funcional de una unidad receptora PSI5 de un aparato de mando de automóvil, en donde la unidad receptora […]

Dispositivo de protección contra fallas en circuitos de árbol de reloj, del 10 de Febrero de 2016, de Winbond Electronics Corp: Un circuito integrado "CI", que comprende:

Un circuito de árbol de reloj configurado para distribuir una señal de reloj en el circuito […]

Dispositivo de protección contra fallas en circuitos de árbol de reloj, del 10 de Febrero de 2016, de Winbond Electronics Corp: Un circuito integrado "CI", que comprende:

Un circuito de árbol de reloj configurado para distribuir una señal de reloj en el circuito […]

Procedimiento, componente electrónico y sistema para diagnosticar enlaces de comunicación, del 6 de Enero de 2016, de PHOENIX CONTACT GMBH & CO. KG: Procedimiento para diagnosticar enlaces de comunicación en un sistema de comunicación , que incluye las etapas

a) aportación de una pluralidad de unidades […]

Procedimiento, componente electrónico y sistema para diagnosticar enlaces de comunicación, del 6 de Enero de 2016, de PHOENIX CONTACT GMBH & CO. KG: Procedimiento para diagnosticar enlaces de comunicación en un sistema de comunicación , que incluye las etapas

a) aportación de una pluralidad de unidades […]