Circuito de cooperación.

Un circuito de cooperación (1), que comprende:

un primer módulo de control (2),

capaz de generar una primera señal de control como una señal PWM y unasegunda señal de control, estando la frecuencia y el ancho de pulso de la primera señal de controldeterminados por la frecuencia y el ancho de pulso de la segunda la señal de control y

un segundo módulo de control (3), acoplado al primer módulo de control (2) para recibir la primera señal decontrol y la segunda señal de control y generar una tercera señal de control de acuerdo con la primera señal decontrol y la segunda señal de control;

en el que el segundo módulo de control (3) provoca un retardo de fase entre la fase de la tercera señal decontrol y la fase de la segunda señal de control de acuerdo con la primera señal de control,

caracterizado porque

la frecuencia de la primera señal de control es igual a la frecuencia de la segunda señal de control multiplicada por elnúmero de los módulos de control primero y segundo, y el ancho de pulso de la primera señal de control es igual alresto del ancho de pulso de la segunda señal de control dividido por el ciclo de la primera señal de control, y porquela frecuencia y el ciclo de trabajo de la tercera señal de control son los mismos que la frecuencia y el ciclo de trabajode la segunda señal de control.

Tipo: Patente Europea. Resumen de patente/invención. Número de Solicitud: E08172515.

Solicitante: Macroblock, Inc.

Nacionalidad solicitante: Taiwan, Provincia de China.

Dirección: 6F-4, NO. 18, PU-TING RD. HSINCHU TAIWAN, R.O.C. 30072 TAIWAN.

Inventor/es: SHIH,FU-YANG, WU,KEN-TANG.

Fecha de Publicación: .

Clasificación Internacional de Patentes:

- G06F13/42 FISICA. › G06 CALCULO; CONTEO. › G06F PROCESAMIENTO ELECTRICO DE DATOS DIGITALES (sistemas de computadores basados en modelos de cálculo específicos G06N). › G06F 13/00 Interconexión o transferencia de información u otras señales entre memorias, dispositivos de entrada/salida o unidades de procesamiento (circuitos de interfaz para dispositivos de entrada/salida específicos G06F 3/00; sistemas multiprocesadores G06F 15/16). › Protocolo de transferencia para bus, p. ej. interbloqueo; Sincronización.

PDF original: ES-2398850_T3.pdf

Fragmento de la descripción:

Circuito de cooperación Antecedentes de la invención 1. Campo de la invención:

La presente invención se refiere en general a un circuito de cooperación y, más en particular, a un circuito de cooperación con un retardo de fase entre la fase de la señal de control de etapa actual y la fase de la señal de control de etapa anterior.

2. Descripción de la técnica anterior:

El circuito de cooperación, usado en la actualidad en el control de corriente de envergadura, se controla generalmente mediante conmutadores internos con bus de interfaz periférica serie (SPI) , bus I2C, bus SM o bus PM, lo que da como resultado las siguientes desventajas:

1. Se requiere un ajuste externo de direccionamiento para el bus I2C, bus SM o bus PM. La frecuencia de reloj es demasiado baja (menos de 400 kHz) para la conmutación de alta frecuencia. Por ejemplo, se requiere que la frecuencia de reloj sea de 60 MHz para una modulación por ancho de pulso (PWM) de 500 kHz con una resolución de 7 bits.

2. Aun cuando el bus SPI es capaz de usar una topología de anillo sin direccionamiento externo, la baja frecuencia de reloj mencionada anteriormente no puede coincidir con el funcionamiento. Además, un funcionamiento de alta frecuencia de reloj consume mucha energía y provoca EMI y ruido.

3. Si el maestro necesita enviar los datos de ajuste tales como la carga, la resolución o el cambio de fase... etc. al esclavo, los esclavos deberían tener un reloj/oscilador interno para contar la carga, lo que añade el coste y consumo de energía. Si se usa un reloj externo, puede dar como resultado un alto consumo de energía y una interferencia EM. Y aún peor, si la frecuencia de reloj de cada IC es diferente, la frecuencia PWM de cada IC es diferente. Por lo tanto, existe una necesidad de proporcionar un circuito de cooperación sin direccionamiento adicional que sea capaz de lograr un bajo consumo energético, una baja EMI y una frecuencia PWM idéntica.

El documento: Huston B: “The serial peripheral interface (SPI) for low cost IC interconnection” Mini/Micro Northeast Computer-conference and exhibition, XX, XX, 1 de enero (01/01/1984) páginas 23/2-1 desvela un puerto de salida SPI de 8 bits, que puede ser en cascada.

El documento US 6.023.420 desvela un inversor trifásico para pequeños motores de alta velocidad y presenta probablemente la técnica anterior más cercana.

Sumario de la invención Un objeto de la presente invención es proporcionar un circuito de cooperación que mejore la técnica anterior y que sea capaz de lograr, preferentemente, pequeñas ondas de potencia, baja EMI y frecuencia PWM idéntica entre módulos con retardos de fase.

Con el fin de lograr el objeto anterior, en una realización, la presente invención proporciona un circuito de cooperación de acuerdo con la reivindicación 1.

Breve descripción de los dibujos Los objetos, valores y ventajas de la realización preferida de la presente invención se entenderán fácilmente por los dibujos adjuntos y las descripciones detalladas, en los que:

La figura 1 es un diagrama sistemático de un circuito de cooperación de acuerdo con la realización preferida de la presente invención;

La figura 2 es un diagrama sistemático de un circuito de cooperación de acuerdo con otra realización de la presente invención;

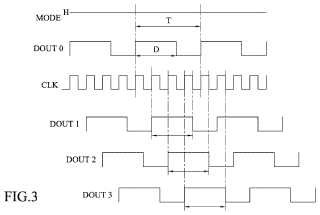

La figura 3 es una forma de onda del disparador de un circuito de cooperación en la figura 2;

La figura 4 es otra forma de onda del disparador de un circuito de cooperación en la figura 2;

La figura 5 es un diagrama sistemático de un circuito de cooperación de acuerdo con otra realización de la presente invención; y

La figura 6 es un diagrama sistemático de un circuito de cooperación de acuerdo con otra realización de la presente invención.

Descripción detallada de la realización preferida La presente invención puede ejemplificarse mediante las realizaciones preferidas, como se describe en lo sucesivo en el presente documento.

La figura 1 es un diagrama sistemático de un circuito de cooperación de acuerdo con la realización preferida de la presente invención. Haciendo referencia a la figura 1, el circuito de cooperación 1 de la presente invención comprende: un primer módulo de control 2 y un segundo módulo de control 3. El primer módulo de control 2 es capaz de generar una primera señal de control CLK y una segunda señal de control DOUT0. El ancho de pulso de la primera señal de control CLK está determinado por el ancho de pulso de la segunda señal de control DOUT0 y el número de los módulos de circuito de cooperación. El segundo módulo de control 3 está acoplado al primer módulo de control 2 para recibir la primera señal de control CLK y la segunda señal de control DOUT0, y generar una tercera señal de control DOUT1 de acuerdo con la primera señal de control CLK y la segunda señal de control DOUT0. El segundo módulo de control 3 provoca un retardo de fase entre la fase de la tercera señal de control DOUT1 y la fase de la segunda señal de control DOUT0 de acuerdo con la primera señal de control CLK y la segunda señal de control DOUT0. La frecuencia y el ciclo de trabajo de la tercera señal de control DOUT1 son los mismos que la frecuencia y el ciclo de trabajo de la segunda señal de control DOUT0.

En una realización, de acuerdo con las necesidades del usuario, la tercera señal de control DOUT1 se retroalimenta al primer módulo de control 2. En otra realización, el primer módulo de control 2 genera una cuarta señal MODE de control. Cuando la cuarta señal MODE de control está en un estado, el primer módulo de control 2 envía la primera señal de control CLK y la segunda señal de control DOUT0 al segundo módulo de control 3 y determina el número del segundo módulo de control 3 de acuerdo con la tercera señal de control DOUT1 desde el segundo módulo de control 3 hacia el primer módulo de control 2. Cuando la cuarta señal MODE de control está en el estado, el primer módulo de control 2 envía la primera señal de control CLK y la segunda señal de control DOUT0 al segundo módulo de control 3 para habilitar el segundo módulo de control 3. Cuando la cuarta señal MODE de control está en otro estado, el segundo módulo de control 3 provoca un retardo de fase entre la fase de la tercera señal de control DOUT1 y la fase de la segunda señal de control DOUT0 de acuerdo con la primera señal de control CLK y la segunda señal de control DOUT0. Para el cálculo de la frecuencia y el ancho de pulso, la frecuencia de la primera señal de control CLK es igual, preferentemente, a la frecuencia de la segunda señal de control DOUT0 multiplicada por el número del primer módulo de control 2 y los segundos módulos de control 3 habilitados. El ancho de pulso de la primera señal de control CLK es igual, preferentemente, al resto del ancho de pulso de la segunda señal de control DOUT0 dividido por el ciclo de la primera señal de control CLK.

Para el disparo del primer módulo de control 2 y el segundo módulo de control 3, es preferible que la tercera señal de control DOUT1 sea alta cuando la primera señal de control CLK se dispara por el borde de subida para un próximo instante después de que la segunda señal de control DOUT0 se dispara por el borde de subida para ser alta; de otro modo, la tercera señal de control DOUT1 es alta cuando la primera señal de control CLK se dispara por el borde de subida para un próximo instante después de que la primera señal de control CLK se dispara por el borde de bajada y la segunda señal de control DOUT0 es alta. La tercera señal de control DOUT1 es baja cuando la primera señal de control CLK se dispara por el borde de bajada para un próximo instante después de que la segunda señal de control DOUT0 se dispara por el borde de bajada para ser baja; de otro modo, la tercera señal de control DOUT1 es baja cuando la primera señal de control CLK se dispara por el borde de bajada para un próximo instante después de que la primera señal de control CLK se dispara por el borde de bajada y la segunda señal de control DOUT0 es baja. El ciclo de trabajo de un módulo de control se define entre el momento en que la segunda señal de control DOUT0 (o la tercera señal de control DOUT1) se dispara por el borde de subida para ser alta y el momento en que la segunda señal de control DOUT0 (o la tercera señal de control DOUT1) se dispara por el borde de bajada para ser baja. La forma de onda del disparador detallada se describirá con los terceros módulos de control plurales en lo sucesivo el presente documento.

La figura 2 es un diagrama sistemático de un circuito de cooperación de acuerdo con otra realización de la presente invención, y la figura 3 es una forma... [Seguir leyendo]

Reivindicaciones:

1. Un circuito de cooperación (1) , que comprende:

un primer módulo de control (2) , capaz de generar una primera señal de control como una señal PWM y una segunda señal de control, estando la frecuencia y el ancho de pulso de la primera señal de control determinados por la frecuencia y el ancho de pulso de la segunda la señal de control y un segundo módulo de control (3) , acoplado al primer módulo de control (2) para recibir la primera señal de control y la segunda señal de control y generar una tercera señal de control de acuerdo con la primera señal de control y la segunda señal de control; en el que el segundo módulo de control (3) provoca un retardo de fase entre la fase de la tercera señal de control y la fase de la segunda señal de control de acuerdo con la primera señal de control,

caracterizado porque la frecuencia de la primera señal de control es igual a la frecuencia de la segunda señal de control multiplicada por el número de los módulos de control primero y segundo, y el ancho de pulso de la primera señal de control es igual al resto del ancho de pulso de la segunda señal de control dividido por el ciclo de la primera señal de control, y porque la frecuencia y el ciclo de trabajo de la tercera señal de control son los mismos que la frecuencia y el ciclo de trabajo de la segunda señal de control.

2. El circuito de cooperación (1) de acuerdo con la reivindicación 1, que además comprende:

una pluralidad de terceros módulos de control, capaces de recibir la primera señal de control, en el que un tercer módulo de control (4) de primera etapa está acoplado al segundo módulo de control (3) para recibir la primera señal de control y la tercera señal de control con el fin de generar una tercera señal de control de etapa actual del tercer módulo de control de primera etapa; en el que los terceros módulos de control (5) subsiguientes están acoplados en serie al tercer módulo de control (4) de primera etapa, y cada tercer módulo de control (5) subsiguiente se convierte en un tercer módulo de control (4) de etapa actual en secuencia a medida que las terceras señales de control (4, 5) son generadas por un tercer módulo de control (4) anterior; en el que el tercer módulo de control (4, 5) de etapa actual recibe la tercera señal de control de etapa actual desde el tercer módulo de control (4, 5) anterior y la primera señal de control, y genera una nueva tercera señal de control de etapa actual, en el que cada tercer módulo de control (4, 5) subsiguiente provoca un retardo de fase entre la fase de la tercera señal de control de etapa actual y la fase de la tercera señal de control de etapa actual generada por el tercer módulo de control (4, 5) anterior, de acuerdo con la primera señal de control y la tercera señal de control generada por el tercer módulo de control (4, 5) anterior.

3. El circuito de cooperación (1) de acuerdo con la reivindicación 1, que además comprende:

una pluralidad de terceros módulos de control (4, 5) , en el que un tercer módulo de control (4) de primera etapa está acoplado al segundo módulo de control (3) , mientras que los otros terceros módulos de control (5) están acoplados a un tercer módulo de control (4) de etapa anterior, en el que el segundo módulo de control (3) genera la primera señal de control enviada al tercer módulo de control (4) de primera etapa de acuerdo con la primera la señal de control, mientras que cada uno de los otros terceros módulos de control (4, 5) genera la primera señal de control enviada a un tercer módulo de control (4, 5) de próxima etapa de acuerdo con la primera señal de control del tercer módulo de control de etapa anterior, en el que cada uno de los módulos de control genera una primera señal de control de etapa actual y la tercera señal de control de etapa actual de acuerdo con la primera señal de control y la tercera señal de control generada por un módulo de control de etapa anterior, en el que el segundo módulo de control (3) provoca un retardo de fase entre la fase de la tercera señal de control y la fase de la segunda señal de control de acuerdo con la primera señal de control y la segunda señal de control, en el que cada uno de los terceros módulos de control provoca un retardo de fase entre la fase de una tercera señal de control de etapa actual y la fase de una tercera señal de control de etapa anterior de acuerdo con la primera señal de control y la señal de control de etapa anterior generada por el tercer módulo de control de etapa anterior.

4. El circuito de cooperación (1) de acuerdo con la reivindicación 1, en el que la tercera señal de control se retroalimenta al primer módulo de control (2) generando una cuarta señal de control, provocando el segundo módulo de control (3) un retardo de fase entre la fase de la tercera señal de control y la fase de la segunda señal de control de acuerdo con la primera señal de control y la segunda señal de control cuando la cuarta señal de control está en un estado, mientras que la primera señal de control, la segunda señal de control y la tercera señal de control muestran la frecuencia respectiva, el ancho de pulso respectivo y la fase respectiva, de manera que el primer módulo de control (2) envía la primera señal de control y la segunda señal de control al segundo módulo de control (3) , y determina el número de segundos módulos de control (3) habilitados de acuerdo con la tercera señal de

control retroalimentada desde el segundo módulo de control (3) hacia el primer módulo de control (2) cuando la cuarta señal de control está en otro estado.

5. El circuito de cooperación (1) de acuerdo con la reivindicación 2, en el que una señal de control de última etapa de un tercer módulo de control de última etapa se retroalimenta al primer módulo de control (2) generando una cuarta señal de control, provocando el segundo módulo de control (3) un retardo de fase entre la fase de la tercera señal de control y la fase de la segunda señal de control de acuerdo con la primera señal de control y la segunda señal de control, y provocando los terceros módulos de control un retardo de fase entre la fase de una señal de control de etapa actual y la fase de una señal de control de etapa anterior de acuerdo con la primera señal de control y la señal de control de etapa anterior cuando la cuarta señal de control está en un estado, mientras que la primera señal de control, la segunda señal de control y la tercera señal de control muestran la frecuencia respectiva, el ancho de pulso respectivo y la fase respectiva, de manera que el primer módulo de control (2) envía la primera señal de control al segundo módulo de control (3) para que además pase a través de cada uno de los terceros módulos de control, y determina el número de segundos y terceros módulos de control habilitados de acuerdo con la señal de control de última etapa retroalimentada hacia el primer módulo de control (2) cuando la cuarta señal de control está en otro estado.

6. El circuito de cooperación (1) de acuerdo con la reivindicación 3, en el que la primera señal de control y la tercera señal de control de un tercer módulo de control de última etapa se retroalimentan al primer módulo de control (2) generando una cuarta señal de control, provocando el segundo módulo de control (3) un retardo de fase entre la fase de la tercera señal de control y la fase de la segunda señal de control de acuerdo con la primera señal de control y la segunda señal de control, y provocando los terceros módulos de control un retardo de fase entre la fase de la señal de control de etapa actual y la fase de la tercera señal de control de etapa anterior de acuerdo con la primera señal de control que pasa a través del tercer módulo de control de etapa anterior y la tercera señal de control de etapa anterior cuando la cuarta señal de control está en un estado, mientras que la primera señal de control, la segunda señal de control y la tercera señal de control muestran la frecuencia respectiva, el ancho de pulso respectivo y la fase respectiva, de manera que el primer módulo de control (2) envía la primera señal de control al segundo módulo de control (3) para que además pase a través de cada uno de los terceros módulos de control, y determina el número de segundos y terceros módulos de control habilitados de acuerdo con la tercera señal de control retroalimentada desde el tercer módulo de control de última etapa hacia el primer módulo de control

(2) cuando la cuarta señal de control está en otro estado.

7. El circuito de cooperación (1) de acuerdo con la reivindicación 1, en el que la tercera señal de control es alta cuando la primera señal de control se dispara por el borde de subida para un próximo instante después de que la segunda señal de control se dispara por el borde de subida, mientras que la tercera señal de control es alta cuando la primera señal de control se dispara por el borde de bajada para un próximo instante después de que la segunda señal de control se dispara por el borde de bajada.

8. El circuito de cooperación (1) de acuerdo con la reivindicación 2, en el que cada una de las terceras señales de control es alta cuando la primera señal de control se dispara por el borde de subida para un próximo instante después de que la segunda señal de control se dispara por el borde de subida, mientras que cada una de las terceras señales de control es alta cuando la primera señal de control se dispara por el borde de bajada para un próximo instante después de que la segunda señal de control se dispara por el borde de bajada.

9. El circuito de cooperación (1) de acuerdo con la reivindicación 3, en el que cada una de las terceras señales de control es alta cuando la primera señal de control se dispara por el borde de subida para un próximo instante después de que la segunda señal de control se dispara por el borde de subida, mientras que cada una de las terceras señales de control es alta cuando la primera señal de control se dispara por el borde de bajada para un próximo instante después de que la segunda señal de control se dispara por el borde de bajada.

10. El circuito de cooperación (1) de acuerdo con la reivindicación 1, en el que la tercera señal de control es alta cuando la primera señal de control se dispara por el borde de subida para un próximo instante si la primera señal de control se dispara por el borde de bajada y la segunda señal de control es alta, mientras que la tercera señal de control es baja cuando la primera señal de control se dispara por el borde de bajada para un próximo instante si la primera señal de control se dispara por el borde de subida y la segunda señal de control es baja.

11. El circuito de cooperación (1) de acuerdo con la reivindicación 2, en el que la tercera señal de control del módulo de control de etapa actual es alta cuando la primera señal de control se dispara por el borde de subida para un próximo instante si la primera señal de control se dispara por el borde de bajada y la tercera señal de control de etapa actual desde el tercer módulo de control anterior es alta, mientras que la tercera señal de control del módulo de control de etapa actual es baja cuando la primera señal de control se dispara por el borde de bajada para un próximo instante si la primera señal de control se dispara por el borde de subida y la tercera señal de control de etapa actual desde el tercer módulo de control anterior es baja.

12. El circuito de cooperación (1) de acuerdo con la reivindicación 3, en el que la tercera señal de control del módulo de control de etapa actual es alta cuando la primera señal de control se dispara por el borde de subida para un próximo instante si la primera señal de control se dispara por el borde de bajada y la tercera señal de control de

etapa actual desde el tercer módulo de control anterior es alta, mientras que la tercera señal de control del módulo de control de etapa actual es baja cuando la primera señal de control se dispara por el borde de bajada para un próximo instante si la primera señal de control se dispara por el borde de subida y la tercera señal de control de etapa actual desde el tercer módulo de control anterior es baja.

13. El circuito de cooperación (1) de acuerdo con la reivindicación 1, en el que el primer módulo de control (2) es capaz de generar una quinta señal de control que comprende información del ancho de pulso y de la frecuencia de la segunda señal de control el segundo módulo de control (3) , acoplado al primer módulo de control (2) para recibir la quinta señal de control después de que la primera señal de control ha disparado el segundo módulo de control (3) , y generar la quinta señal

de control de un módulo de control de próxima etapa.

14. El circuito de cooperación (1) de acuerdo con la reivindicación 13, que además comprende:

una pluralidad de terceros módulos de control, capaces de recibir la primera señal de control, en el que un tercer módulo de control de primera etapa está acoplado al segundo módulo de control (3) para recibir la primera señal de control y la quinta señal de control con el fin de generar la tercera señal de control y

la quinta señal de control de un módulo de control de etapa actual, en el que la quinta señal de control del módulo de control de etapa actual comprende información del ancho de pulso y de la frecuencia de la tercera señal de control, en el que los otros terceros módulos de control están acoplados a un tercer módulo de control de etapa anterior para recibir la quinta señal de control y la primera señal de control desde el tercer módulo de control de etapa anterior para generar la tercera señal de control y la quinta señal de control del tercer módulo de control de etapa actual, en el que el segundo módulo de control (3) provoca un retardo de fase entre la fase de la tercera señal de control y la fase de la segunda señal de control de acuerdo con la primera señal de control y la segunda señal de control,

en el que cada uno de los terceros módulos de control provoca un retardo de fase entre la fase de la tercera señal de control de etapa actual y la fase de la tercera señal de control de etapa anterior de acuerdo con la primera señal de control y la tercera señal de control de etapa anterior.

Patentes similares o relacionadas:

Aparato para establecer la dirección de un módulo utilizando un reloj, del 17 de Junio de 2020, de LEXMARK INTERNATIONAL, INC.: Un circuito integrado específico de la aplicación (ASIC) que comprende: un pin de alimentación; un pin de masa; un pin de reloj I2C; un pin […]

Método para implementar un bus industrial de banda ancha de campo de internet, del 17 de Junio de 2020, de Kyland Technology Co., Ltd: Un método para implementar un bus industrial de banda ancha de campo de internet, caracterizado por que, el método es aplicable a un sistema de arquitectura […]

Sistema de arquitectura de bus de banda ancha de campo de internet de la industria, del 3 de Junio de 2020, de Kyland Technology Co., Ltd: Un sistema de arquitectura de bus de banda ancha de campo de Internet de la industria, caracterizado por que, el sistema comprende un controlador de bus […]

Método para gestionar la configuración del bus de banda ancha del campo de internet industrial, del 3 de Junio de 2020, de Kyland Technology Co., Ltd: Un método para gestionar la configuración de un bus de banda ancha del campo de internet industrial, caracterizado por que, el método es aplicable a […]

Método para implementar un bus de campo en tiempo real de banda ancha de Internet industrial, del 29 de Abril de 2020, de Kyland Technology Co., Ltd: Un método para implementar un bus de campo en tiempo real de banda ancha de Internet industrial, en donde el método puede aplicarse a una red de transferencia […]

Procedimiento para hacer funcionar un sistema de transmisión de datos y sistema de transmisión de datos, del 29 de Abril de 2020, de Siemens Mobility GmbH: Procedimiento para hacer funcionar un sistema de transmisión de datos en el que - un primer equipo de transmisión de datos está conectado […]

Método y aparato para detectar contrapresión de mensajes, del 8 de Abril de 2020, de HUAWEI TECHNOLOGIES CO., LTD.: Un método de detección de contrapresión de paquetes, en donde el método se aplica a un dispositivo que tiene un puerto de Interconexión de […]

Sistema de autenticación e información para instrumentos quirúrgicos reutilizables, del 8 de Abril de 2020, de Covidien LP (100.0%): Un método para comunicar datos a través de un bus, el método que comprende: autenticar un componente quirúrgico utilizando un microchip […]