Optimización de recopia para un sistema de memoria.

Un método que comprende:

obtener una página de datos y metadatos asociados de una memoria no volátil (106) de un subsistema de memoria (102) acoplado a un controlador (116),

almacenar la página de datos en un registro (110) del subsistema de memoria (102), enviar la página de datos y metadatos asociados desde el registro (110) al controlador (116) para procesamiento;

recibir una página de datos procesada y metadatos asociados desde el controlador (116), determinar si la página de datos procesada ha cambiado; si la página de datos procesada ha cambiado, escribir la página de datos procesada y metadatos asociados en el registro (110) en el subsistema de memoria (102);

si la página de datos procesada no ha cambiado, escribir los metadatos asociados en el registro (110) en el subsistema de memoria (102);

y escribir el contenido del registro en la memoria no volátil (106) .

Tipo: Patente Internacional (Tratado de Cooperación de Patentes). Resumen de patente/invención. Número de Solicitud: PCT/US2009/039160.

Solicitante: APPLE INC..

Nacionalidad solicitante: Estados Unidos de América.

Dirección: 1 INFINITE LOOP CUPERTINO CA 95014-2084 ESTADOS UNIDOS DE AMERICA.

Inventor/es: WAKRAT,Nir Jacob, HELM,Mark Alan.

Fecha de Publicación: .

Clasificación Internacional de Patentes:

- G06F11/10 FISICA. › G06 CALCULO; CONTEO. › G06F PROCESAMIENTO ELECTRICO DE DATOS DIGITALES (sistemas de computadores basados en modelos de cálculo específicos G06N). › G06F 11/00 Detección de errores; Corrección de errores; Monitorización (detección, corrección o monitorización de errores en el almacenamiento de información basado en el movimiento relativo entre el soporte de registro y el transductor G11B 20/18; monitorización, es decir, supervisión del progreso del registro o reproducción G11B 27/36; en memorias estáticas G11C 29/00). › añadiendo cifras binarias o símbolos especiales a los datos expresados según un código, p. ej. control de paridad, exclusión de los 9 o de los 11.

PDF original: ES-2378371_T3.pdf

Fragmento de la descripción:

Optimización de recopia para un sistema de memoria.

Campo Este objeto se refiere en general a sistemas de memoria.

Antecedentes

Una memoria flash es un tipo de memoria programable borrable eléctricamente de solo lectura (EEPROM) . Debido a que las memorias flash son no volátiles y relativamente densas, se usan para almacenar archivos y otros objetos persistentes en ordenadores portátiles, teléfonos móviles, cámaras digitales, reproductores de música portátiles, y muchos otros dispositivos en los que otras soluciones de almacenamiento (por ejemplo, discos magnéticos) son inapropiadas. Cuando se procesan datos almacenados en una memoria flash, se lee una página de datos de la memoria flash y se almacena en un registro. El contenido del registro se transfiere a un controlador que es externo a la memoria no volátil para procesamiento. La página de datos procesada se vuelve a introducir en el registro de forma que la página de datos procesada puede volver a escribirse en la memoria flash.

Se conoce por el documento US2006050576 un dispositivo de memoria flash NAND que implementa una función de limpieza basada en una función de recopia, en la que se leen datos del vector de memoria y se revisar/corrigen usando EDC, de forma que los datos corregidos se copian de nuevo en el vector de memoria.

Se conoce por el documento US4020466 un sistema de memoria jerárquico que implementa un algoritmo de recopia ‘el primero modificado menos recientemente', en el que el volver a copiar los datos en cualquier nivel se hace en base al orden en que se hizo la entrada en el almacén de recopia.

RESUMEN

En una operación de recopia o lectura para un subsistema de memoria no volátil, se usan indicadores de cambio en página de datos para gestionar la transferencia de páginas de datos entre un registro en una memoria no volátil y un controlador que es externo a la memoria no volátil. La invención se define en detalle en las reivindicaciones adjuntas independientes 1 y 5.

DESCRIPCION DE LOS DIBUJOS

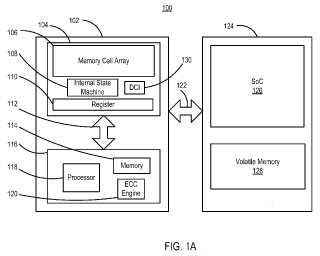

La Figura 1a es un diagrama de bloques de un sistema de memoria de ejemplo para implementar un proceso de recopia optimizado.

La Figura 1B es un diagrama de bloques de otro sistema de memoria de ejemplo para implementar un proceso de recopia optimizado.

La Figura 2 es un diagrama de flujo de un proceso de recopia optimizado de ejemplo 200 para computar y almacenar indicadores de cambio de datos utilizados por los sistemas de memoria de las Figuras 1A y 1B.

Las Figuras 3A-3C son diagramas de flujo de un proceso de recopia optimizado de ejemplo implementado por los sistemas de memoria de las Figuras 1A y 1B.

La Figura 4 es un diagrama de flujo de una operación de lectura optimizada de ejemplo implementada por los sistemas de memoria de las Figuras 1A y 1B.

La Figura 5 ilustra estructuras de datos de ejemplo utilizadas en los procesos de recopia de las Figuras 3A-3C.

DESCRIPCION DETALLADA

Ejemplos de Subsistemas de Memoria La Figura 1A es un diagrama de bloques de un sistema de memoria 100 de ejemplo para implementar un proceso optimizado de recopia. En algunas implementaciones, el sistema 100 puede incluir un subsistema de memoria 102 acoplado a un dispositivo anfitrión 124 a través de un bus externo 122 (por ejemplo, Interfaz Flash Abierta NAND (ONFI) , ATA) . El dispositivo anfitrión 124 puede ser cualquier dispositivo electrónico incluyendo pero no limitado a teléfonos inteligentes, reproductores, dispositivos de mensajes de texto, ordenadores portátiles, disqueteras de estado sólido, cámaras digitales, etcétera. El subsistema de memoria 102 puede ser cualquier subsistema de memoria no volátil (por ejemplo, NAND gestionada) .

El dispositivo anfitrión 124 puede incluir un sistema en un chip (SoC) 126 y memoria volátil 128. El SoC 126 puede incluir hardware y software para interactuar con el subsistema de memoria 102, tal como transmitir solicitudes de lectura y escritura hechas por aplicaciones que se están ejecutando en el dispositivo anfitrión 124.

El subsistema de memoria 102 puede incluir memoria no volátil 104 (también denominada "memoria sin editar") y un controlador externo 116. La memoria 104 puede incluir un vector de celdas de memoria 106, una máquina de estados interna 108, un registro de memoria 110 y un indicador de cambio de datos (DCI) 130. El controlador 116 puede incluir un procesador 118, memoria volátil 114 y una máquina de códigos correctores de errores (ECC) 120. Son posibles otras configuraciones para el subsistema de memoria 102. Por ejemplo, puede incluirse un registro de memoria temporal en la ruta de datos entre el vector de celdas de memoria 106 y el registro de memoria 110 para permitir a la máquina interna de estados leer a siguiente página de datos del vector de celdas de memoria 106 mientras transfiere la pagina actual al controlador 116 a través del bus interno 112.

La Figura 1B es un diagrama de bloques de otro sistema de memoria de ejemplo 130 para implementar un proceso optimizado de recopia. El sistema 130 muestra solo el subsistema de memoria 102, cuya operación se describió en referencia a la Figura 1A.

Operaciones de Recopia La recopia puede ser un comando del subsistema de memoria para trasladar datos desde una página a otra página. La recopia se puede utilizar en nivelación de desgaste y otras operaciones de gestión de memoria no volátil. En una operación típica de recopia, una página de datos es leída del vector de celdas de memoria 106 y es almacenada en el registro de memoria 110 por la máquina de estados interna. El controlador externo 116 lee o saca la página de datos del registro de memoria 110 de forma que el procesador 118 puede llevar a cabo una operación deseada en la página de datos (por ejemplo, una operación ECC) . La página de datos procesada puede volver a ser escrita en el registro de memoria 100 por el controlador 116. La máquina de estados interna 108 puede escribir el contenido del registro de memoria 110 en una nueva página de datos en el vector de celdas de memoria 106. Evitando la transferencia de contenidos enteros del registro 110 al controlador externo 116, se pueden reducir los tiempos de procesamiento y el consumo de energía.

Proceso de ejemplo para escribir nuevas páginas de memoria La Figura 2 es un diagrama de flujo de un proceso optimizado de recopia de ejemplo 200 para computar y almacenar indicadores de cambio de datos utilizados por los sistemas de memoria de las Figuras 1A y 1B. En algunas implementaciones, el proceso 200 puede empezar cuando una nueva página de datos se transfiere a un registro de memoria de un subsistema de memoria (202) . Se puede computar un DCI para la página de datos y almacenarlo en el subsistema de memoria (204) . Algunos ejemplos de indicadores de cambio de datos pueden incluir códigos de detección de errores (EDC) , incluyendo pero no limitados a: suma de comprobación, código Hamming, bit de paridad, comprobación de redundancia cíclica (CRC) , inversión de polaridad de símbolo, código Turbo, etcétera. Un EDC también puede ser parte de un ECC, tal como código Reed-Salomon, código Reed-Muller, código binario Golay, y códigos de comprobación de paridad de baja densidad. Una vez se han computado y almacenado los DCI, el contenido del registro puede escribirse en la memoria no volátil (206) . Los DCI pueden usarse para el proceso de recopia optimizado descrito en referencia a las Figuras 3A-3C.

Proceso de Recopia Optimizado de Ejemplo Las Figuras 3A-3C son diagramas de flujo de un proceso de recopia optimizado 300 implementado por los sistemas de memoria de las Figuras 1A y 1B. En algunas implementaciones, el proceso 300 puede empezar leyendo una página de datos de una memoria no volátil (por ejemplo, el vector de celdas de memoria 106) y almacenando la página de datos en un registro de memoria (302) (por ejemplo, el registro 110) . Un DCI (por ejemplo, el DCI 130) puede ser verificado para la página de datos en el registro de memoria (304) . En algunas implementaciones, el DCI puede ser computado y almacenado previamente en el subsistema de memoria cuando la página de datos se escribe primero en memoria no volátil (por ejemplo utilizando el proceso 200) . En otras implementaciones el DCI se puede computar "en el momento" como parte de la operación de lectura o como una operación separada. El subsistema de memoria puede notificar al controlador externo (por ejemplo, controlador externo 116) que se ha completado la operación de lectura (306) .

Si... [Seguir leyendo]

Reivindicaciones:

1. Un método que comprende:

obtener una página de datos y metadatos asociados de una memoria no volátil (106) de un subsistema de memoria (102) acoplado a un controlador (116) , almacenar la página de datos en un registro (110) del subsistema de memoria (102) , enviar la página de datos y metadatos asociados desde el registro (110) al controlador (116) para procesamiento;

recibir una página de datos procesada y metadatos asociados desde el controlador (116) , determinar si la página de datos procesada ha cambiado; si la página de datos procesada ha cambiado, escribir la página de datos procesada y metadatos asociados en el registro (110) en el subsistema de memoria (102) ; si la página de datos procesada no ha cambiado, escribir los metadatos asociados en el registro (110) en el subsistema de memoria (102) ; y escribir el contenido del registro en la memoria no volátil (106) .

2. El método según la reivindicación 1 donde determinar si la página de datos procesada ha cambiado, comprende además:

leer un indicador de cambio de datos para la página de datos procesada.

3. El método según la reivindicación 2, donde el indicador de cambio de datos está asociado con un código de detección de errores.

4. El método según la reivindicación 1, en donde determinar si la página de datos procesada ha cambiado, comprende además:

computar un indicador de cambio de datos para la página de datos procesada; y determinar si la página de datos procesada ha cambiado en base al indicador de cambio de página.

5. Un sistema (100) que comprende: un interfaz (112) adaptado para acoplarse a un controlador (116) ; memoria no volátil (106) ; un procesador (118) acoplado a la memoria no volátil (106) y a la interfaz (112) el procesador operable para

obtener una página de datos y metadatos asociados de la memoria no volátil (106) de un subsistema de memoria (106) acoplado al controlador (116) ;

almacenar la página de datos en un registro (110) del subsistema de memoria (102) ; enviar la página de datos y metadatos asociados desde el registro (110) a través de la interfaz (112) al controlador (116) para procesamiento;

recibir una página de datos procesada y metadatos asociados desde el controlador (116) a través de la interfaz (112) ; determinar si la página de datos procesada ha cambiado;

si la página de datos procesada ha cambiado, transferir la página de datos procesada y metadatos asociados en el registro (110) al subsistema de memoria (102) ;

si la página de datos procesada no ha cambiado, transferir los metadatos asociados en el registro (110) en el subsistema de memoria (102) ; y escribir el contenido del registro en la memoria no volátil (106) .

6. El sistema según la reivindicación 5 donde determinar si la página de datos procesada ha cambiado, comprende además:

leer un indicador de cambio de datos para la página de datos procesada.

7. El sistema según la reivindicación 6, donde el indicador de cambio de datos está asociado con un código de 5 detección de errores.

8. El sistema según la reivindicación 5, donde determinar si la página de datos procesada ha cambiado, comprende además: computar un indicador de cambio de datos para la página de datos procesada; y determinar si la página de datos procesada ha cambiado en base al indicador de cambio de página. 10

Patentes similares o relacionadas:

Método de segmentación de un bloque de transporte en múltiples bloques de código cuando se añade una CRC a cada bloque de código, del 2 de Octubre de 2019, de LG ELECTRONICS INC.: Un método para transmitir datos en un sistema de acceso inalámbrico, el método que comprende: obtener (S601) un número C de bloques de código en base […]

Dispositivo de memoria de semiconductor no volátil, del 28 de Agosto de 2019, de Winbond Electronics Corp: Un dispositivo de almacenamiento de semiconductor no volátil , que comprende: una matriz de memoria ; una pluralidad de circuitos de retención de […]

Seguimiento de cambios usando redundancia en tiempo lógico, del 4 de Junio de 2019, de Microsoft Technology Licensing, LLC: Un método para mantener el seguimiento de cambios entre porciones unitarias de un sistema de almacenaje, comprendiendo el método: […]

Métodos y sistemas para detectar y corregir errores en una memoria no volátil, del 30 de Enero de 2019, de Winbond Electronics Corp: Un sistema de memoria, que comprende: una matriz de memoria no volátil resistiva configurada para almacenar datos, bits de anticipación y bits de […]

Sistemas y métodos para asegurar datos en movimiento, del 9 de Mayo de 2018, de Security First Corp: Un método para leer y escribir un conjunto de datos, que comprende: dividir el conjunto de datos en una o más comparticiones de datos 5 usando un algoritmo […]

Método para procesar datos en Ethernet, circuito integrado de capa física y dispositivo de Ethernet, del 2 de Mayo de 2018, de HUAWEI TECHNOLOGIES CO., LTD.: Un método de procesamiento de datos de Ethernet, aplicable al procesamiento de datos en un extremo de transmisión, que comprende: * la realización de una codificación […]

Dispositivo de inspección de traducción de dirección, dispositivo de procesamiento central y procedimiento de inspección de traducción de dirección, del 17 de Enero de 2018, de MITSUBISHI HEAVY INDUSTRIES, LTD.: Un dispositivo de comprobación de traducción de dirección que comprende: una unidad de gestión de memoria de traducción entre una dirección virtual y una dirección […]

Procedimiento, dispositivo y sistema de almacenamiento distribuido, del 11 de Octubre de 2017, de HUAWEI TECHNOLOGIES CO., LTD.: Un procedimiento de almacenamiento distribuido, que comprende: dividir un archivo de datos para generar K segmentos de datos, dividir cada segmento de […]