CONVERTIDOR A/D MULTICANAL.

Convertidor A/D multicanal (10) para la conversión de varias señales de entrada analógicas (IN1 - IN n) en una señal de salida digital (OUT 1 - OUT n) correspondiente,

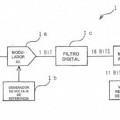

con un modulador ∑Δ(12) que comprende varios comparadores de entrada (14 1 - 14 n) asignados respectivamente a una señal de entrada (IN 1 - IN n), una unidad de muestreo (18) dispuesta después de éstos a través de un multiplexor (16) y un bucle de realimentación (24) que presenta un convertidor D/A (20) así como un filtro (22), a través del que la señal de salida de la unidad de muestreo (18) se reconduce a los comparadores de entrada (141 - 14 n), en el que los comparadores de entrada (14 1 - 14 n), el multiplexor (16), la unidad de muestreo (18) y el convertidor D/A (20) están realizados en una FPGA (26) y el filtro (22) está realizado como filtro analógico y está previsto fuera de la FPGA (26)

Tipo: Patente Europea. Resumen de patente/invención. Número de Solicitud: E08020314.

Solicitante: SICK AG.

Nacionalidad solicitante: Alemania.

Dirección: ERWIN-SICK-STRASSE 1 79183 WALDKIRCH/BREISGAU ALEMANIA.

Inventor/es: HUG,GOTTFRIED, Bohli,Alexander, Heindl,Jakob.

Fecha de Publicación: .

Fecha Solicitud PCT: 21 de Noviembre de 2008.

Clasificación Internacional de Patentes:

- H03M3/02 ELECTRICIDAD. › H03 CIRCUITOS ELECTRONICOS BASICOS. › H03M CODIFICACION, DECODIFICACION O CONVERSION DE CODIGO, EN GENERAL (por medio de fluidos F15C 4/00; convertidores ópticos analógico/digitales G02F 7/00; codificación, decodificación o conversión de código especialmente adaptada a aplicaciones particulares, ver las subclases apropiadas, p. ej. G01D, G01R, G06F, G06T, G09G, G10L, G11B, G11C, H04B, H04L, H04M, H04N; cifrado o descifrado para la criptografía o para otros fines que implican la necesidad de secreto G09C). › H03M 3/00 Conversión de valores analógicos en, o a partir de una modulación diferencial. › Modulación delta, es decir, modulación diferencial con un bit.

Clasificación PCT:

- H03M3/02 H03M 3/00 […] › Modulación delta, es decir, modulación diferencial con un bit.

Países PCT: Austria, Bélgica, Suiza, Alemania, Dinamarca, Francia, Reino Unido, Grecia, Italia, Liechtensein, Luxemburgo, Países Bajos, Suecia, Mónaco, Portugal, Irlanda, Eslovenia, Finlandia, Rumania, Chipre, Lituania, Letonia, Ex República Yugoslava de Macedonia, Albania.

PDF original: ES-2364867_T3.pdf

Fragmento de la descripción:

La invención se refiere a un convertidor A/D (convertidor analógico / digital) multicanal para la conversión de varias señales de entrada en una señal de salida digital correspondiente.

Si con una FPGA (Field Programmable Gate Array) se deben valorar magnitudes analógicas, como en particular tensiones y/o corrientes, entonces éstas se deben someter en primer lugar a una conversión analógica / digital. La posibilidad más sencilla de realizar una conversión semejante la ofrecen los IC (circuitos integrados) acabados, tal y como están disponibles en el mercado. No obstante, tales IC no son apropiados para muchas tareas sencillas del convertidor, debido a su necesidad de espacio en la tarjeta de circuitos impresos correspondiente, a la absorción de potencia, al gasto de comunicación que se produce para la FPGA y no en último lugar debido a sus elevados costes.

Para la conversión analógica / digital se conocen también ya el procedimiento de rampa simple o de doble rampa o de aproximaciones sucesivas (compárese, por ejemplo, el documento US 6,246,258 B1). Estos procedimientos traen consigo respecto a los IC convencionales una mejora respecto a los costes, la absorción de potencia y el gasto de comunicación. No obstante, debido a su elevada propensión a fallos no se pueden utilizar de forma razonable, por ejemplo, para las tareas de supervisión en sistemas relevantes en seguridad. Además, este procedimiento condiciona un proceso de decisión continuo, en el que las magnitudes perturbadoras analógicas provocan al inicio del proceso decisiones erróneas y por consiguiente errores considerables.

Otra posibilidad para la realización de una conversión digital / analógica se da con el procedimiento sigma – delta (∑∆) conocido. Este procedimiento ya se ha aplicado con coste diferente con elementos analógicos y digitales o de forma completamente integrada. En este caso se utiliza actualmente respectivamente un modulador ∑∆, en cuyo bucle de realimentación está previsto un integrador en forma de un amplificador de operación.

Del documento US 6,246,258 B1 se conoce además un así denominado convertidor A/D flash. No obstante, para la realización de un convertidor semejante se necesitan para n bits 2n – 1 comparadores. Para una resolución de 10 bits son necesarios 1023 comparadores, lo que va en contra de una conversión realista.

Entre los inconvenientes de los procedimientos o convertidores A/D conocidos cuentan por consiguiente en particular una propensión a fallos relativamente elevada, una resolución demasiado baja, una exactitud demasiado baja, tolerancias demasiado elevadas, una sensibilidad a la temperatura demasiado elevada, una absorción de potencia demasiado elevada, un consumo de recursos demasiado elevado en la FPGA, una necesidad de espacio demasiado elevada en la placa de circuitos impresos electrónicos (PCB, Printed Circuit Board), una cantidad de componentes relativamente grande, así como los costes relativamente elevados.

La invención tiene el objetivo de crear un convertidor A/D multicanal que se pueda aplicar utilizando lo mejor posible los recursos con una FGPA.

Este objetivo se resuelve según la invención con un convertidor A/D multicanal con las características de la reivindicación

1.

El convertidor A/D multicanal según la invención para la conversión de varias señales de entrada analógicas en una señal de salida digital correspondiente se caracteriza porque comprende un modulador ∑∆ con varios comparadores de entrada asignados respectivamente a una señal de entrada, una unidad de muestreo dispuesta después de estos a través de un multiplexor y un bucle de realimentación que presenta un convertidor D/A así como un filtro, a través del que la señal de salida de la unidad de muestreo se reconduce a los comparadores de entrada. A este respecto los comparadores de entrada, el multiplexor, la unidad de muestreo y el convertidor D/A están realizados en una FPGA, mientras que el filtro está realizado como filtro analógico y está previsto fuera de la FPGA.

Con este convertidor A/D multicanal que se basa en el principio ∑∆, se pueden medir y convertir varias señales de entrada con un coste en componentes muy pequeño, necesitándose para la realización solo una pequeña parte de la unidad lógica FPGA y un filtro analógico. Debido a la sencilla estructura se produce una forma económica, que ahorra recursos, espacio y energía de un convertidor A/D multicanal. En este caso con una buena calidad en la conversión se utilizan de forma óptima las cualidades de la FPGA en un sentido analógico y digital y el coste en componentes analógicos adicionales se mantiene bajo. Además se minimiza la tolerancia y la sensibilidad a la temperatura, así como se obtiene una elevada calidad de medición (linealidad y exactitud), elevada seguridad frente a fallos, en particular respecto a perturbaciones externas y una resolución elevada (poco ruido).

El convertidor A/D puede comprender una unidad de valoración para la valoración de la señal de salida de la unidad de muestreo. En este caso esta unidad de valoración también está realizada preferentemente en la FPGA.

La unidad de valoración está realizada preferiblemente para la promediación de la señal de salida de la unidad de muestreo durante un intervalo de tiempo predeterminable. Para ello puede comprender, por ejemplo, al menos un filtro FIR (FIR = Finite Impulse Response) y/o al menos un filtro CIC (CIC = Cascaded Integrator Comb).

La unidad de valoración puede estar realizada también en particular de forma que se cuentan los valores de exploración “1” que aparecen en una ventana de tiempo predeterminable correspondiente, correspondiendo el estado del contador que se produce al final de la ventana de tiempo con el resultado de la conversión.

Los filtros CIC ofrecen respecto a los filtros FIR un menor consumo de recursos, así como un tiempo de respuesta transitoria más breve. El recuento preferido correspondientemente de la señal que vuelve del comparador correspondiente es el más cuidadoso con los recursos, contándose cada “1” que aparece en una ventana de tiempo o ventana de medición determinada. El conteo se puede comenzar de forma síncrona al inicio de cada ventana de tiempo por una unidad de control y se puede interrumpir bruscamente al final. Después del desarrollo de la ventana de tiempo, el estado del contador se corresponde con el resultado de la conversión. La unidad de control puede conmutar al siguiente comparador y puede iniciar la siguiente ventana de tiempo tan pronto como el filtro analógico se ha estabilizado de forma segura. Una estructura del contador, potente, lo más rápida posible y que evite los fallos de sincronización en el diseño se obtiene en particular con dos contadores conectados en serie.

El convertidor A/D comprende convenientemente un demultiplexor dispuesto después de la unidad de valoración, que suministra las señales de salida digitales. En este caso este demultiplexor está realizado también en la FPGA.

Según se ha mencionado, el convertidor A/D comprende preferentemente también una unidad de control. Esta unidad de control también está realizada de nuevo en la FPGA.

La unidad de control puede estar prevista en particular para el control del multiplexor, para el control de la unidad de muestreo, para el control de la unidad de valoración y/o para el control del demultiplexor.

La unidad de control está realizada preferiblemente de forma que la señales de salida de los comparadores de entrada se suministran correspondientemente a la unidad de muestreo para una ventana de tiempo predeterminable, un inicio correspondiente de la unidad de muestreo se sincroniza con un inicio correspondiente de la unidad de valoración y/o el demultiplexor se controla correspondientemente para la emisión de la señales de salida digitales.

El filtro analógico previsto fuera de la FPGA puede comprender un filtro RC, comprendiendo preferentemente un filtro multipolar, en particular un filtro RC multipolar. El filtro analógico previsto fuera de la FPGA comprende preferentemente un filtro RC multipolar recursivo. En particular es ventajoso que comprenda un filtro RC cuadripolar recursivo, cuya toma esté prevista en particular después del tercer polo. Para la realización del filtro analógico se necesitan así sólo dos tipos de componentes o dos redes analógicas, así en particular cuatro elementos R idénticos... [Seguir leyendo]

Reivindicaciones:

1. Convertidor A/D multicanal (10) para la conversión de varias señales de entrada analógicas (IN1 – INn) en una señal de salida digital (OUT1 – OUTn) correspondiente, con un modulador ∑∆ (12) que comprende varios comparadores de entrada (141 – 14n) asignados respectivamente a una señal de entrada (IN1 – INn), una unidad de muestreo (18) dispuesta después de éstos a través de un multiplexor (16) y un bucle de realimentación (24) que presenta un convertidor D/A (20) así como un filtro (22), a través del que la señal de salida de la unidad de muestreo (18) se reconduce a los comparadores de entrada (141 – 14n), en el que los comparadores de entrada (141 – 14n), el multiplexor (16), la unidad de muestreo (18) y el convertidor D/A (20) están realizados en una FPGA (26) y el filtro (22) está realizado como filtro analógico y está previsto fuera de la FPGA (26).

2. Convertidor según la reivindicación 1, caracterizado porque comprende una unidad de valoración (28) para la valoración de la señal de salida de la unidad de muestreo (18).

3. Convertidor según la reivindicación 2, caracterizado porque la unidad de valoración (28) también está realizada en la FPGA (26).

4. Convertidor según la reivindicación 2 ó 3, caracterizado porque la unidad de valoración (28) está realizada para la promediación de la señal de salida de la unidad de muestreo (18) durante un intervalo de tiempo predeterminable.

5. Convertidor según una de las reivindicaciones precedentes, caracterizado porque la unidad de valoración (28) comprende al menos un filtro FIR y/o al menos un filtro CIC.

6. Convertidor según una de las reivindicaciones precedentes, caracterizado porque la unidad de valoración (28) está realizada de forma que se cuentan los valores de exploración “1” que aparecen en una ventana de tiempo predeterminable correspondiente, correspondiendo el estado del contador que se produce al final de la ventana de tiempo con el resultado de la conversión.

7. Convertidor según una de las reivindicaciones precedentes, caracterizado porque comprende una demultiplexor (32) dispuesto después de la unidad de valoración (28) y que suministra las señales de salida digitales (OUT1 – OUTn).

8. Convertidor según la reivindicación 7, caracterizado porque el demultiplexor (32) también está realizado en la FPGA (26).

9. Convertidor según una de las reivindicaciones precedentes, caracterizado porque comprende una unidad de control (30).

10. Convertidor según la reivindicación 9, caracterizado porque la unidad de control (30) también está realizada en la FPGA.

11. Convertidor según la reivindicación 9 ó 10, caracterizado porque la unidad de control (30) está prevista para el control del multiplexor (16), para el control de la unidad de muestreo (18), para el control de la unidad de valoración y/o para el control del demultiplexor (32).

12. Convertidor según la reivindicación 11, caracterizado porque la unidad de control (30) está realizada de forma que las señales de salida de los comparadores de salida (141 – 14n) se suministran respectivamente a la unidad de muestreo (18) para una ventana de tiempo predeterminable, un inicio correspondiente de la unidad de muestreo (18) se sincroniza con un inicio correspondiente de la unidad de valoración (28) y/o el demultiplexor (32) se controla correspondientemente para la emisión de las señales de salida digitales (OUT1 – OUTn).

13. Convertidor según una de las reivindicaciones precedentes, caracterizado porque el filtro analógico (22) previsto fuera de la FPGA (26) comprende un filtro RC, en particular un filtro RC multipolar.

14. Convertidor según la reivindicación 13, caracterizado porque el filtro analógico (22) previsto fuera de la FPGA (26) comprende un filtro RC multipolar recursivo.

15. Convertidor según la reivindicación 13 ó 14, caracterizado porque el filtro analógico (22) previsto fuera de la FPGA

(26) comprende un filtro RC cuadripolar recursivo, cuya toma está prevista en particular después del tercer polo.

Patentes similares o relacionadas:

Procedimiento para la adaptación de frecuencia automático de filtros durante el funcionamiento bucles de regulación cerrados, del 23 de Enero de 2019, de Albert-Ludwigs-Universität Freiburg: Procedimiento para la adaptación de la frecuencia de resonancia de un filtro de bucle en un modulador deltasigma a un valor de frecuencia predeterminado, […]

Modulador sigma-delta con pasabanda LC de tecnología mixta MEMS/BICMOS para muestreo de RF directo, del 18 de Abril de 2012, de RAYTHEON COMPANY: Modulador sigma-delta , que comprende: un primer DAC comprendido en un primer bucle de realimentación y un segundo DAC comprendido […]

CIRCUITO REGULADOR DE AMPLITUD DE UN SOLO BIT, del 3 de Mayo de 2011, de OSAKI ELECTRIC CO., LTD: Circuito regulador de amplitud de un solo bit.Para regular la amplitud de una señal digital salida de un convertidor A/D de un esquema de modulación {dl}{sg} […]

CIRCUITO REGULADOR DE AMPLITUD DE UN SOLO BIT, del 3 de Mayo de 2011, de OSAKI ELECTRIC CO., LTD: Circuito regulador de amplitud de un solo bit.Para regular la amplitud de una señal digital salida de un convertidor A/D de un esquema de modulación {dl}{sg} […]

CONVERTIDOR DE ANALOGO A DIGITAL SIGMA-DELTA CON MUESTREO MULTIPLE., del 16 de Mayo de 2007, de QUALCOMM INCORPORATED: Un convertidor analógico a digital sigma-delta, que comprende: al menos un bucle , con el bucle, o cada bucle configurado para recibir una señal […]

METODO Y DISPOSICION PARA SINCRONIZAR UN MODULADOR SIGMADELTA., del 16 de Agosto de 2006, de KONINKLIJKE PHILIPS ELECTRONICS N.V.: Método para sincronizar un modulador ÓÄ que comprende un filtro de paso bajo con estados del integrador y un cuantificador en una disposición de retroalimentación […]

CONVERSOR DIGITAL/ANALOGICO QUE GENERA FORMAS DE ONDA DE TIPO EXPONENCIAL DECRECIENTE PARA EL LAZO DE REALIMENTACION DE UN CONVERSOR SIGMA-DELTA DE TIEMPO CONTINUO., del 16 de Mayo de 2006, de UNIVERSIDAD DE VALLADOLID: El circuito conversor Digital/Analógico propuesto genera formas de onda de tipo exponencial decreciente para el lazo de realimentaci6n de un conversor Sigma-Delta […]

CIRCUITO DE SUPRESION DE RUIDO Y CONVERTIDOR REDUCTOR DE FRECUENCIA EN CUADRATURA., del 1 de Agosto de 2005, de QUALCOMM INCORPORATED: Circuito de supresión de ruido que comprende: por lo menos un diezmador pasabanda , comprendiendo cada diezmador pasabanda un filtro de supresión de errores […]

MÉTODO Y APARATO DE GENERACIÓN DE LA SEÑAL DE REALIMENTACIÓN EN CONVERTIDORES ANALÓGICO A DIGITAL SIGMA-DELTA, del 24 de Junio de 2011, de TELEFONAKTIEBOLAGET LM ERICSSON (PUBL): Un convertidor digital a analógico (DAC) para la generación de una señal de realimentación de conversión (ifb(t)) en un convertidor […]