CIRCUITO REGULADOR DE AMPLITUD DE UN SOLO BIT.

Circuito regulador de amplitud de un solo bit.Para regular la amplitud de una señal digital salida de un convertidor A/D de un esquema de modulación {dl}{sg} que tiene una resolución de N bits con un valor de regulación de amplitud que tiene M dígitos,

dado que se debe realizar multiplicaciones de NxM bits, un multiplicador se incrementa en escala, y requiere un número de elementos de circuito y una zona de montaje grande. Una señal de entrada (X) de un modulador {dl}{sg}(2a), representada por una señal de un bit y que sigue siendo la señal de un bit, es multiplicada por un valor de regulación de amplitud de 11 dígitos salido de un registro de valor de regulación de amplitud (2d) por un multiplicador de un solo bit (2c) para regular su amplitud. Así, la amplitud puede ser regulada sin realizar multiplicaciones de una señal de 16 bits (N-bits) o multi-bit con un valor de regulación de amplitud de 11 dígitos (M dígitos) (16x11) como antes. Como resultado, es posible reducir el número de elementos de circuito que incluyen el multiplicador (2c) para reducir la escala de circuito del circuito regulador de amplitud por un factor de N

Tipo: Patente de Invención. Resumen de patente/invención. Número de Solicitud: P200802050.

Solicitante: OSAKI ELECTRIC CO., LTD.

Nacionalidad solicitante: Japón.

Dirección: 2-7 HIGASHI-GOTANDA 2-CHOME SHINAGAWA-KU-TOKYO 141-8646 JAPON.

Inventor/es: OHHIRA,TAKEO, AIKYO,YASUAKI, KAWASHIMA,NAOTO, GO,KAZUNORI.

Fecha de Solicitud: 9 de Julio de 2008.

Fecha de Publicación: .

Fecha de Concesión: 18 de Abril de 2011.

Clasificación Internacional de Patentes:

- H03M3/02 ELECTRICIDAD. › H03 CIRCUITOS ELECTRONICOS BASICOS. › H03M CODIFICACION, DECODIFICACION O CONVERSION DE CODIGO, EN GENERAL (por medio de fluidos F15C 4/00; convertidores ópticos analógico/digitales G02F 7/00; codificación, decodificación o conversión de código especialmente adaptada a aplicaciones particulares, ver las subclases apropiadas, p. ej. G01D, G01R, G06F, G06T, G09G, G10L, G11B, G11C, H04B, H04L, H04M, H04N; cifrado o descifrado para la criptografía o para otros fines que implican la necesidad de secreto G09C). › H03M 3/00 Conversión de valores analógicos en, o a partir de una modulación diferencial. › Modulación delta, es decir, modulación diferencial con un bit.

Clasificación PCT:

- H03M3/02 H03M 3/00 […] › Modulación delta, es decir, modulación diferencial con un bit.

Fragmento de la descripción:

Circuito regulador de amplitud de un solo bit.

Antecedentes de la invención

La presente invención se refiere a un circuito regulador de amplitud de un solo bit para regular la amplitud de una señal representada por una entrada de señal de un bit de un modulador ΔΣ o análogos mediante procesado operativo de un solo bit.

Un convertidor A/D (analógico a digital) de un esquema de modulación ΔΣ envía un valor digital que representa la relación de un valor de voltaje de una señal analógica de entrada a un valor de voltaje de referencia del convertidor A/D. Consiguientemente, un valor a escala completa descrito en el funcionamiento del convertidor A/D depende del valor absoluto del voltaje de referencia. También, un valor analógico introducido en el convertidor A/D es calculado a partir de un valor digital salido del convertidor A/D y el valor a escala completa descrito en el funcionamiento del convertidor A/D. Como tal, se necesita un valor preciso a escala completa con el fin de calcular exactamente el valor analógico introducido en el convertidor A/D. Realmente, sin embargo, el valor a escala completa puede incluir errores porque las relaciones de los condensadores y análogos, que son elementos analógicos, tienen que constituir una sección integradora del convertidor A/D del esquema de modulación ΔΣ, y estos elementos analógicos tienen limitaciones en la exactitud de los valores absolutos. En consecuencia, con el fin de calcular exactamente el valor analógico introducido en el convertidor A/D, hay que conocer de antemano un valor real a escala completa, en lugar del valor a escala completa descrito en el funcionamiento del convertidor A/D, o la amplitud debe ser regulada para encaje en una escala completa definida. Convencionalmente, hay dos métodos de regular la amplitud.

Un primer método implica hacer variable un voltaje de referencia de un convertidor A/D usando un circuito analógico, y regular el voltaje de referencia de tal manera que un valor a escala completa tome un valor deseado.

Un segundo método implica multiplicar un valor digital salido de un convertidor A/D por un valor de regulación de amplitud predeterminado usando un multiplicador digital de tal manera que un valor digital salido del convertidor A/D presente una resolución deseada a un valor deseado.

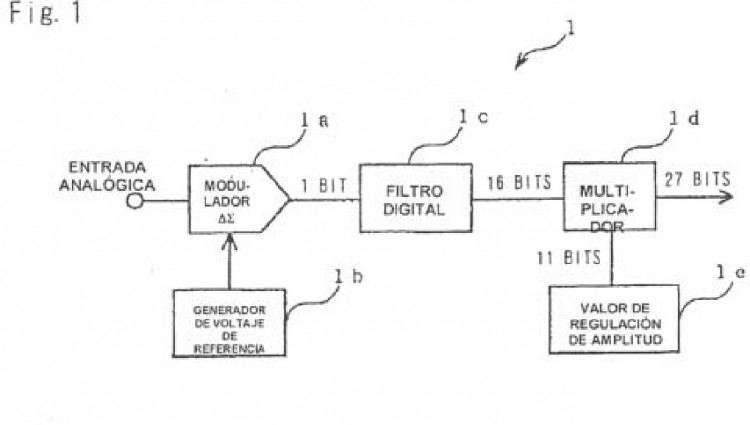

La figura 1 es un diagrama de bloques que representa la configuración de un convertidor A/D 1 del esquema de modulación ΔΣ que emplea un circuito regulador de amplitud convencional para regular la amplitud de una salida usando el segundo método. Este convertidor A/D 1 incluye un modulador ΔΣ 1a, un generador de voltaje de referencia 1b, un filtro digital le, un multiplicador 1d, y un registro de valor de regulación de amplitud 1e. Una señal analógica introducida en el convertidor A/D 1 es convertida a una señal digital de un bit (una señal representada por un valor binario "+1" o "-1", que a continuación se denomina la "señal de un bit") por el modulador ΔΣ 1a con referencia a un voltaje de referencia salido del generador de voltaje de referencia 1b. La señal de un bit salida es convertida a un valor digital representado por una señal digital multi-bit (por ejemplo, 16 bits) (a continuación denominada la "señal multi-bit") por el filtro digital le según la escala completa. El valor digital de salida es multiplicado por un valor de regulación de amplitud que tiene una pluralidad de dígitos, que se pone en el registro de valor de regulación de amplitud 1e, en el multiplicador 1d, y se regula de tal manera que el valor a escala completa presente una resolución deseada a un valor deseado. Aquí, el multiplicador 1d y el registro de valor de regulación de amplitud 1e incluyen un circuito regulador de amplitud de salida del convertidor A/D 1. Dado que hay tendencia a poner menos circuitos analógicos desde el punto de vista de la reducción del costo, el segundo método se emplea principalmente como un método de regulación de amplitud en lugar del primer método que se emplea menos frecuentemente debido al uso del circuito analógico.

Se describen circuitos de proceso de un solo bit usando dicho modulador ΔΣ 1a en el documento de Patente 1 y el documento de Patente 2 siguientes:

Documento de Patente 1: JP-2001-94430-A

Documento de Patente 2: JP-2005-303944-A

El convertidor A/D del esquema de modulación ΔΣ es un medio efectivo para enviar una señal analógica de entrada como una señal digital a alta resolución. Los convertidores A/D comercialmente disponibles del esquema de modulación ΔΣ incluyen los productos que producen señales digitales representadas por 16 bits o más de 20 bits, en algunos casos, a altas resoluciones.

Para realizar una escala completa deseada mediante una regulación de la amplitud de la salida de un convertidor A/D que tiene dicha resolución, un multiplicador requerido para un circuito regulador de amplitud se determina de la siguiente manera. Por ejemplo, en la figura 1, la señal de un bit salida del modulador ΔΣ 1a es convertida a un valor digital de 16 bits por el filtro digital 1e. Cuando la amplitud de esta salida es regulada de manera que se incremente un factor de cero a dos, es decir, en 200 pasos en incrementos de 1% desde 0% a 200%, el multiplicador 1d tiene que realizar una multiplicación de 16 bits por 8 bits, donde el valor de regulación de amplitud en el registro de valor de regulación de amplitud se pone a ocho dígitos (28=256). Si la amplitud es regulada en 2000 pasos en incrementos de 0,1% para un rendimiento más alto, el multiplicador 1d tiene que realizar una multiplicación de 16 bits por 11 bits, donde el valor de regulación de amplitud en el registro de valor de regulación de amplitud 1e se pone a 11 dígitos (211=2048). Este multiplicador 1d necesita 176 (=16x11) puertas Y y 176 sumadores plenos.

Generalmente, en un convertidor A/D de la un esquema de modulación ΔΣ que tiene una resolución de N bits, cuando la amplitud es regulada con un valor de regulación de amplitud de M dígitos en el registro de valor de regulación de amplitud 1e, se requiere un multiplicador para realizar una multiplicación de N bits por M bits. En este caso, este amplificador necesita simplemente NxM puertas Y y sumadores plenos. Consiguientemente, con una resolución más alta y un valor de regulación de amplitud mayor que implican mayores valores de N y M, un multiplicador resultante tiene una mayor escala y requiere más elementos de circuito y una zona de montaje más grande.

Resumen de la invención

La presente invención se ha realizado con el fin de resolver el problema indicado anteriormente, y proporciona un circuito regulador de amplitud de un solo bit que incluye un registro de valor de regulación de amplitud que tiene un número de dígitos que representa un valor de regulación de amplitud para regular la amplitud de una señal de entrada, y un multiplicador de un solo bit para multiplicar la señal de entrada representada por una señal de un bit por el valor de regulación de amplitud salido del registro de valor de regulación de amplitud para enviar el resultado de la multiplicación en forma de una señal de un bit.

Según esta configuración, una señal de entrada de un modulador ΔΣ, representada por una señal de un bit y que sigue siendo la señal de un bit, es multiplicada por un valor de regulación de amplitud salido del registro de valor de regulación de amplitud por el multiplicador de un solo bit para regular su amplitud. Así, la amplitud puede ser regulada sin realizar multiplicaciones de una señal de N bits o multi-bit con un valor de regulación de amplitud de M dígitos (NxM) como antes, haciendo así posible reducir el número de elementos de circuito que incluyen el multiplicador para reducir la escala de circuito del circuito regulador de amplitud en un factor de N.

Además, en la presente invención, el multiplicador de un solo bit incluye una pluralidad de circuitos 0 lógico exclusivo para procesar un 0 lógico exclusivo de la señal de entrada con cada dígito del valor de regulación de amplitud salido del registro de valor de regulación de amplitud, y una pluralidad de sumadores de un solo bit conectados en múltiples etapas para añadir salidas de los circuitos O lógico exclusivo, donde los sumadores de un solo bit realizan procesado de adición para...

Reivindicaciones:

1. Un circuito regulador de amplitud de un solo bit incluyendo:

un registro de valor de regulación de amplitud (2d) que tiene un número de dígitos que representa un valor de regulación de amplitud para regular la amplitud de una señal de entrada; y

un multiplicador de un solo bit (2c) para multiplicar la señal de entrada representada por una señal de un bit por el valor de regulación de amplitud salido de dicho registro de valor de regulación de amplitud para obtener el resultado de la multiplicación en forma de una señal de un bit.

2. Un circuito regulador de amplitud de un solo bit según la reivindicación 1, donde:

dicho multiplicador de un solo bit incluye:

una pluralidad de circuitos O lógico exclusivo (31a-31k) para procesar un O lógico exclusivo de la señal de entrada con cada dígito del valor de regulación de amplitud salido de dicho registro de valor de regulación de amplitud; y

una pluralidad de sumadores de un solo bit (32a-32k) conectados en múltiples etapas para añadir salidas de dichos circuitos O lógico exclusivo,

donde dichos sumadores de un solo bit realizan procesado de adición para una señal que es duplicada en la misma etapa que el procesado de adición con una señal de un bit que es aplicada con un peso predeterminado según el número de duplicaciones de la señal, sin usar una pluralidad de sumadores de un solo bit en la misma etapa, en un sumador de un solo bit en una etapa posterior.

3. Un circuito regulador de amplitud de un solo bit según la reivindicación 2, donde dicho sumador de un solo bit determina z(n) y Q(n) por:

z(n) = x(n-1)+y(n-1))/2

Q(n) = Q(n-1)

cuando x(n)=y(n), y por

z(n) = Q(n-1)

Q(n) = Q(n-1)x(-1)

cuando x(n)

4. Un circuito regulador de amplitud de un solo bit según cualquiera de las reivindicaciones 1 a 3, donde dicha señal de entrada es una señal de salida de un modulador ΔΣ (2a) para convertir una señal analógica a una señal digital de un bit mediante modulación ΔΣ.

5. Un circuito regulador de amplitud de un solo bit según cualquiera de las reivindicaciones 1 a 3, donde dicha señal de entrada representa el resultado de una multiplicación de bits únicos en respectivas salidas de dos moduladores ΔΣ (2a1, 2a2) para convertir una señal analógica a una señal digital de un bit mediante modulación ΔΣ.

Patentes similares o relacionadas:

Procedimiento para la adaptación de frecuencia automático de filtros durante el funcionamiento bucles de regulación cerrados, del 23 de Enero de 2019, de Albert-Ludwigs-Universität Freiburg: Procedimiento para la adaptación de la frecuencia de resonancia de un filtro de bucle en un modulador deltasigma a un valor de frecuencia predeterminado, […]

Modulador sigma-delta con pasabanda LC de tecnología mixta MEMS/BICMOS para muestreo de RF directo, del 18 de Abril de 2012, de RAYTHEON COMPANY: Modulador sigma-delta , que comprende: un primer DAC comprendido en un primer bucle de realimentación y un segundo DAC comprendido […]

CONVERTIDOR A/D MULTICANAL, del 15 de Septiembre de 2011, de SICK AG: Convertidor A/D multicanal para la conversión de varias señales de entrada analógicas (IN1 - IN n) en una señal de salida digital (OUT 1 - OUT n) correspondiente, […]

CONVERTIDOR DE ANALOGO A DIGITAL SIGMA-DELTA CON MUESTREO MULTIPLE., del 16 de Mayo de 2007, de QUALCOMM INCORPORATED: Un convertidor analógico a digital sigma-delta, que comprende: al menos un bucle , con el bucle, o cada bucle configurado para recibir una señal […]

METODO Y DISPOSICION PARA SINCRONIZAR UN MODULADOR SIGMADELTA., del 16 de Agosto de 2006, de KONINKLIJKE PHILIPS ELECTRONICS N.V.: Método para sincronizar un modulador ÓÄ que comprende un filtro de paso bajo con estados del integrador y un cuantificador en una disposición de retroalimentación […]

CONVERSOR DIGITAL/ANALOGICO QUE GENERA FORMAS DE ONDA DE TIPO EXPONENCIAL DECRECIENTE PARA EL LAZO DE REALIMENTACION DE UN CONVERSOR SIGMA-DELTA DE TIEMPO CONTINUO., del 16 de Mayo de 2006, de UNIVERSIDAD DE VALLADOLID: El circuito conversor Digital/Analógico propuesto genera formas de onda de tipo exponencial decreciente para el lazo de realimentaci6n de un conversor Sigma-Delta […]

CIRCUITO DE SUPRESION DE RUIDO Y CONVERTIDOR REDUCTOR DE FRECUENCIA EN CUADRATURA., del 1 de Agosto de 2005, de QUALCOMM INCORPORATED: Circuito de supresión de ruido que comprende: por lo menos un diezmador pasabanda , comprendiendo cada diezmador pasabanda un filtro de supresión de errores […]

MÉTODO Y APARATO DE GENERACIÓN DE LA SEÑAL DE REALIMENTACIÓN EN CONVERTIDORES ANALÓGICO A DIGITAL SIGMA-DELTA, del 24 de Junio de 2011, de TELEFONAKTIEBOLAGET LM ERICSSON (PUBL): Un convertidor digital a analógico (DAC) para la generación de una señal de realimentación de conversión (ifb(t)) en un convertidor […]