ARQUITECTURA DE MEMORIA PARA DECODIFICADOR DE PROBABILIDAD MAXIMA A POSTERIORI.

Un sistema para llevar a cabo una decodificación de la probabilidad máxima a posteriori en ventana desplazable,

en lo sucesivo denominada MAP, comprendiendo la decodificación:

a) una RAM (160) de desentrelazado de canal para almacenar un bloque de estimaciones de símbolos;

b) un total de S calculadores (272, 274) de métricas de estado, siendo cada calculador de métricas de estado para generar un conjunto de cálculos métricos de estado, en el que dichos calculadores (272, 274) de métricas de estado procesan datos en ventanas iguales o menores que el tamaño de una RAM de ventana;

c) un conjunto de S+1 RAM (230A-D) de ventana, en el que S de dichas S+1 RAM de ventana proporcionan estimaciones de símbolos a dichos S calculadores de métricas de estado, y una RAM restante de ventana recibe estimaciones de símbolos desde dicha RAM (160) de desentrelazado de canal

Tipo: Patente Internacional (Tratado de Cooperación de Patentes). Resumen de patente/invención. Número de Solicitud: PCT/US99/18550.

Solicitante: QUALCOMM INCORPORATED.

Nacionalidad solicitante: Estados Unidos de América.

Dirección: 5775 MOREHOUSE DRIVE,SAN DIEGO, CA 92121-1714.

Inventor/es: HALTER,STEVEN,J.

Fecha de Publicación: .

Fecha Concesión Europea: 28 de Julio de 2010.

Clasificación Internacional de Patentes:

- H03M13/29T

- H03M13/39A

- H03M13/45 ELECTRICIDAD. › H03 CIRCUITOS ELECTRONICOS BASICOS. › H03M CODIFICACION, DECODIFICACION O CONVERSION DE CODIGO, EN GENERAL (por medio de fluidos F15C 4/00; convertidores ópticos analógico/digitales G02F 7/00; codificación, decodificación o conversión de código especialmente adaptada a aplicaciones particulares, ver las subclases apropiadas, p. ej. G01D, G01R, G06F, G06T, G09G, G10L, G11B, G11C, H04B, H04L, H04M, H04N; cifrado o descifrado para la criptografía o para otros fines que implican la necesidad de secreto G09C). › H03M 13/00 Codificación, decodificación o conversión de código para detectar o corregir errores; Hipótesis básicas sobre la teoría de codificación; Límites de codificación; Métodos de evaluación de la probabilidad de error; Modelos de canal; Simulación o prueba de códigos (detección o correción de errores para la conversión de código o la conversión analógico/digital, digital/analógica H03M 1/00 - H03M 11/00; especialmente adaptados para los computadores digitales G06F 11/08; para el registro de la información basado en el movimiento relativo entre el soporte de registro y el transductor G11B, p. ej. G11B 20/18; para memorias estáticas G11C). › Decodificación discreta, es decir, usando información de fiabilidad de los símbolos (H03M 13/41 tiene prioridad).

Clasificación PCT:

- H03M13/39 H03M 13/00 […] › Estimación de secuencia, es decir, usando métodos estadísticos para la reconstrucción de los códigos originales.

Clasificación antigua:

- H03M13/00 H03M […] › Codificación, decodificación o conversión de código para detectar o corregir errores; Hipótesis básicas sobre la teoría de codificación; Límites de codificación; Métodos de evaluación de la probabilidad de error; Modelos de canal; Simulación o prueba de códigos (detección o correción de errores para la conversión de código o la conversión analógico/digital, digital/analógica H03M 1/00 - H03M 11/00; especialmente adaptados para los computadores digitales G06F 11/08; para el registro de la información basado en el movimiento relativo entre el soporte de registro y el transductor G11B, p. ej. G11B 20/18; para memorias estáticas G11C).

Fragmento de la descripción:

Arquitectura de memoria para decodificador de probabilidad máxima a posteriori.

I. Campo de la invención

La presente invención versa acerca de la codificación. Más en particular, la presente invención versa acerca de una técnica novedosa y mejorada para llevar a cabo una decodificación de la probabilidad máxima a posteriori (MAP) en ventana desplazable.

II. Descripción de la técnica relacionada

La "turbocodificación" representa un importante avance en el área de la corrección anticipada de errores (FEC). Hay muchas variantes de la turbocodificación, pero la mayoría utiliza múltiples etapas de codificación separadas por etapas de entrelazado combinadas con decodificación iterativa. Esta combinación proporciona un rendimiento no disponible previamente con respecto a la tolerancia al ruido en un sistema de comunicaciones. Es decir, la turbocodificación permite comunicaciones con niveles de Eb/N0 que eran previamente inaceptables usando las técnicas existentes de corrección anticipada de errores.

Hay muchos sistemas que usan técnicas de corrección anticipada de errores, y, por lo tanto, se beneficiarían del uso de la turbocodificación. Por ejemplo, los turbocódigos podrían mejorar el rendimiento de los enlaces inalámbricos por satélite, en los que la limitada potencia de transmisión del enlace descendente del satélite necesita sistemas receptores que puedan operar a bajos niveles de Eb/N0. El uso de turbocódigos en un enlace inalámbrico por satélite podría reducir el tamaño de la antena parabólica para un sistema de transmisión digital de vídeo (DVB) o, alternativamente, permitir que se transmitieran más datos dentro de un ancho de banda dado de frecuencias.

Los sistemas de telecomunicaciones inalámbricas digitales, como los sistemas telefónicos móvil digital y PCS, también usan la corrección anticipada de errores. Por ejemplo, el estándar de interfaz aérea IS-95 y sus derivados, como el IS-95B, definen un sistema de comunicaciones inalámbricas digitales que usa una codificación convencional para proporcionar una ganancia de codificación para aumentar la capacidad del sistema. En la patente estadounidense nº 5.103.459, titulada "System and Method for Generating Signal Waveforms in a CDMA Cellular Telephone System", transferida al cesionario de la presente invención (patente 5.103.459), se describe un sistema y un procedimiento para el procesamiento de señales de RF sustancialmente según el uso del estándar IS-95.

Dado que los sistemas de comunicaciones inalámbricas digitales como el IS-95 son fundamentalmente para comunicaciones móviles, es importante contar con dispositivos que minimicen el uso de energía y que sean pequeños y ligeros. Típicamente, esto requiere el desarrollo de un circuito integrado semiconductor ("chip") para llevar a cabo la mayor parte o la totalidad del procesamiento necesario. Aunque la codificación convolucional es relativamente compleja, los circuitos necesarios para llevar a cabo la codificación y la decodificación convolucionales pueden formarse en un único chip junto con cualquier otra circuitería necesaria.

La turbocodificación (en particular la operación de decodificación) es significativamente más compleja que la codificación (y la decodificación) convolucional. No obstante, sería sumamente deseable incluir la turbocodificación en los sistemas de telecomunicaciones inalámbricas digitales, incluyendo los sistemas de comunicaciones digitales móviles y el sistema de comunicaciones por satélite. Así, la presente invención se dirige al aumento de la velocidad con la que pueden llevarse a cabo ciertas operaciones para facilitar el uso de la turbocodificación en una variedad de sistemas.

Se llama, además, la atención al documento titulado "An intuitive justification and a simplified implementation of the MAP decoder for convolutional codes", de Viterbi A J, IEEE Journal on selected areas in communications, US, IEEE INC Nueva York, vol. 16, nº 2, páginas 260-264, XP000741780. El documento expone el uso de decodificadores MAP para códigos convolucionales y también aplica técnicas de gestión de la memoria similares a las usadas para los códigos convolucionales ordinarios.

También se llama la atención al documento de G. Fettweiss y H. Meyr titulado "Feedforward Architectures for Parallel Viterbi Decoding", Journal on VLSI signal processing, vol. 3, nº 2, junio de 1991, páginas 105-119, XP000228897. El documento expone, en el contexto de la decodificación de Viterbi, que dejando de procesar recursivamente una realimentación ACS pueden diseñarse arquitecturas puramente de alimentación directa para la decodificación De Viterbi.

Por último, se llama la atención a la publicación de DAWID H; MEYR H.: "Real-Time Algorithms and VLSI Architectures for Soft Output MAP Convolutional Decoding" PROC. OF PERSONAL, INDOOR AND MOBILE RADIO CONFERENCE (PIMRC) 1995 vol. 1, 27 de septiembre de 1995, ONTARIO, CANADÁ, páginas 193 - 197, XP002176458.

Resumen de la invención

En el contexto de la presente invención, se proporcionan un sistema y un procedimiento para llevar a cabo una decodificación de la probabilidad máxima a posteriori en ventana desplazable según se expone en las reivindicaciones 1 y 9. Las realizaciones de la presente invención se describen en las reivindicaciones dependientes.

La presente invención es una técnica novedosa y mejorada para la técnica de la decodificación con aplicación particular a las técnicas de turbocodificación o de codificación iterativa. Según una realización de la invención, un sistema de decodificación incluye una RAM de desentrelazado de canal para almacenar un bloque de estimaciones de símbolos, un conjunto de S calculadores de métricas de estado. Cada calculador de métricas de estado es para generar un conjunto de cálculos de métricas de estado y un conjunto de S+1 RAM de ventana, en el que S de dichas S+1 RAM de ventana proporcionan estimaciones de símbolos a dichos S calculadores de métricas de estado. Una RAM restante de ventana recibe estimaciones de símbolos desde dicha RAM de desentrelazado de canal.

Breve descripción de los dibujos

Las características, los objetos y las ventajas de la presente invención se harán más evidentes a partir de la descripción detallada expuesta más abajo cuando se la toma en conjunto con los dibujos, en los que los caracteres de referencia similares identifican partes correspondientes en el conjunto y en los que:

las Figuras 1A y 1B son diagramas de bloques de sistemas de comunicaciones inalámbricas;

la Fig. 2 es un diagrama de bloques de un sistema de transmisión;

las Figuras 3A y 3B son diagramas de turbocodificadores;

la Fig. 4 es un diagrama de bloques de un sistema de procesamiento de recepción;

la Fig. 5 es un diagrama de bloques de un decodificador y una porción de un desentrelazador de canal;

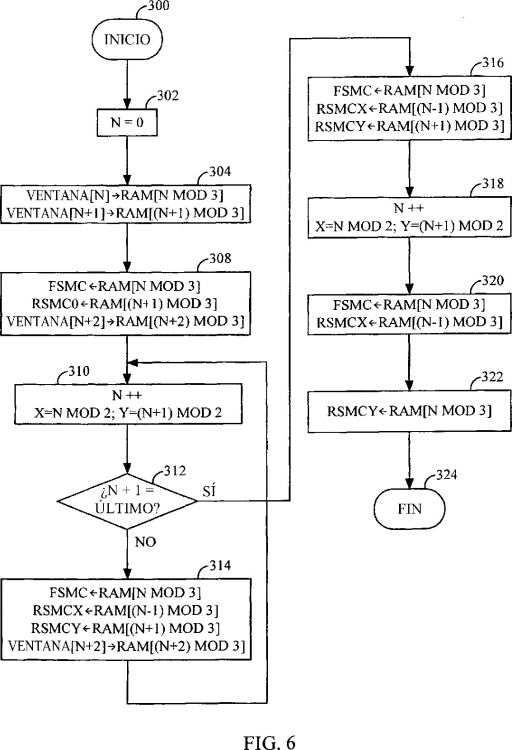

la Fig. 6 es un diagrama de flujo que ilustra un conjunto ejemplar de etapas de decodificación.

Descripción detallada de las realizaciones preferidas

La presente invención es una técnica novedosa y mejorada para llevar a cabo una turbocodificación. La realización ejemplar se describe en el contexto del sistema de telefonía móvil digital. Aunque el uso dentro de este contexto es ventajoso, pueden incorporarse diferentes realizaciones de la invención en diferentes entornos, configuraciones o sistemas digitales de transmisión de datos, incluyendo sistemas de comunicaciones por satélite y sistemas de comunicaciones mediante cable físico, como los sistemas de cable digital y de telefonía.

En general, los diversos sistemas descritos en el presente documento pueden formarse usando procesadores controlados por software, circuitos integrados o lógica discreta; sin embargo, se prefiere la implementación en un circuito integrado. Los datos, las instrucciones, las órdenes, la información, las señales, los símbolos y los chips a los que se puede hacer referencia en la solicitud son representados con ventaja por tensiones, corrientes, ondas electromagnéticas, campos o partículas magnéticos, campos o partículas ópticos, o una combinación de los mismos. Además, los bloques mostrados en cada diagrama de bloques pueden representar o bien hardware o bien etapas del procedimiento.

La Fig. 1A es un diagrama muy simplificado de un sistema telefónico móvil configurado según una realización de la...

Reivindicaciones:

1. Un sistema para llevar a cabo una decodificación de la probabilidad máxima a posteriori en ventana desplazable, en lo sucesivo denominada MAP, comprendiendo la decodificación:

2. El sistema según la reivindicación 1 en el que S es igual a 3.

3. El sistema según la reivindicación 1 en el que dichas RAM (230A-D) de ventana son menores que dicha RAM (160) de desentrelazado de canal.

4. El sistema según la reivindicación 1 que comprende un decodificador, comprendiendo dicho decodificador:

una memoria de entrelazado de canal para almacenar un bloque de entrelazado de canal de estimaciones de recepción, comprendiendo dicha memoria dicha RAM (160) de desentrelazado de canal;

un procesador (270) de decodificación para decodificar las estimaciones de recepción, comprendiendo dicho procesador (270) de decodificación los S calculadores (272, 274) de métricas de estado;

una memoria intermedia de decodificación que comprende dicho conjunto de S+1 RAM (230A-D) de ventana, siendo dicha memoria intermedia de decodificación para leer de salida, simultáneamente, un primer conjunto de estimaciones de recepción y un segundo conjunto de estimaciones de recepción a dicho procesador (270) de decodificación y escribir de entrada un tercer conjunto de estimaciones de recepción procedentes de dicha memoria de entrelazado de canal.

5. El sistema según la reivindicación 4 en el que dicha memoria intermedia de decodificación es, además, para leer de salida un cuarto conjunto de estimaciones de recepción.

6. El sistema según la reivindicación 4 en el que dicho procesador (270) de decodificación es un procesador de decodificación MAP.

7. El sistema según la reivindicación 4 en el que dicho procesador (270) de decodificación comprende:

un calculador de métricas directas de estado para generar métricas de estado directas en respuesta a dicho primer conjunto de estimaciones de recepción;

un calculador de métricas inversas de estado para generar métricas de estado inversas en respuesta a dicho segundo conjunto de estimaciones de recepción.

8. El sistema según la reivindicación 5 en el que dicho procesador (270) de decodificación comprende:

un calculador de métricas directas de estado para generar métricas de estado directas en respuesta a dicho primer conjunto de estimaciones de recepción;

un primer calculador de métricas inversas de estado para generar métricas de estado inversas en respuesta a dicho segundo conjunto de estimaciones de recepción; y

un segundo calculador de métricas inversas de estado para generar métricas de estado inversas en respuesta a dicho cuarto conjunto de estimaciones de recepción.

9. Un procedimiento para llevar a cabo una decodificación de la probabilidad máxima a posteriori en ventana desplazable, en lo sucesivo denominada MAP, comprendiendo el procedimiento:

Patentes similares o relacionadas:

Método, aparato y sistema para retroalimentar la decodificación de detención temprana, del 1 de Julio de 2020, de ZTE CORPORATION: Un método para retroalimentar un resultado de decodificación de la decodificación de detención temprana, caracterizado porque comprende: en un intervalo de tiempo […]

Uso de decisiones de bits fáciles para mejorar la desmodulación DPSK de datos SPS, del 30 de Abril de 2019, de QUALCOMM INCORPORATED: Un procedimiento de desmodulación de datos, dicho procedimiento que comprende: proporcionar una primera señal de entrada que comprende una palabra de […]

Procedimiento para la transmisión de datos para canales con propiedades de transmisión rápidamente variables, del 27 de Marzo de 2019, de MBDA Deutschland GmbH: Procedimiento para determinar una métrica de selección en un sistema de transmisión de datos con una unidad de emisión y una unidad de recepción […]

Procedimientos que emplean códigos de FEC con inactivación permanente de símbolos para procesos de codificación y decodificación, del 2 de Mayo de 2018, de QUALCOMM INCORPORATED: Un procedimiento de transmisión electrónica de datos a través de uno o más transmisores capaces de emitir una señal electrónica, en donde los datos a transmitir […]

Corrección de errores con prueba de varias longitudes para una trama de datos, del 2 de Noviembre de 2016, de GRDF: Procedimiento de recepción de datos digitales transmitidos por tramas utilizando una codificación de control de integridad mediante el cual, antes […]

Método y equipo de procesamiento de señalización, y receptor de señal, del 23 de Marzo de 2016, de HUAWEI TECHNOLOGIES CO., LTD.: Un método de procesamiento de señal, que comprende:

detectar (S1), de acuerdo con una regla de comprobación establecida durante la codificación […]

Método y equipo de procesamiento de señalización, y receptor de señal, del 23 de Marzo de 2016, de HUAWEI TECHNOLOGIES CO., LTD.: Un método de procesamiento de señal, que comprende:

detectar (S1), de acuerdo con una regla de comprobación establecida durante la codificación […]

Método de codificación de corrección de errores, método de decodificación y dispositivos asociados, del 25 de Junio de 2014, de Airbus DS SAS: Método de codificación de corrección de errores para codificar en serie datos digitales de origen, que tienen la forma de una […]

Método de codificación de corrección de errores, método de decodificación y dispositivos asociados, del 25 de Junio de 2014, de Airbus DS SAS: Método de codificación de corrección de errores para codificar en serie datos digitales de origen, que tienen la forma de una […]

Método de codificación de corrección de errores, método de decodificación y dispositivos asociados, del 25 de Junio de 2014, de Airbus DS SAS: Método de codificación de corrección de errores para codificar en paralelo datos digitales denominados de origen, que tienen la […]

Método de codificación de corrección de errores, método de decodificación y dispositivos asociados, del 25 de Junio de 2014, de Airbus DS SAS: Método de codificación de corrección de errores para codificar en paralelo datos digitales denominados de origen, que tienen la […]