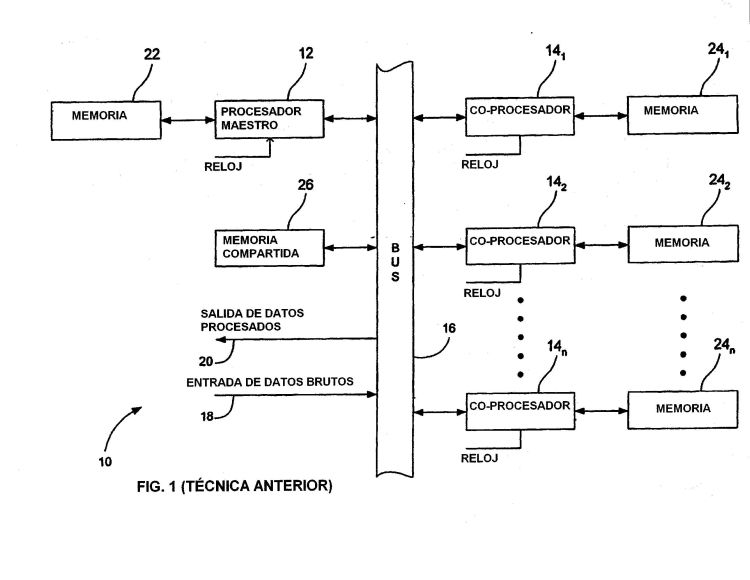

COPROCESADOR CANALIZADO.

Máquina de transferencia de vectores entre entidades pares (40),

que comprende: un procesador central (42) que se puede hacer funcionar para ejecutar un programa, y, en respuesta al programa, se puede hacer funcionar para generar unos primeros datos principales; un acelerador de canalización (44) que comprende canalizaciones de conexiones permanentes y que está acoplado al procesador central (42) y que se puede hacer funcionar para recibir los primeros datos principales y para generar unos primeros datos de canalización a partir de los primeros datos principales, presentando el acelerador de canalización unas interconexiones internas configurables y una memoria de microprograma (52) que se puede hacer funcionar para almacenar un microprograma de configuración para configurar las interconexiones internas, caracterizada porque la máquina de vectores entre pares (40) comprende además un registro de configuración (70) del acelerador acoplado al procesador central (42) y que se puede hacer funcionar para almacenar información de configuración del acelerador de canalización que es independiente con respecto al programa, y el procesador central (42) se puede hacer funcionar para recibir la información de configuración a partir del registro (70) y para configurar el acelerador de canalización (44) con vistas a generar los primeros datos de canalización mediante el suministro de la información de configuración al acelerador de canalización antes de ejecutar el programa descargando la información de configuración en la memoria del microprograma, y porque se proporciona un único bus (50) para la comunicación del procesador central con el acelerador de canalización y el procesador central y el acelerador de canalización se comunican a través de mensajes que comprenden los primeros datos principales y un encabezamiento que contiene la canalización de conexiones permanentes deseada de destino de los datos.

Tipo: Resumen de patente/invención.

Solicitante: LOCKHEED MARTIN CORPORATION.

Nacionalidad solicitante: Estados Unidos de América.

Dirección: 9500 GODWIN DRIVE, BUILDING 400/043,MANASSAS, VA 20110-4157.

Inventor/es: MATHUR,CHANDAN, HELLENBACH,SCOTT, RAPP,JOHN,W, JACKSON,LARRY, JONES,MARK, CHERASARO,TROY.

Fecha de Publicación: .

Fecha Concesión Europea: 12 de Diciembre de 2007.

Clasificación PCT:

- G06F9/38 FISICA. › G06 CALCULO; CONTEO. › G06F PROCESAMIENTO ELECTRICO DE DATOS DIGITALES (sistemas de computadores basados en modelos de cálculo específicos G06N). › G06F 9/00 Disposiciones para el control por programa, p. ej. unidades de control (control por programa para dispositivos periféricos G06F 13/10). › Ejecución simultánea de instrucciones, p. ej. segmentación, anticipación.

Patentes similares o relacionadas:

Control de ejecución de hilos en un procesador multihilo, del 24 de Junio de 2020, de INTERNATIONAL BUSINESS MACHINES CORPORATION: Un método para controlar la ejecución de hilos en un entorno informático, comprendiendo dicho método: detener , mediante un hilo […]

Arquitectura e instrucciones flexibles para el estándar de cifrado avanzado (AES), del 27 de Mayo de 2020, de INTEL CORPORATION: Un procesador que comprende: una pluralidad de núcleos; una caché de instrucciones de nivel 1, L1, para almacenar una pluralidad de instrucciones […]

Predicados uniformes en sombreadores para unidades de procesamiento de gráficos, del 11 de Diciembre de 2019, de QUALCOMM INCORPORATED: Un procedimiento para procesar datos, comprendiendo el procedimiento: recibir una indicación de que todos los subprocesos de una urdimbre […]

Aumento de protocolo de coherencia para indicar estado de transacción, del 4 de Diciembre de 2019, de INTERNATIONAL BUSINESS MACHINES CORPORATION: Un método implementado por ordenador para implementar un protocolo de coherencia, comprendiendo el método: enviar , por un procesador (112a) solicitante, […]

Método y aparato para un acceso a memoria basado en hilos en un procesador multihilo, del 11 de Septiembre de 2019, de QUALCOMM INCORPORATED: Método para acceder a una memoria por un procesador multihilo , comprendiendo el método: determinar un identificador de hilo asociado a un […]

Procedimientos y aparatos para predecir la no ejecución de instrucciones de no bifurcación condicional, del 15 de Mayo de 2019, de QUALCOMM INCORPORATED: Un procedimiento para manejar una instrucción de no bifurcación condicional, que comprende: identificar una instrucción […]

Procesamiento transaccional, del 17 de Abril de 2019, de INTERNATIONAL BUSINESS MACHINES CORPORATION: Un método de controlar la ejecución de una transacción en un entorno informático, comprendiendo el método los pasos de: Iniciar, mediante un procesador, la ejecución […]

Guardar/restablecer registros seleccionados en procesamiento transaccional, del 13 de Marzo de 2019, de INTERNATIONAL BUSINESS MACHINES CORPORATION: Un método para facilitar el procesamiento de transacciones dentro de un entorno de computación, comprendiendo dicho método: obtener una instrucción […]