DISPOSICION PARA VERIFICACION JTAG.

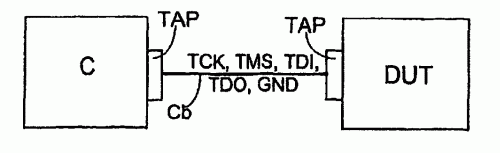

Un sistema de verificación JTAG que comprende un equipo de prueba JTAG (TS) y un dispositivo en fase de prueba (DUT) compatible con el JTAG dispuesto para formar una conexión para transmisión de datos síncrona entre ellos para transferir datos de prueba a través de un recorrido de transmisión (Cb) colocado entre interfaces predeterminadas (TAP),

caracterizado porque dicho recorrido de transmisión entre las interfaces (TAP) es una conexión asíncrona (ATP), y porque dicho equipo de prueba (TS) y dicho dispositivo en fase de prueba (DUT) comprenden un transceptor (TR1, TR2) dispuesto en el lado del recorrido de transmisión (ATP), estando configurado el transceptor (TR1, TR2) para disponer los datos de prueba que han de enviarse desde dicha interfaz (TAP) en un modo apropiado para un recorrido de transmisión asíncrona y en consecuencia para disponer los datos de prueba que llegan del recorrido de transmisión asíncrona para que sean recibidos en un modo síncrono requerido por dicha interfaz (TAP).

Tipo: Resumen de patente/invención.

Solicitante: PATRIA FINAVITEC OY.

Nacionalidad solicitante: Finlandia.

Dirección: NAULAKATU 3,33100 TAMPERE.

Inventor/es: SIMONEN, MIKKO, REIS, ILKKA.

Fecha de Publicación: .

Fecha Concesión Europea: 4 de Mayo de 2005.

Clasificación Internacional de Patentes:

- G01R31/3185 FISICA. › G01 METROLOGIA; ENSAYOS. › G01R MEDIDA DE VARIABLES ELECTRICAS; MEDIDA DE VARIABLES MAGNETICAS (indicación de la sintonización de circuitos resonantes H03J 3/12). › G01R 31/00 Dispositivos para ensayo de propiedades eléctricas; Dispositivos para la localización de fallos eléctricos; Disposiciones para el ensayo eléctrico caracterizadas por lo que se está ensayando, no previstos en otro lugar (ensayo o medida de dispositivos semiconductores o de estado sólido, durante la fabricación H01L 21/66; ensayo de los sistemas de transmisión por líneas H04B 3/46). › Reconfiguración para los ensayos, p. ej. LSSD, divisiones.

- G01R31/319 G01R 31/00 […] › Hardware de pruebas, es decir, circuitos de tratamiento de señales de salida.

Patentes similares o relacionadas:

Dispositivo de protección contra fallas en circuitos de árbol de reloj, del 10 de Febrero de 2016, de Winbond Electronics Corp: Un circuito integrado "CI", que comprende:

Un circuito de árbol de reloj configurado para distribuir una señal de reloj en el circuito […]

Dispositivo de protección contra fallas en circuitos de árbol de reloj, del 10 de Febrero de 2016, de Winbond Electronics Corp: Un circuito integrado "CI", que comprende:

Un circuito de árbol de reloj configurado para distribuir una señal de reloj en el circuito […]

Aparato y procedimiento de control de la modificación dinámica de una trayectoria de exploración, del 16 de Julio de 2014, de ALCATEL LUCENT: Un aparato de sistema en chip , que comprende:

una trayectoria de exploración de prueba que comprende una pluralidad de componentes […]

Aparato y procedimiento de control de la modificación dinámica de una trayectoria de exploración, del 16 de Julio de 2014, de ALCATEL LUCENT: Un aparato de sistema en chip , que comprende:

una trayectoria de exploración de prueba que comprende una pluralidad de componentes […]

DISPOSITIVO Y PROCEDIMIENTO PARA CREAR UNA FIRMA., del 16 de Noviembre de 2006, de SIEMENS AKTIENGESELLSCHAFT: Dispositivo para crear una firma, en donde se ha previsto una cantidad precalculada de registros de desplazamiento , en los que se depositan […]

SISTEMA Y PROCEDIMIENTO PARA PPREPROGRAMAR LA MEMORIA DE UN DISPOSITIVO ELECTRONICO., del 16 de Julio de 2006, de QUALCOMM INCORPORATED: Procedimiento para programar en paralelo la memoria de un dispositivo electrónico con un código de prueba y un código de sistema antes de […]

SISTEMA DIGITAL Y METODO DE DETECCION DE ERRORES DEL MISMO., del 1 de Junio de 2006, de KONINKLIJKE PHILIPS ELECTRONICS N.V.: Sistema digital para procesar un vector (VEn_p) digital de entrada, que comprende p bits (E1, E2, ..., Ep), para proporcionar un vector (VSa_q) digital […]

METODO PARA ALMACENAR PROPIEDADES DE REGISTRO EN UNA ESTRUCTURA DE DATOS Y ESTRUCTURA DE DATOS RELACIONADA., del 1 de Junio de 2006, de ALCATEL: Método para almacenar propiedades de registro de un dispositivo hardware (ASIC1, ASIC2, ASIC3, ASIC4) que tiene memoria heterogénea, en una estructura de datos, estando […]

PROCEDIMIENTO DE PRUEBA DE RADIOFRECUENCIA SIN HILOS DE CIRCUITOS INTEGRADOS Y OBLEAS., del 16 de Marzo de 2006, de THE GOVERNORS OF THE UNIVERSITY OF ALBERTA: Aparato para probar un circuito integrado sobre una oblea que comprende: a) un circuito de prueba formado sobre la oblea con el circuito […]

COMPOSICIONES DE TRAZAS DE DATOS PARA UN CIRCUITO INTEGRADO DE MEMORIAS MULTIPLES, del 1 de Marzo de 2009, de QUALCOMM INCORPORATED: Un circuito integrado que comprende: una pluralidad de memorias (126a, 126b); y un módulo de traza operativo para formar paquetes de trazas de datos, […]

COMPOSICIONES DE TRAZAS DE DATOS PARA UN CIRCUITO INTEGRADO DE MEMORIAS MULTIPLES, del 1 de Marzo de 2009, de QUALCOMM INCORPORATED: Un circuito integrado que comprende: una pluralidad de memorias (126a, 126b); y un módulo de traza operativo para formar paquetes de trazas de datos, […]