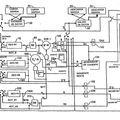

SUMADOR DE 1 BIT.

POR EJEMPLO PARA LAS APLICACIONES DE VIDEO SE REQUIEREN MULTIPLICADORES RAPIDOS CON UNA ALTA RESOLUCION.

PERO UNA RESOLUCION MAYOR DA COMO RESULTADO QUE SE TENGAN QUE CALCULAR PRODUCTOS MAS PARCIALES DE FORMA INTERNA. PUEDE USARSE EL ALGORITMO DE BOOTH-MC SORLEY PARA REDUCIR EL NUMERO REQUERIDO DE PRODUCTOS PARCIALES. ESTE ALGORITMO PUEDE COMBINARSE CON UNA PROPAGACION DIAGONAL DEL ACARREO DE UN PRODUCTO PARCIAL AL OTRO, PERMITIENDO QUE TODAS LAS SUMAS SE CALCULEN EN UNA LINEA SIMULTANEAMENTE. PERO EL TIEMPO DE MULTIPLICACION NO ES LO SUFICIENTEMENTE CORTO. EL MULTIPLICADOR DE LA INVENCION TIENE UN DISEÑO CERCANO AL CMOS Y HA SIDO CONSTRUIDO CON TECNOLOGIA BICMOS DE 1.2 (MU), QUE TIENE UN TIEMPO DE APLICACION DE 9 NS CON UNA TENSION DE SUMINISTRO DE 5 VOLTIOS. SE HA CONSEGUIDO UN TIEMPO DE MULTIPLICACION MINIMO MEDIANTE UNA COMBINACION DE LAS SIGUIENTES TECNICAS: EL USO DEL ALGORITMO BOOTH-MC SORLEY PARA REDUCIR EL NUMERO DE PRODUCTOS PARCIALES; LA PROPAGACION DIAGONAL DEL ACARREO DE UN PRODUCTO PARCIAL AL OTRO PERMITIENDO QUE TODAS LAS SUMAS SE HAGAN SIMULTANEAMENTE SOBRE UNA LINEA. EL USO DE APROXIMACION DE SELECCION DE ACARREO EN EL SUMADOR TOTAL DE 14 BITS Y EN LOS DOS SUMADORES DE LAS FILAS INTERMEDIAS; EL USO DE SUMADORES COMPLETOS DE UN BIT DE LA INVENCION CON LOGICA TRANSITORIA DE PASO COMPLEMENTARIO.

Tipo: Resumen de patente/invención.

Solicitante: THOMSON MULTIMEDIA.

Nacionalidad solicitante: Francia.

Dirección: 46, QUAI A. LE GALLO, 92648 BOULOGNE CEDEX.

Inventor/es: CHAN YAN FONG, JOSEPH.

Fecha de Publicación: .

Fecha Solicitud PCT: 12 de Octubre de 1992.

Fecha Concesión Europea: 3 de Septiembre de 1997.

Clasificación Internacional de Patentes:

- G06F7/50 FISICA. › G06 CALCULO; CONTEO. › G06F PROCESAMIENTO ELECTRICO DE DATOS DIGITALES (sistemas de computadores basados en modelos de cálculo específicos G06N). › G06F 7/00 Métodos o disposiciones para el procesamiento de datos actuando sobre el orden o el contenido de los datos tratados (circuitos lógicos H03K 19/00). › Adición; Subtracción (G06F 7/483 - G06F 7/491, G06F 7/544 - G06F 7/556 tiene prioridad).

- G06F7/52 G06F 7/00 […] › Multiplicación; División (G06F 7/483 - G06F 7/491, G06F 7/544 - G06F 7/556 tienen prioridad).

Países PCT: Alemania, España, Francia, Reino Unido, Italia, Oficina Europea de Patentes, Japón, República de Corea, Estados Unidos de América.

Patentes similares o relacionadas:

DISPOSITIVO PARA LA MULTIPLICACION CON FACTORES CONSTANTES Y SU UTILIZACION PARA LA COMPRESION DE VIDEO (MPEG)., del 16 de Abril de 2006, de INFINEON TECHNOLOGIES AG: Dispositivo para la multiplicación de un multiplicando binario (QMi) por factores (QS) constantes a partir de un número de factores diferentes […]

METODO PARA LA COMPUTACION DE LAS OPERACIONES DE DIVISION, RECIPROCO, RAIZ CUADRADA Y RAIZ CUADRADA INVERSA., del 16 de Noviembre de 2004, de UNIVERSIDADE DE SANTIAGO DE COMPOSTELA: Método para la computación de las operaciones de división, recíproco, raíz cuadrada y raíz cuadrada inversa. El método para la computación en doble precisión en formato de punto […]

MULTIPLICADOR RAPIDO PARA MULTIPLICAR UNA SEÑAL NUMERICA POR UNA SEÑAL PERIODICA., del 16 de Noviembre de 2001, de THOMSON-CSF SEXTANT: LA INVENCION SE REFIERE A UN CIRCUITO DE MULTIPLICACION DIGITAL PARA MULTIPLICAR UNA SEÑAL DIGITAL SN POR UNA FORMA DE ONDA PERIODICA, EN PRINCIPIO […]

METODO Y DISPOSITIVO PARA LLEVAR A CABO UNA DIVISION ARITMETICA APROXIMADA, del 1 de Marzo de 1996, de TELEFONAKTIEBOLAGET L M ERICSSON: METODO Y ORDEN PARA REALIZAR UNA DIVISION APROXIMADA DE UN NUMERO CONSTANTE MEDIANTE UN NUMERO VARIABLE EN FORMA BINARIA. SE SUPONE QUE EL NUMERO VARIABLE […]

CIRCUITO DE CONTROL DE GANANCIA DE SEÑAL DIGITAL., del 1 de Junio de 1994, de RCA THOMSON LICENSING CORPORATION: UN SISTEMA DE CONTROL DEL VOLUMEN O VARIACION DE LA AMPLITUD DE LAS SEÑALES DIGITALES INCLUYE UNA CONEXION EN CASCADA DE UN MULTIPLICADOR/DIVISOR BASTO […]

UN APARATO DIVISOR ELECTRONICO,CON CIRCUITERIA SIMPLIFICADA, del 1 de Septiembre de 1986, de FUJITSU LIMITED: DISPOSITIVO DIVISOR ELECTRONICO. CONSTA DE UN REGISTRO PARA ALMACENAR EL VALOR DIVISOR, OTRO REGISTRO PARA DIVIDENDO O RESTO PARCIAL, UN […]

UN PROCESADOR ASOCIATIVO CON CAPACIDAD DE MULTIPLICACION RAPIDA CON LONGITUD VARIABLE., del 16 de Junio de 1984, de STANDARD ELECTRICA, S.A.: PROCESADOR ASOCIATIVO CON CAPACIDAD DE MULTIPLICACION RAPIDA CON LONGITUD VARIABLE.COMPRENDE: A) UNA ORDENACION DE PILAS Y COLUMNAS DE CELULA ASOCIATIVAS ADAPTADAS CADA UNA […]

APARATO Y METODO MEJORADOS PARA LA MULTIPLICACION Y EXPONENCIACION MODULARES BASADAS EN LA MULTIPLICACION DE MONTGOMERY, del 16 de Marzo de 2008, de FORTRESS U & T LTD.: Unidad aritmético lógica (ALU) microelectrónica para realizar una multiplicación modular de tipo Montgomery de P(A·B)N, donde P(P·B)N es modularmente […]

APARATO Y METODO MEJORADOS PARA LA MULTIPLICACION Y EXPONENCIACION MODULARES BASADAS EN LA MULTIPLICACION DE MONTGOMERY, del 16 de Marzo de 2008, de FORTRESS U & T LTD.: Unidad aritmético lógica (ALU) microelectrónica para realizar una multiplicación modular de tipo Montgomery de P(A·B)N, donde P(P·B)N es modularmente […]