UN PROCESADOR ASOCIATIVO CON CAPACIDAD DE MULTIPLICACION RAPIDA CON LONGITUD VARIABLE.

PROCESADOR ASOCIATIVO CON CAPACIDAD DE MULTIPLICACION RAPIDA CON LONGITUD VARIABLE.

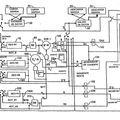

COMPRENDE: A) UNA ORDENACION DE PILAS Y COLUMNAS DE CELULA ASOCIATIVAS ADAPTADAS CADA UNA PARA ALMACENAR SIMULTANEAMENTE UN BIT DE SUMA Y UN BIT DE ARRASTRE; B) UN ELEMENTO DE MASCARA PARA IDENTIFICAR QUE UNA O MAS CELULAS CONTIENEN UN BIT DEL MULTIPLICADOR O DEL MULTIPLICANDO O DE AMBOS; C) UN ELEMENTO PARA ALMACENAR UN BIT DEL MULTIPLICADOR; D) UN ELEMENTO PARA MULTIPLICAR EL BIT DEL MULTIPLICANDO CON UN BIT DEL MULTIPLICADOR; E) UN ELEMENTO PARA ACTIVAR LA CELULA DURANTE UNA OPERACION DE MULTIPLICACION PARA QUE LA CELULA ALMACENE DOS BITS DEL RESULTADO DE LA MULTIPLICACION; F) UN ELEMENTO DE UNIDAD DE LOGICA ARITMETICA PARA RECIBIR EN SERIE LOS BITS DEL MULTIPLICADOR PARA SUMAR O RESTAR EL BIT DEL MULTIPLICANDO CON MASCARA A LOS RESULTADOS DE LA OPERACION ARITMETICA DEL TIEMPO DE DESPLAZAMIENTO PARA CONSEGUIR UN RESULTADO DE LA MULTIPLICACION EN CURSO; G) UN ELEMENTO PARA ACOPLAR LOS RESULTADOS DE LA MULTIPLICACION A LA CELULA ASOCIATIVA ADYACENTE EN EL MISMO TIEMPO DE DESPLAZAMIENTO EN QUE SE OBTIENE EL RESULTADO EN CURSO.

Tipo: Resumen de patente/invención.

Solicitante: STANDARD ELECTRICA, S.A..

Nacionalidad solicitante: España.

Provincia: MADRID.

Fecha de Solicitud: 1 de Agosto de 1983.

Fecha de Publicación: .

Fecha de Concesión: 21 de Marzo de 1984.

Clasificación Internacional de Patentes:

- G06F7/52 FISICA. › G06 CALCULO; CONTEO. › G06F PROCESAMIENTO ELECTRICO DE DATOS DIGITALES (sistemas de computadores basados en modelos de cálculo específicos G06N). › G06F 7/00 Métodos o disposiciones para el procesamiento de datos actuando sobre el orden o el contenido de los datos tratados (circuitos lógicos H03K 19/00). › Multiplicación; División (G06F 7/483 - G06F 7/491, G06F 7/544 - G06F 7/556 tienen prioridad).

Patentes similares o relacionadas:

DISPOSITIVO PARA LA MULTIPLICACION CON FACTORES CONSTANTES Y SU UTILIZACION PARA LA COMPRESION DE VIDEO (MPEG)., del 16 de Abril de 2006, de INFINEON TECHNOLOGIES AG: Dispositivo para la multiplicación de un multiplicando binario (QMi) por factores (QS) constantes a partir de un número de factores diferentes […]

METODO PARA LA COMPUTACION DE LAS OPERACIONES DE DIVISION, RECIPROCO, RAIZ CUADRADA Y RAIZ CUADRADA INVERSA., del 16 de Noviembre de 2004, de UNIVERSIDADE DE SANTIAGO DE COMPOSTELA: Método para la computación de las operaciones de división, recíproco, raíz cuadrada y raíz cuadrada inversa. El método para la computación en doble precisión en formato de punto […]

MULTIPLICADOR RAPIDO PARA MULTIPLICAR UNA SEÑAL NUMERICA POR UNA SEÑAL PERIODICA., del 16 de Noviembre de 2001, de THOMSON-CSF SEXTANT: LA INVENCION SE REFIERE A UN CIRCUITO DE MULTIPLICACION DIGITAL PARA MULTIPLICAR UNA SEÑAL DIGITAL SN POR UNA FORMA DE ONDA PERIODICA, EN PRINCIPIO […]

SUMADOR DE 1 BIT., del 1 de Febrero de 1998, de THOMSON MULTIMEDIA: POR EJEMPLO PARA LAS APLICACIONES DE VIDEO SE REQUIEREN MULTIPLICADORES RAPIDOS CON UNA ALTA RESOLUCION. PERO UNA RESOLUCION MAYOR DA COMO RESULTADO QUE SE TENGAN QUE CALCULAR […]

METODO Y DISPOSITIVO PARA LLEVAR A CABO UNA DIVISION ARITMETICA APROXIMADA, del 1 de Marzo de 1996, de TELEFONAKTIEBOLAGET L M ERICSSON: METODO Y ORDEN PARA REALIZAR UNA DIVISION APROXIMADA DE UN NUMERO CONSTANTE MEDIANTE UN NUMERO VARIABLE EN FORMA BINARIA. SE SUPONE QUE EL NUMERO VARIABLE […]

CIRCUITO DE CONTROL DE GANANCIA DE SEÑAL DIGITAL., del 1 de Junio de 1994, de RCA THOMSON LICENSING CORPORATION: UN SISTEMA DE CONTROL DEL VOLUMEN O VARIACION DE LA AMPLITUD DE LAS SEÑALES DIGITALES INCLUYE UNA CONEXION EN CASCADA DE UN MULTIPLICADOR/DIVISOR BASTO […]

UN APARATO DIVISOR ELECTRONICO,CON CIRCUITERIA SIMPLIFICADA, del 1 de Septiembre de 1986, de FUJITSU LIMITED: DISPOSITIVO DIVISOR ELECTRONICO. CONSTA DE UN REGISTRO PARA ALMACENAR EL VALOR DIVISOR, OTRO REGISTRO PARA DIVIDENDO O RESTO PARCIAL, UN […]

APARATO Y METODO MEJORADOS PARA LA MULTIPLICACION Y EXPONENCIACION MODULARES BASADAS EN LA MULTIPLICACION DE MONTGOMERY, del 16 de Marzo de 2008, de FORTRESS U & T LTD.: Unidad aritmético lógica (ALU) microelectrónica para realizar una multiplicación modular de tipo Montgomery de P(A·B)N, donde P(P·B)N es modularmente […]

APARATO Y METODO MEJORADOS PARA LA MULTIPLICACION Y EXPONENCIACION MODULARES BASADAS EN LA MULTIPLICACION DE MONTGOMERY, del 16 de Marzo de 2008, de FORTRESS U & T LTD.: Unidad aritmético lógica (ALU) microelectrónica para realizar una multiplicación modular de tipo Montgomery de P(A·B)N, donde P(P·B)N es modularmente […]