Detección y correccion de errores para una memoria cuyos estados de bit tienen una resistencia de error diferente.

Una memoria que comprende:

- celdas de memoria (7, 8, 12, 13),

únicas o múltiples, de comportamiento disimétrico,

- un comportamiento disimétrico resultante de la sensibilidad de una celda de memoria en un primer estadoeléctrico, al cambiar de estado a un segundo estado eléctrico cuando se produce una agresión por irradiación,de tal manera que esta sensibilidad es menos grande para pasar del primer estado al segundo estado quepara pasar del segundo estado al primer estado,

- pares de celdas de memoria, formados por estas celdas de memoria de comportamiento disimétrico,

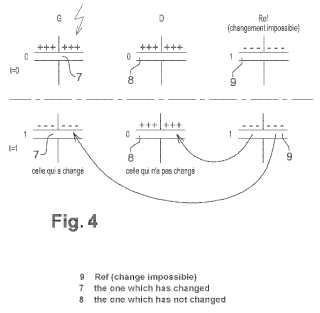

- de tal manera que una primera celda (7) de un par está cargada con una primera información binaria y unasegunda celda (9) del par está cargada con una segunda información binaria,

- un detector (17), destinado a detectar que las celdas de memoria de un par están cargadas con dosinformaciones contradictorias en lugar de dos informaciones coherentes, y

caracterizada por que comprende:

- una celda de memoria de referencia (9, 14), cargada con una información correspondiente al primer estadoeléctrico insensible a las agresiones, de tal modo que este estado eléctrico corresponde a un estado lógico enel que la información binaria es falsa,

- un circuito lógico destinado a designar aquella de las celdas de memoria del par que se encuentra en elsegundo estado eléctrico correspondiente a un estado lógico en que la información binaria es verdadera,cuando los estados eléctricos de las dos celdas son contradictorios, en función del estado eléctrico de lacelda de memoria de referencia.

Tipo: Patente Internacional (Tratado de Cooperación de Patentes). Resumen de patente/invención. Número de Solicitud: PCT/FR2009/051165.

Solicitante: ASTRIUM SAS.

Nacionalidad solicitante: Francia.

Dirección: 6 RUE LAURENT PICHAT 75016 PARIS FRANCIA.

Inventor/es: MILLER,Florent, CARRIERE,Thierry, BOUGEROL,Antonin.

Fecha de Publicación: .

Clasificación Internacional de Patentes:

- G11C5/00 FISICA. › G11 REGISTRO DE LA INFORMACION. › G11C MEMORIAS ESTATICAS (dispositivos semiconductores para memorias H01L, p. ej. H01L 27/108 - H01L 27/11597). › Detalles de memorias cubiertos por el grupo G11C 11/00.

PDF original: ES-2386305_T3.pdf

Fragmento de la descripción:

Detección y corrección de errores para una memoria cuyos estados de bit tienen una resistencia de error diferente.

La presente invención tiene por objeto un procedimiento de detección y de corrección de errores para memorias electrónicas, cuyo punto de memoria tiene un comportamiento de memorización disimétrico. El procedimiento permite utilizar memorias electrónicas comerciales y no específicamente protegidas, a pesar de su sensibilidad a las interacciones energéticas externas, en aplicaciones aeronáuticas o espaciales. Esta es aplicable a todas las familias de memorias con material de base semiconductor, que tengan un comportamiento disimétrico, embarcadas o instaladas en sistemas inducidos a evolucionar en entornos perturbados por radiaciones naturales o artificiales.

En el caso del entorno radiactivo natural, un efecto del que protege la invención recibe el nombre de efecto singular. Se trata de un efecto no destructivo que se traduce en la inversión de una o varias informaciones lógicas almacenadas en una memoria electrónica. Efectos de este tipo son provocados por el aporte de cargas eléctricas seguidamente al paso de una partícula ionizante, de forma directa o no.

En el momento actual, existe un cierto número de técnicas de detección y de correcciones de errores que se ponen en práctica para afrontar esta problemática. No obstante, su eficacia es proporcional a su complejidad y a su coste. Es por ello que su utilización se ve a menudo restringida a los elementos más críticos de un sistema. La información unitaria, que recibe el nombre de bit, es binaria y puede tomar el valor ‘1’ o ‘0’. Se denomina palabra a un conjunto de varios bits. Los criterios que determinan la eficacia de una técnica de detección y de corrección de errores son el número de bits con error que pueden ser detectados en una palabra, el número de bits con error que pueden ser corregidos, el tiempo de tratamiento así como la cantidad de recursos necesaria para efectuar estas detecciones y correcciones. El rendimiento R es la relación entre el número de bits que se han de corregir y el número de bits que se han de almacenar.

Por orden de complejidad, se distinguen diferentes técnicas de detección y de corrección. La técnica de los códigos de paridad permite la detección de un único error en una palabra. Para una información codificada en n bits, se almacena un bit suplementario. Esta técnica no permite la corrección del error. La técnica de los códigos de Hamming permite la detección de dos errores y la corrección de un error dentro de una palabra. El Código de Hamming (11, 7) , por ejemplo, permite, de esta forma, proteger una información de 7 bits añadiendo 4 bits suplementarios. Este código es el que tiene un rendimiento, es decir, el número de bits transmitidos con respecto al número de bits útiles, máximo en el marco de la corrección de un bit único en una palabra.

La técnica de los códigos de Reed Salomon corrige varios errores en el seno de una misma palabra. Para una información de N bits y para corregir K bits, es necesario almacenar N + 2K bits. Así, para corregir la integridad de los N bits de una palabra, es necesario almacenar 3 x N bits. El rendimiento es, por tanto, R = 1/3.

La técnica de triplicación utiliza una redundancia triple, es decir, que cada dato se almacena en tres ejemplares. Un elemento de tipo votante compara los tres datos y selecciona el valor que aparece al menos dos veces. Como en la técnica precedente, a fin de proteger los N bits de una palabra, es necesario almacenar 3 x N bits. El rendimiento es, por tanto, también R = 1/3.

Actualmente, los sistemas que protegen la integridad de los bits de una palabra necesitan, por consiguiente, almacenar, como mínimo, tres veces más informaciones, lo que es un rendimiento R = 1/3. La invención propuesta es una técnica que permite detectar y corregir la integridad de los bits de una palabra, sea cual sea su longitud, y que necesita un menor almacenamiento de bits suplementarios que las técnicas existentes, siendo el rendimiento próximo a R = ½.

La invención se basa en una prioridad intrínseca de ciertas familias de memorias electrónicas, para las cuales se constata un comportamiento disimétrico, o asimétrico, de la estructura de memorización, y para las cuales uno de los dos estados posibles es insensible a las perturbaciones externas.

Se dice que una memoria tiene comportamiento simétrico cuando la información es almacenada en una estructura simétrica, como es el caso, por ejemplo, en un punto de memoria SRAM, que pone en funcionamiento dos inversores retroacoplados. La Figura 1 muestra, a este respecto, un punto de memoria SRAM, de estructura simétrica.

Por el contrario, se entiende por memoria de comportamiento disimétrico las memorias para las que la información lógica es almacenada en una estructura no simétrica, como, por ejemplo, una capacidad que almacena una cierta cantidad de cargas eléctricas, o un transistor que almacena una cierta cantidad de cargas eléctricas en su casilla flotante.

La invención se aplica indiferentemente a las memorias del tipo volátil y no volátil. Se entiende por memorias volátiles las memorias que pierden la información almacenada cuando se quedan sin tensión. Y a la inversa, se

denomina memoria no volátil a una memoria que guarda la información cuando se queda sin tensión.

Entre las memorias de comportamiento disimétrico y volátil, puede citarse, a título de ejemplo, la familia de las memorias DRAM, memorias dinámicas de acceso aleatorio [“dynamic random-access memories”] (VDRAM [DRAM de vídeo –“video DRAM”], RDRAM [DRAM de bus de RAM –“Rambus DRAM”], XDR DRAM [DRAM de intervalo dinámico extendido –“eXtended Dynamic Range DRAM”], DRAM EDO [salida de datos extendida de DRAM –“DRAM extended data output”], DDR, DDR2, DDR3, eDRAM, DRAM FPM, ...) , para las cuales se almacena la información lógica en una estructura capacitiva. La información almacenada puede ser un ‘1’ o un ‘0’ lógico, según que la capacidad esté cargada o no.

La Figura 2 muestra en corte un ejemplo de una estructura, así como la representación esquemática asociada, para un punto de memoria DRAM. Este punto de memoria 1 comprende un condensador C1, conectado por medio de un transistor M1 a una fila 2 de bits. El transistor M1 está gobernado por una fila 3 de palabras, conectada a su casilla. El potencial de la armadura del condensador conectado al transistor M1 se lleva a VCC cuando el punto de memoria memoriza un 1. Este se lleva al de la masa cuando se memoriza un 0. Las memorias de comportamiento disimétrico y no volátiles son las de la familia de las EPROMs [memorias de solo lectura programables y borrables –“erasable programmable read-only memories”] y de las FLASHs [memorias de acceso por impulsos], con un transistor de casilla flotante como elemento de memorización.

La invención se aplica para las memorias anteriormente citadas, ya sean de una sola celda o de múltiples celdas. Recibe el nombre de memoria de una sola celda una memoria que almacena una información binaria por cada estructura física. Se denomina memoria de múltiples celdas a una memoria que almacena varias informaciones binarias en una misma estructura física.

Se denomina estado, en el sentido de estado eléctrico, a un estado físico de una celda, por ejemplo, una celda con electrones almacenados o no sobre una armadura implicada de un condensador de una memoria DRAM, o con electrones almacenados o no en la casilla flotante de una EPROM o de una memoria FLASH.

Se denomina información binaria, fundamentalmente dependiente de un protocolo de lectura, de un modo de lectura, a un estado lógico, en oposición a un estado eléctrico, cuyo valor es 1 o 0. Según se esté en lógica positiva o en lógica negativa, un mismo estado eléctrico, electrones almacenados en una placa de condensador o en una casilla flotante, que puede corresponder a dos estados lógicos diferentes.

La propiedad física utilizada es la insensibilidad frente a la recogida de cargas parásitas de unos de los dos estados posibles de una celda de memoria de comportamiento disimétrico. Dicho de otro modo, es la particularidad para este tipo de celda de no tener más que un solo estado sometido a las perturbaciones externas.... [Seguir leyendo]

Reivindicaciones:

1. Una memoria que comprende:

- celdas de memoria (7, 8, 12, 13) , únicas o múltiples, de comportamiento disimétrico,

- un comportamiento disimétrico resultante de la sensibilidad de una celda de memoria en un primer estado eléctrico, al cambiar de estado a un segundo estado eléctrico cuando se produce una agresión por irradiación, de tal manera que esta sensibilidad es menos grande para pasar del primer estado al segundo estado que para pasar del segundo estado al primer estado,

- pares de celdas de memoria, formados por estas celdas de memoria de comportamiento disimétrico,

- de tal manera que una primera celda (7) de un par está cargada con una primera información binaria y una segunda celda (9) del par está cargada con una segunda información binaria,

- un detector (17) , destinado a detectar que las celdas de memoria de un par están cargadas con dos informaciones contradictorias en lugar de dos informaciones coherentes, y caracterizada por que comprende:

- una celda de memoria de referencia (9, 14) , cargada con una información correspondiente al primer estado eléctrico insensible a las agresiones, de tal modo que este estado eléctrico corresponde a un estado lógico en el que la información binaria es falsa,

- un circuito lógico destinado a designar aquella de las celdas de memoria del par que se encuentra en el segundo estado eléctrico correspondiente a un estado lógico en que la información binaria es verdadera, cuando los estados eléctricos de las dos celdas son contradictorios, en función del estado eléctrico de la celda de memoria de referencia.

2. Una memoria de acuerdo con la reivindicación 1, caracterizada por que

- la segunda información corresponde un mismo estado eléctrico que el de la primera información para que estas informaciones sean coherentes,

- de manera que informaciones contradictorias son, entonces, informaciones correspondientes a estados eléctricos complementarios.

3. Una memoria de acuerdo con la reivindicación 1, caracterizada por que

- la segunda información corresponde a un estado eléctrico complementario al de la primera información para que estas informaciones sean coherentes,

- de tal modo que informaciones contradictorias son, entonces, informaciones correspondientes a unos mismos estados eléctricos.

4. Una memoria de acuerdo con una de las reivindicaciones 1 a 3, caracterizada por que

- el detector detecta aquella de las celdas que ha cambiado de estado como consecuencia de la irradiación, y

- un circuito lógico designa la otra celda como la celda que se encuentra en un estado verdadero.

5. Una memoria de acuerdo con una de las reivindicaciones 1 a 4, caracterizada por que es del tipo de DRAM o de EPROM.

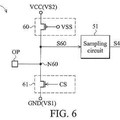

6. Una memoria de acuerdo con una de las reivindicaciones 1 a 4, caracterizada por que comprende:

- filas de bits conectadas a celdas de memoria duplicadas,

- un acceso o puerta O exclusiva, conectada a estas filas de bits,

- un duplexador gobernado por esta puerta O exclusiva,

- de manera que este duplexador recibe como entrada una de estas filas de bits y una fila de bits proveniente de la celda de referencia.

7. Uso de una memoria de acuerdo con una de las reivindicaciones 1 a 6 en una computadora de tipo personal.

8. Un procedimiento de detección y de corrección de errores de datos memorizados en una memoria cuyo punto de memoria es de comportamiento disimétrico, según el cual:

- se memorizan los datos que corregir en dos bancos de datos,

- se detecta un error en un banco y

- se corrige con el contenido del otro banco,

caracterizado por que

- resulta un comportamiento disimétrico de la sensibilidad de una celda de memoria en un primer estado eléctrico, al cambiar de estado a un segundo estado eléctrico cuando se produce una agresión por irradiación, siendo esta sensibilidad menos grande para pasar del primer estado al segundo estado que para pasar del segundo estado al primer estado,

- se forman pares de celdas de memoria con la ayuda de celdas memorizadas de comportamiento disimétrico en dos de los bancos,

-de tal modo que una primera celda de un par se carga con una primera información binaria y una segunda celda del par se carga con una segunda información binaria,

- se memoriza en una celda de memoria de referencia una información correspondiente al primer estado eléctrico insensible a las agresiones, de tal modo que este estado eléctrico corresponde a un estado lógico en el que la información binaria es falsa,

-se detecta que las celdas de memoria de un par están cargadas con dos informaciones contradictorias en lugar de dos informaciones coherentes, y

- se designa, con la ayuda de un circuito lógico, en función de la celda de memoria de referencia, aquella de las celdas de memoria del par que se encuentra en el segundo estado eléctrico correspondiente a un estado lógico en que la información binaria es verdadera, cuando los estados eléctricos de las dos celdas son

contradictorios.

9. Un procedimiento de acuerdo con la reivindicación 8, caracterizado por que, tras haber detectado un error, este se corrige.

Patentes similares o relacionadas:

Dispositivo de memoria que corrige el efecto de colisiones de partículas de alta energía, del 28 de Agosto de 2019, de THALES: Dispositivo de memoria que corrige automáticamente el efecto de colisiones de partículas de alta energía, que comprende una célula (CM) de memoria; […]

Sistema de memoria caché y método para generar objetos que no están almacenados en la memoria caché a partir de componentes de objetos en la memoria caché y almacenados, del 26 de Octubre de 2016, de AWARE, INC.: En un sistema de procesamiento de datos que tiene una memoria caché , un método para generar una imagen no almacenada en la memoria caché que comprende: […]

Difusión general selectiva de datos en dispositivos conectados en serie, del 9 de Abril de 2014, de MOSAID TECHNOLOGIES INCORPORATED: Método para seleccionar un subconjunto de dispositivos de una pluralidad de dispositivos conectados en serie a un controlador de memorias con el fin […]

Lectura de registro para memoria volátil, del 3 de Octubre de 2012, de QUALCOMM INCORPORATED: Un procedimiento de lectura de datos de un módulo SDRAM (RAM, Memoria de Acceso Dinámico Síncrona), no estando almacenados tales datos en una matriz DRAM […]

Sistema y procedimiento para el control de potencia en sistemas de comunicación inalámbrica, del 24 de Abril de 2012, de QUALCOMM INCORPORATED: Un metodo para variar un nivel de potencia de una seral proporcionada a un amplificador de potencia de un transmisor de un dispositivo de comunicacion inalambrica, […]

Chips de memoria y circuitos de evaluación de los mismos, del 14 de Marzo de 2012, de Winbond Electronics Corp: Un chip de memoria que opera en una pluralidad de modos, que comprende: Una plaqueta de opción (OP) que tiene una pluralidad de estados; y una unidad de […]

Chips de memoria y circuitos de evaluación de los mismos, del 14 de Marzo de 2012, de Winbond Electronics Corp: Un chip de memoria que opera en una pluralidad de modos, que comprende: Una plaqueta de opción (OP) que tiene una pluralidad de estados; y una unidad de […]

MATRIZ PASIVA NO VOLATIL Y METODO PARA LA LECTURA DE LA MISMA., del 16 de Agosto de 2005, de THIN FILM ELECTRONICS ASA: Dispositivo que constituye una memoria de matriz pasiva no volátil y comprende un material de memoria dieléctrico eléctricamente polarizable […]

ESCRITURA EN TIEMPO REAL ASEGURADA PARA MEMORIA NO VOLATIL, del 16 de Marzo de 2009, de GEMPLUS: Procedimiento para escribir datos iniciales contenidos en una petición de escritura (RE1) transmitida por un medio de tratamiento de datos (PR, AP) a […]

ESCRITURA EN TIEMPO REAL ASEGURADA PARA MEMORIA NO VOLATIL, del 16 de Marzo de 2009, de GEMPLUS: Procedimiento para escribir datos iniciales contenidos en una petición de escritura (RE1) transmitida por un medio de tratamiento de datos (PR, AP) a […]