Dispositivo de memoria que corrige el efecto de colisiones de partículas de alta energía.

Dispositivo de memoria que corrige automáticamente el efecto de colisiones de partículas de alta energía,

que comprende una célula (CM) de memoria;

- unos medios (MRET) de retención, durante un retardo determinado, de un umbral ejemplar de un valor (Qd) memorizado en dicha célula (CM) de memoria, caracterizado porque el dispositivo de memoria comprende además:

- unos medios (MDET) de detección de un cambio de estado de dicha célula (CM) de memoria, por comparación del valor (Qd) memorizado en dicha célula (CM) de memoria con el valor en retención en dichos medios (MRET) de retención; y

- unos medios (MG) de gestión que comprenden unos medios de multiplexado adaptados para determinar si un cambio de estado de dicha célula (CM) de memoria detectado es debido a una colisión de partículas de alta energía o es un cambio de estado controlado, los medios de multiplexado reciben en la entrada una salida del módulo (MDET) de detección, una señal (Q) que representa el valor situado en retención en el módulo (MRET) de retención durante el retardo determinado, un estado (Data) del dato a memorizar en la célula (MC) de memoria, así como una señal (CS) de validación de la carga de datos que acompañan a dicho estado (Data) confirmando un cambio de estado controlado del valor a memorizar en dicha célula de memoria y adaptados para, en el caso de que el cambio de estado de dicha célula de memoria detectado sea debido a una colisión de partículas de alta energía, controlar automáticamente una recarga del valor memorizado en dichos medios (MRET) de retención en dicha célula (CM) de memoria, permitiendo de ese modo evitar la intervención de un reloj de cadencia de refresco de los datos que pueda perturbar funciones de tipo de radiofrecuencia RF.

Tipo: Patente Europea. Resumen de patente/invención. Número de Solicitud: E12173220.

Solicitante: THALES.

Inventor/es: JACQUET, BRUNO, RODRIGUEZ,RAOUL, LAVALETTE,VINCENT.

Fecha de Publicación: .

Clasificación Internacional de Patentes:

- G11C11/412 FISICA. › G11 REGISTRO DE LA INFORMACION. › G11C MEMORIAS ESTATICAS (dispositivos semiconductores para memorias H01L, p. ej. H01L 27/108 - H01L 27/11597). › G11C 11/00 Memorias digitales caracterizadas por la utilización de elementos de almacenamiento eléctricos o magnéticos particulares; Elementos de almacenamiento correspondientes (G11C 14/00 - G11C 21/00 tienen prioridad). › utilizando únicamente transistores de efecto de campo.

- G11C5/00 G11C […] › Detalles de memorias cubiertos por el grupo G11C 11/00.

- H03K19/003 ELECTRICIDAD. › H03 CIRCUITOS ELECTRONICOS BASICOS. › H03K TECNICA DE IMPULSO (medida de las características de los impulsos G01R; modulación de oscilaciones sinusoidales por impulsos H03C; transmisión de información digital, H04L; circuitos discriminadores de detección de diferencia de fase entre dos señales de conteo o integración de ciclos de oscilación H03D 3/04; control automático, arranque, sincronización o estabilización de generadores de oscilaciones o de impulsos electrónicos donde el tipo de generador es irrelevante o esta sin especificar H03L; codificación, decodificación o conversión de código, en general H03M). › H03K 19/00 Circuitos lógicos, es decir, teniendo al menos dos entradas que actúan sobre una salida (circuitos para sistemas de computadores que utilizan la lógica difusa G06N 7/02 ); Circuitos de inversión. › Modificaciones para aumentar la fiabilidad.

- H03K3/037 H03K […] › H03K 3/00 Circuitos para la generación de impulsos eléctricos; Circuitos monoestables, biestables o multiestables (H03K 4/00 tiene prioridad; para generadores de funciones digitales en ordenadores G06F 1/02). › Circuitos biestables.

PDF original: ES-2752745_T3.pdf

Patentes similares o relacionadas:

Sistema de memoria caché y método para generar objetos que no están almacenados en la memoria caché a partir de componentes de objetos en la memoria caché y almacenados, del 26 de Octubre de 2016, de AWARE, INC.: En un sistema de procesamiento de datos que tiene una memoria caché , un método para generar una imagen no almacenada en la memoria caché que comprende: […]

Difusión general selectiva de datos en dispositivos conectados en serie, del 9 de Abril de 2014, de MOSAID TECHNOLOGIES INCORPORATED: Método para seleccionar un subconjunto de dispositivos de una pluralidad de dispositivos conectados en serie a un controlador de memorias con el fin […]

Lectura de registro para memoria volátil, del 3 de Octubre de 2012, de QUALCOMM INCORPORATED: Un procedimiento de lectura de datos de un módulo SDRAM (RAM, Memoria de Acceso Dinámico Síncrona), no estando almacenados tales datos en una matriz DRAM […]

Sistema y procedimiento para el control de potencia en sistemas de comunicación inalámbrica, del 24 de Abril de 2012, de QUALCOMM INCORPORATED: Un metodo para variar un nivel de potencia de una seral proporcionada a un amplificador de potencia de un transmisor de un dispositivo de comunicacion inalambrica, […]

Detección y correccion de errores para una memoria cuyos estados de bit tienen una resistencia de error diferente, del 28 de Marzo de 2012, de ASTRIUM SAS: Una memoria que comprende:

- celdas de memoria , únicas o múltiples, de comportamiento disimétrico,

- un comportamiento disimétrico resultante de la sensibilidad […]

Detección y correccion de errores para una memoria cuyos estados de bit tienen una resistencia de error diferente, del 28 de Marzo de 2012, de ASTRIUM SAS: Una memoria que comprende:

- celdas de memoria , únicas o múltiples, de comportamiento disimétrico,

- un comportamiento disimétrico resultante de la sensibilidad […]

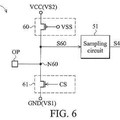

Chips de memoria y circuitos de evaluación de los mismos, del 14 de Marzo de 2012, de Winbond Electronics Corp: Un chip de memoria que opera en una pluralidad de modos, que comprende: Una plaqueta de opción (OP) que tiene una pluralidad de estados; y una unidad de […]

Chips de memoria y circuitos de evaluación de los mismos, del 14 de Marzo de 2012, de Winbond Electronics Corp: Un chip de memoria que opera en una pluralidad de modos, que comprende: Una plaqueta de opción (OP) que tiene una pluralidad de estados; y una unidad de […]

MATRIZ PASIVA NO VOLATIL Y METODO PARA LA LECTURA DE LA MISMA., del 16 de Agosto de 2005, de THIN FILM ELECTRONICS ASA: Dispositivo que constituye una memoria de matriz pasiva no volátil y comprende un material de memoria dieléctrico eléctricamente polarizable […]

ESCRITURA EN TIEMPO REAL ASEGURADA PARA MEMORIA NO VOLATIL, del 16 de Marzo de 2009, de GEMPLUS: Procedimiento para escribir datos iniciales contenidos en una petición de escritura (RE1) transmitida por un medio de tratamiento de datos (PR, AP) a […]

ESCRITURA EN TIEMPO REAL ASEGURADA PARA MEMORIA NO VOLATIL, del 16 de Marzo de 2009, de GEMPLUS: Procedimiento para escribir datos iniciales contenidos en una petición de escritura (RE1) transmitida por un medio de tratamiento de datos (PR, AP) a […]