PROCESADOR DE SEÑALES.

UN PROCESADOR DE SEÑALES QUE COMPRENDE UN PROCESADOR PARALELO CONECTADO DIVIDIDO QUE TRATA LAS SEÑALES DE DATOS PROCEDENTES DE FUENTES DE SEÑALES EXTERNAS Y PROPORCIONA FUNCIONES DE TRATAMIENTO DE SEÑALES UTILIZANDO UNA PLURALIDAD DE FORMATOS DE DATOS.

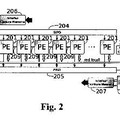

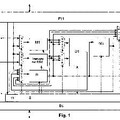

EL PROCESADOR DE SEÑALES COMPRENDE UN INTERFAZ EXTERNO QUE TIENE UN PUERTO DE CONTROL EN SERIE Y UNA PLURALIDAD DE PUERTOS PARALELOS BIDIRECCIONALES.EL INTERFAZ TRANSMITE LAS SEÑALES DE CONTROL Y DATOS ENTRE EL PROCESADOR DE SEÑALES Y LOS DISPOSITIVOS EXTERNOS.LOS PUERTOS PARALELOS SON CONFIGURABLES COMO PUERTOS PARALELOS INDIVIDUALES O COMO PARES ACOPLADOS QUE FORMAN UN PUERTO QUE TIENE LA TRAYECTORIA DE DATOS COMBINADA DE AMBOS PUERTOS ACOPLADOS.UN CONTROLADOR DE ELEMENTOS ARITMETICOS QUE COMPRENDE UNA MEMORIA DE MICROPROGRAMA Y UNA MEMORIA DE PROGRAMA DE CONTROL ESTA ACOPLADA AL INTERFAZ QUE CARGA LOS PROGRAMAS DE APLICACIONES EN LA MEMORIA DE PROGRAMAS DE CONTROL Y EJECUTA LOS PROGRAMAS.EL CONTROLADOR DE ELEMENTOS ARITMETICOS CONTROLA EL TRATAMIENTO DE LAS SEÑALES DE DATOS Y CONTROL EN EL PROCESADOR DE SEÑALES.UNA PLURALIDAD DE ELEMENTOS ARITMETICOS CONECTADOS ESTAN ACOPLADOS AL CONTROLADOR DE ELEMENTOS ARITMETICOS, COMPRENDIENDO CADA UNO UNA MEMORIA DE ALMACENAMIENTO DE DATOS, UN MULTIPLICADOR Y UNA UNIDAD DE LOGICA ARITMETICA Y REGISTRO. CADA ELEMENTO ARITMETICO TIENE SU MEMORIA DE ALMACENAMIENTO DE DATOS ACOPLADA AL INTERFAZ EXTERNO PARA RECIBIR Y ALMACENAR SEÑALES DE DATOS, Y A SU MULTIPLICADOR Y A LA UNIDAD DE LOGICA ARITMETICA Y REGISTRO PARA EJECUTAR OPERACIONES ARITMETICAS DE PUNTO FIJO Y FLOTANTE CON LOS DATOS ALMACENADOS EN LA MEMORIA DE ALMACENAMIENTO DE DATOS.ESTAS OPERACIONES ARITMETICAS SE EJECUTAN DE ACUERDO AL PROGRAMA DE APLICACION Y A LAS INSTRUCCIONES DE MICROPROGRAMA CONTENIDAS EN LAS MEMORIAS DE LOS MICROPROGRAMAS Y PROGRAMAS DE CONTROL.EL PRESENTE INVENTO PROPORCIONA UNA ARQUITECTURA DE ALTA EJECUCION PARA SU USO CON ALGORITMOS DE TRATAMIENTO DE SEÑALES DE MATRICES Y VECTORES QUE REDUCE AL MINIMO LA CANTIDAD DE HARDWARE NECESARIA PARA IMPLEMENTARLA.

Tipo: Resumen de patente/invención.

Solicitante: HUGHES AIRCRAFT COMPANY.

Nacionalidad solicitante: Estados Unidos de América.

Dirección: 7200 HUGHES TERRACE P.O. BOX 45066,LOS ANGELES, CALIFORNIA 90045-.

Inventor/es: DAVIES, STEVEN P., BALMFORTH, KEVIN D., BATES, GARY A., HABEREDER, HANS L., HARRISON, LOYD R., HOPP, DONALD M., RICKER, GEORGE G.

Fecha de Publicación: .

Fecha Concesión Europea: 12 de Marzo de 1997.

Clasificación Internacional de Patentes:

- G06F15/80 FISICA. › G06 CALCULO; CONTEO. › G06F PROCESAMIENTO ELECTRICO DE DATOS DIGITALES (sistemas de computadores basados en modelos de cálculo específicos G06N). › G06F 15/00 Computadores digitales en general (detalles G06F 1/00 - G06F 13/00 ); Equipo de procesamiento de datos en general. › que comprenden un conjunto de unidades de procesamiento con control común, p. ej. varios procesadores de datos de instrucción única (G06F 15/82 tiene prioridad).

Patentes similares o relacionadas:

Procesador digital de señales y dispositivo de comunicación de banda base, del 5 de Noviembre de 2018, de MediaTek Sweden AB: Una unidad de ejecución de vectores para su uso en un procesador digital de señales que tiene un núcleo de procesador, […]

Procesador digital de señales y método para direccionar una memoria en un procesador digital de señales, del 18 de Octubre de 2017, de MediaTek Sweden AB: Un procesador digital de señales que comprende al menos una unidad funcional, que puede ser una unidad de ejecución de vectores , o un acelerador, […]

Procesador de señal digital y dispositivo de comunicación de banda base, del 16 de Agosto de 2017, de MediaTek Sweden AB: Un procesador de señal digital que comprende: - un núcleo de procesador que incluye una unidad de ejecución de enteros […]

Arquitectura híbrida SIMD/MIMD dinámicamente reconfigurable de un coprocesador para sistemas de visión, del 4 de Julio de 2013, de UNIVERSIDADE DE SANTIAGO DE COMPOSTELA: La presente invención se refiere a una arquitectura híbrida Simple Instrucción-Múltiples Datos (SIMD)/Múltiples Instrucciones-Múltiples Datos (MIMD), dinámicamente […]

Arquitectura híbrida SIMD/MIMD dinámicamente reconfigurable de un coprocesador para sistemas de visión, del 4 de Julio de 2013, de UNIVERSIDADE DE SANTIAGO DE COMPOSTELA: La presente invención se refiere a una arquitectura híbrida Simple Instrucción-Múltiples Datos (SIMD)/Múltiples Instrucciones-Múltiples Datos (MIMD), dinámicamente […]

ARQUITECTURA HÍBRIDA SIMD/MIMD DINÁMICAMENTE RECONFIGURABLE DE UN COPROCESADOR PARA SISTEMAS DE VISIÓN, del 29 de Noviembre de 2012, de UNIVERSIDADE DE SANTIAGO DE COMPOSTELA: La presente invención se refiere a una arquitectura híbrida Simple Instrucción-Múltiples Datos (SIMD)/Múltiples Instrucciones-Múltiples Datos (MIMD), […]

ARQUITECTURA HÍBRIDA SIMD/MIMD DINÁMICAMENTE RECONFIGURABLE DE UN COPROCESADOR PARA SISTEMAS DE VISIÓN, del 29 de Noviembre de 2012, de UNIVERSIDADE DE SANTIAGO DE COMPOSTELA: La presente invención se refiere a una arquitectura híbrida Simple Instrucción-Múltiples Datos (SIMD)/Múltiples Instrucciones-Múltiples Datos (MIMD), […]

Dispositivo de direccionamiento para procesador paralelo, del 15 de Agosto de 2012, de THALES: Procesador paralelo que comprende procesadores elementales que comprenden cada uno al menos unaunidad de cálculo y al menos una memoria que incluye palabras […]

SISTEMA DE PROCESAMIENTO DE DATOS Y DISPOSITIVO DE COMPUTACIÓN, del 12 de Marzo de 2012, de STARLAB BARCELONA SL: Sistema de procesamiento de datos y dispositivo de computación.

El sistema comprende:

- unos dispositivos de computación que procesan en paralelo […]

SISTEMA DE PROCESAMIENTO DE DATOS Y DISPOSITIVO DE COMPUTACIÓN, del 12 de Marzo de 2012, de STARLAB BARCELONA SL: Sistema de procesamiento de datos y dispositivo de computación.

El sistema comprende:

- unos dispositivos de computación que procesan en paralelo […]

REDES NEURONALES., del 1 de Enero de 2004, de BRITISH AEROSPACE: Dispositivo para tratar datos que representan una pluralidad de ejemplos, con lo que se determina una plantilla genérica que representa dichos ejemplos, donde dicho dispositivo […]