Método y sistema de filtrado adaptativo basado en una sub-banda de error.

Un método de filtrado adaptativo ajustado por al menos un algoritmo de mínimos cuadrados LMS sobre la base de una sub-banda de error,

que comprende:

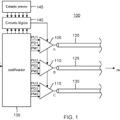

recibir, por un filtro adaptativo, una señal de entrada, realizar un procesamiento de filtrado adaptativo sobre la señal de entrada en función de un factor de ponderación de filtrado adaptativo actualmente memorizado en el filtro adaptativo, con el fin de obtener L señales de filtrado adaptativo, y transmitir las L señales de filtrado adaptativo a un subtractor;

recibir, por el subtractor, una señal de referencia y las L señales de filtrado adaptativo, realizar un cálculo en función de la señal de referencia y de las L señales de filtrado adaptativo para obtener una señal de error, y transmitir la señal de error a un filtro de sub-banda de error, en donde la señal de referencia es una señal generada después de que la señal de entrada pase a través de un canal real;

recibir, por el filtro de sub-banda de error, la señal de error, realizar un procesamiento de filtrado de análisis de subbanda sobre la señal de error para obtener N señales de sub-banda de error, y transmitir las N señales de subbanda de error a un actualizador de ponderación adaptativa,

recibir, por 20 un filtro de análisis de señal de entrada, la señal de entrada, realizar un procesamiento de filtrado de análisis de sub-banda sobre la señal de entrada para obtener N señales de sub-banda de entrada, y transmitir las N señales de sub-banda de entrada al actualizador de ponderación adaptativa; y

recibir, por el actualizador de ponderación adaptativa, las N señales de sub-banda de error y las M señales de sub banda de entrada, efectuar en cálculo función de las N señales de sub-banda de error y de las M señales de subbanda de entrada para obtener una nueva ponderación del filtrado adaptativo, y sustituir la ponderación de filtrado adaptativo actualmente memorizada en el filtro adaptativo por la nueva ponderación de filtrado adaptativo; en donde el filtro adaptativo tiene L ramas que comprenden una primera rama a una L-ésima rama, y cada rama tiene un puerto de entrada y un puerto de salida, en donde L es un número entero positivo;

cuando L es igual a 1, M multiplicadores, M-1 sumadores y M-1 retardadores de reloj M están dispuestos en la Lésima rama, en donde los M multiplicadores son un multiplicador 0 a un multiplicador M-1, los M-1 sumadores son un sumador 1 a un sumador M-1 y los M-1 retardadores de reloj M son un retardador 1 de reloj M a un retardador M- 1 de reloj M; cada retardador tiene un puerto de entrada y un puerto de salida, cada multiplicador tiene un puerto de entrada y un puerto de salida y cada sumador tiene dos puertos de entrada y un puerto de salida, M es un número entero positivo, y un puerto de entrada de la L-ésima rama está conectado a puertos de entrada del multiplicador 0 al multiplicador M-1, un puerto de salida del multiplicador 0 está conectado a un puerto de entrada del retardador 1 de reloj M, un puerto de salida de cada uno de un multiplicador 1 al multiplicador M-1 está conectado a un puerto de entrada de cada uno del sumador 1 al sumador M-1 y un puerto de salida de cada uno del retardador 1 de reloj M al retardador M-1 de reloj M está conectado al otro puerto de entrada del sumador 1 al sumador M-1;

a continuación, la recepción, por un filtro adaptativo, de una señal de entrada, realizando un procesamiento de filtrado adaptativo sobre la señal de entrada en función de una ponderación de filtrado adaptativo actualmente memorizada en el filtro adaptativo de manera que se obtenga una señal de filtrado adaptativo comprende: en la 1ª rama, recibir, por cada uno del multiplicador 0 al multiplicador M-1, la señal de entrada por intermedio del puerto de entrada de la L-ésima rama, y efectuar una multiplicación sobre la señal de entrada en función de una ponderación de filtro adaptativo memorizada en cada uno de los multiplicadores, para obtener una señal de salida de multiplicador generada por cada uno del multiplicador 0 al multiplicador M-1; proporcionar, a la salida, por cada uno del multiplicador 0 al multiplicador M-1, por intermedio de un puerto de salida de cada uno del multiplicador 0 al multiplicador M-1, la señal de salida del multiplicador generada por cada uno del multiplicador 0 al multiplicador M-1; efectuar, por cada uno del retardador 1 de reloj M al retardador M-1 de reloj M, un procesamiento de retardo de reloj M sobre una señal recibida en un puerto de entrada de cada uno del retardador 1 de reloj M al retardador M-1 de reloj M, para obtener una señal de retardo de reloj M generada por cada uno del retardador 1 de reloj M al retardador M-1 de reloj M; proporcionar, a la salida, por cada uno del retardador 1 de reloj M al retardador M-1 de reloj M, por intermedio del puerto de salida de cada uno del retardador 1 de reloj M al retardador M-1 de reloj M, la señal de retardo de reloj M generada por cada uno del retardador 1 de reloj M al retardador M-1 de reloj M; efectuar, por el sumador 1 al sumador M-1, un procesamiento de adición sobre las señales recibidas por intermedio de dos puertos 60 de entrada que corresponden a cada uno del sumador 1 al sumador M-1, para obtener una señal de salida de sumador generada por cada uno del sumador 1 al sumador M-1, y proporcionar, a la salida, por cada uno del sumador 1 al sumador M-1, por intermedio de un puerto de salida correspondiente a cada uno del sumador 1 al sumador M-1, la señal de salida del sumador generada por cada uno del sumador 1 al sumador M-1; y

cuando L es mayor que 1, un retardador de reloj (L-1), M multiplicadores, M-1 sumadores y M-1 retardadores de reloj M están dispuestos en la L-ésima rama, en donde los M multiplicadores son un multiplicador 0 a un multiplicador M- 1, los M-1 sumadores son un sumador 1 a un sumador M-1 y los M-1 retardadores de reloj M son un retardador 1 de reloj M a un retardador M-1 de reloj M; cada retardador tiene un puerto de entrada y puerto de salida, cada multiplicador tiene un puerto de entrada y un puerto de salida y cada sumador tiene dos puertos de entrada y un puerto de salida; y en la L-ésima rama, un puerto de entrada de la L-ésima rama está conectado a un puerto de entrada del retardador de reloj (L-5 1), un puerto de salida del retardador de reloj (L-1) está conectado a puertos de entrada de todos los multiplicadores, un puerto de salida del multiplicador 0 está conectado a un puerto de entrada del retardador 1 de reloj M, un puerto de salida de cada uno del multiplicador 1 al multiplicador M-1 está conectado a un puerto de entrada de cada uno del sumador 1 al sumador M-1, y un puerto de salida de cada uno del retardador 1 de reloj M al retardador M-1 de reloj M está conectado al otro puerto de entrada de cada uno del sumador 1 al sumador M-1;

a continuación, la recepción, por un filtro adaptativo, de una señal de entrada, la realización de un procesamiento de filtrado adaptativo sobre la señal de entrada en función de una ponderación de filtrado adaptativo actualmente memorizada en el filtro adaptativo, con el fin de obtener una señal de filtrado adaptativo comprende:

en la L-ésima rama, la recepción, por el retardador de reloj (L-1), de la señal de entrada por intermedio del puerto de entrada del retardador de reloj (L-1), y realizar un procesamiento de retardo de reloj (L-1) sobre la señal de entrada para generar una señal de retardo de reloj (L-1); proporcionar, a la salida, por el retardador de reloj (L-1), la señal de retardo de reloj (L-1) por intermedio del puerto de salida del retardador de reloj (L-1); la recepción, por cada uno del multiplicador 0 al multiplicador M-1, de la señal de retardo de reloj (L-1) por intermedio del puerto de entrada de la Lésima rama, y realizar una multiplicación sobre la señal de retardo de reloj (L-1) en función de una ponderación de filtrado adaptativo memorizada en cada uno de los multiplicadores, para obtener una señal de salida del multiplicador generada por cada uno del multiplicador 0 al multiplicador M-1; proporcionar, a la salida, por cada uno del multiplicador 0 al multiplicador M-1 por intermedio de un puerto de salida de cada uno del multiplicador 0 al multiplicador M-1, la señal de salida del multiplicador generada por cada uno del multiplicador 0 al multiplicador M-1; realizar, por cada uno del retardador 1 de reloj M al retardador M-1 de reloj M, un procesamiento de retardo de reloj M sobre una señal recibida en un puerto de entrada de cada uno del retardador 1 de reloj M al retardador M-1 de reloj M, con el fin de obtener una señal de retardo generada por cada uno del retardador 1 de reloj M al retardador M-1 de reloj M; proporcionar, a la salida, por cada uno del retardador 1 de reloj M al retardador M-1 de reloj M por intermedio del puerto de salida de cada uno del retardador 1 de reloj M al retardador M-1 de reloj M, la señal de retardo generada por cada uno del retardador 1 de reloj M al retardador M-1 de reloj M; realizar, por cada uno del sumador 1 al sumador M-1, un procesamiento de adición sobre las señales recibidas por intermedio de dos puertos de entrada correspondientes a cada uno del sumador 1 al sumador M-1, con el fin de obtener una señal de salida de sumador generada por cada uno del sumador 1 al sumador M-1, y proporcionar, a la salida, por cada uno del sumador 1 al sumador M-1, por intermedio de un puerto de salida correspondiente a cada uno del sumador 1 al sumador M-1, la señal de salida de sumador generada por cada uno del sumador 1 al sumador M-1.

Tipo: Patente Internacional (Tratado de Cooperación de Patentes). Resumen de patente/invención. Número de Solicitud: PCT/CN2012/082224.

Solicitante: HUAWEI TECHNOLOGIES CO., LTD..

Nacionalidad solicitante: China.

Dirección: Huawei Administration Building, Bantian Longgang District , Shenzhen, Guangdong 518129 CHINA.

Inventor/es: SHI,DONGYUAN, HE,DONGMEI, CAI,MENG.

Fecha de Publicación: .

Clasificación Internacional de Patentes:

- H04L25/03 ELECTRICIDAD. › H04 TECNICA DE LAS COMUNICACIONES ELECTRICAS. › H04L TRANSMISION DE INFORMACION DIGITAL, p. ej. COMUNICACION TELEGRAFICA (disposiciones comunes a las comunicaciones telegráficas y telefónicas H04M). › H04L 25/00 Sistemas de banda base. › Redes de formación para emisor o receptor, p. ej. redes de formación adaptables.

PDF original: ES-2625275_T3.pdf

Patentes similares o relacionadas:

Ecualización inteligente para un sistema multifásico de tres transmisores, del 29 de Julio de 2020, de QUALCOMM INCORPORATED: Un sistema de tres transmisores para transmitir símbolos multifásicos sucesivos, que comprende:

un codificador configurado para codificar […]

Ecualización inteligente para un sistema multifásico de tres transmisores, del 29 de Julio de 2020, de QUALCOMM INCORPORATED: Un sistema de tres transmisores para transmitir símbolos multifásicos sucesivos, que comprende:

un codificador configurado para codificar […]

Información de control en un sistema de comunicación inalámbrica, del 15 de Julio de 2020, de QUALCOMM INCORPORATED: Un procedimiento para enviar datos de tráfico e información de control en un sistema de comunicación inalámbrica, que comprende: realizar conformación de haces […]

Asignación dinámica de recursos ACK en un sistema de comunicación inalámbrica, del 15 de Abril de 2020, de QUALCOMM INCORPORATED: Un procedimiento para comunicación inalámbrica, que comprende: recibir una asignación semipersistente para un recurso de acuse de recibo, ACK, para un equipo de usuario, […]

Asignación dinámica de recursos ack en un sistema de comunicación inalámbrica, del 15 de Abril de 2020, de QUALCOMM INCORPORATED: Un procedimiento para comunicación inalámbrica, que comprende: recibir una asignación semipersistente para un equipo de usuario, UE, siendo válida […]

Señal de sincronización extendida para la detección de índice de símbolos, del 15 de Abril de 2020, de QUALCOMM INCORPORATED: Un procedimiento de comunicación inalámbrica, que comprende: determinar una primera secuencia de señal de sincronización extendida, […]

Método y dispositivo para cuantificar y retroalimentar la información de canal y precodificar datos, del 8 de Abril de 2020, de ZTE CORPORATION: Un método para cuantificar y retroalimentar la información de canal en un sistema polarizado doble, caracterizado porque comprende: recibir una señal piloto de […]

Transmisor con equilibrio de polarización, del 1 de Abril de 2020, de Tianma Micro-Electronics Co., Ltd: Un transmisor que comprende: un generador de datos de señalización L1 (Capa 1), configurado para generar datos de señalización […]

Procedimiento y aparato para la conformación de haces de información de control en un sistema de comunicación inalámbrica, del 25 de Marzo de 2020, de QUALCOMM INCORPORATED: Un procedimiento de envío datos de tráfico e información de control en un sistema de comunicación inalámbrica, que comprende: realizar […]