Mejora de la eficiencia energética de un controlador de línea.

Un equipo que comprende:

un primer controlador de línea (66);

un segundo controlador de línea (68);

un multiplicador de voltaje (64); y

caracterizado por que un circuito lógico de control acoplado al primer controlador de línea (66) y al segundo controlador de línea (68) y configurado para deshabilitar el multiplicador de voltaje (64) cuando tanto una primera señal de control asociada con el primer controlador de línea (66) como una segunda señal de control asociada con el segundo controlador de línea (68) indican un estado deshabilitado del multiplicador de voltaje, en donde el primer controlador de línea (66) y el segundo controlador de línea (68) están configurados para conmutar entre un nivel de voltaje bajo y un nivel de voltaje alto de una fuente de alimentación para amplificar una señal de pico baja o alta, respectivamente; el primer controlador de línea (66) y el segundo controlador de línea (68) utilizan el multiplicador de voltaje (64) para conmutar el valor del voltaje de la fuente de alimentación desde el nivel bajo hasta valor alto.

Tipo: Patente Internacional (Tratado de Cooperación de Patentes). Resumen de patente/invención. Número de Solicitud: PCT/US2010/030298.

Solicitante: HUAWEI TECHNOLOGIES CO., LTD..

Nacionalidad solicitante: China.

Dirección: Building B1-3-A, Huawei Industrial Base, Bantian, Longgang District Shenzhen, Guangdong 518129 CHINA.

Inventor/es: LONG,Guozhu, XIAO,RUIJIE, ZHAO,ZHILEI.

Fecha de Publicación: .

Clasificación Internacional de Patentes:

- H04L25/02 ELECTRICIDAD. › H04 TECNICA DE LAS COMUNICACIONES ELECTRICAS. › H04L TRANSMISION DE INFORMACION DIGITAL, p. ej. COMUNICACION TELEGRAFICA (disposiciones comunes a las comunicaciones telegráficas y telefónicas H04M). › H04L 25/00 Sistemas de banda base. › Detalles.

PDF original: ES-2546479_T3.pdf

Fragmento de la descripción:

Mejora de la eficiencia energética de un controlador de línea Antecedentes La tecnología de Línea de Abonado Digital (DSL) es una tecnología de transmisión de datos de gran ancho de banda y/o alta velocidad que se implementa utilizando cables de par trenzado, por ejemplo, pares trenzados no apantallados. Por ejemplo, las tecnologías DSL incluyen la Línea de Abonado Digital Asimétrica (ADSL) , la Línea de Abonado Digital de Muy Alta Tasa de Bits (VDSL) , la Línea de Abonado Digital basada en la Red Digital de Servicios Integrados (RDSI) (IDSL) , y la Línea de Abonado Digital de Alta Velocidad de Un Solo Par (SHDSL) . Habitualmente, en muchos sistemas de comunicaciones DSL se utiliza un amplificador de potencia (PA) , que en ocasiones recibe el nombre de controlador de línea, para amplificar la señal de salida antes de que ésta sea enviada a los medios de transmisión, por ejemplo, cables de par trenzado. El controlador de línea puede consumir un gran porcentaje de la energía total utilizada por el sistema DSL. Con la mejora de las tecnologías de semiconductores se ha reducido considerablemente el consumo de energía del sistema DSL para el procesamiento digital de las señales, pero el consumo de energía del controlador de línea sigue siendo sustancialmente alto. Como resultado, el controlador de línea puede consumir incluso un porcentaje mayor de la energía total utilizada en el sistema DSL.

El documento US 6.531.902 B1 divulga un controlador de línea que comprende: un detector de picos que dispone de un dispositivo para calcular la magnitud de la señal y un elemento de retardo lógico, en donde el detector de picos está preparado para recibir una señal de datos, el detector de picos está preparado para generar una primera señal lógica de salida cuando la señal de datos se encuentra por debajo de un valor umbral y para generar una segunda señal lógica de salida cuando la señal de datos excede el valor umbral, el dispositivo para calcular la magnitud de la señal está preparado para calcular la cantidad en la que la señal de datos excede el valor umbral, el elemento de retardo lógico está preparado para recibir una de las señales lógicas, la primera o la segunda, el elemento de retardo lógico está preparado para generar una de las señales lógicas de retardo, la primera o la segunda, en función de la cantidad en la que la señal de datos excede el valor umbral.

El documento de JOHN WILSON "Zero-overhead class-g drivers improve power efficiency in ADSL line cards (Los controladores de clase g y sobrecarga cero mejoran la eficiencia energética en las tarjetas de línea ADSL) " divulga un controlador de línea de Clase G que utiliza dos raíles (canales) de alimentación de energía, en donde se utiliza un voltaje alto cuando la amplitud de la señal es grande y se utiliza un voltaje bajo cuando la amplitud de la señal es pequeña.

El documento US 2004/001586 A1 divulga un controlador de línea que comprende: un detector de picos que dispone de un dispositivo para calcular la magnitud de la señal y un elemento de retardo lógico, en donde el detector de picos está preparado para recibir una señal de datos, el detector de picos está preparado para generar una primera señal lógica de salida cuando la señal de datos se encuentra por debajo de un valor umbral y para generar una segunda señal lógica cuando la señal de datos excede el valor umbral, el dispositivo para calcular la magnitud de la señal está preparado para calcular una cantidad en la que la señal de datos excede el valor umbral, el elemento de retardo lógico está preparado para recibir una de las señales lógicas, la primera o la segunda, el elemento de retardo lógico está preparado para generar una señal lógica de retardo de salida, la primera o la segunda, en función de la cantidad en la que la señal de datos excede el valor umbral.

Resumen En un modo de realización, la divulgación incluye un equipo que comprende un primer controlador de línea, un segundo controlador de línea, un circuito multiplicador de voltaje (charge pump) , y un circuito lógico de control acoplado al primer controlador de línea y al segundo controlador de línea, y configurado para deshabilitar el multiplicador de voltaje cuando tanto una primera señal de control asociada con el primer controlador de línea como una segunda señal de control asociada con el segundo controlador de línea indican un estado de deshabilitado del multiplicador de voltaje, en donde el primer controlador de línea y el segundo controlador de línea están configurados para conmutar entre un nivel bajo y un nivel alto de voltaje de una fuente de alimentación con el fin de amplificar una señal de pico baja o alta, respectivamente; el primer controlador de línea y el segundo controlador de línea utilizan el multiplicador de voltaje para conmutar el valor del voltaje de la fuente de alimentación desde el nivel bajo al valor alto.

En otro modo de realización, la divulgación incluye un componente de red que comprende al menos un procesador configurado para implementar un método que incluye recibir una primera señal de control y una segunda señal de control, deshabilitar un multiplicador de voltaje cuando tanto la primera señal de control como la segunda señal de control indican un estado deshabilitado del multiplicador de voltaje, y activar el multiplicador de voltaje para aumentar un voltaje cuando la primera señal de control, la segunda señal de control o ambas indican un estado activo del multiplicador de voltaje; en donde el primer controlador de línea y el segundo controlador de línea están configurados para conmutar entre un nivel bajo y un nivel alto de voltaje de una fuente de alimentación con el fin de amplificar una señal de pico baja o alta, respectivamente; el primer controlador de línea y el segundo controlador de

línea utilizan el multiplicador de voltaje para conmutar el valor del voltaje de la fuente de alimentación desde el nivel bajo al valor alto.

Estas y otras características se comprenderán más claramente a partir de la siguiente descripción detallada tomada conjuntamente con los dibujos y las reivindicaciones que se acompañan.

Breve descripción de los dibujos Para una mejor comprensión de esta divulgación, a continuación se hace referencia a la siguiente descripción abreviada, tomada conjuntamente con los dibujos adjuntos y la descripción detallada, en donde los mismos números de referencia representan los mismos componentes.

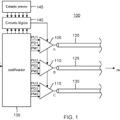

La FIG. 1 es un diagrama esquemático de un modo de realización de un controlador de línea.

La FIG. 2 es un diagrama esquemático de un modo de realización de un controlador de línea de doble canal.

La FIG. 3 es un diagrama esquemático de otro modo de realización de un controlador de línea.

La FIG. 4 es un diagrama esquemático de otro modo de realización de un controlador de línea.

FIG. 5 es un diagrama esquemático de un modo de realización de un esquema de control de un controlador de línea.

FIG. 6 es un diagrama esquemático de otro modo de realización de un controlador de línea de doble canal.

FIG. 7 es un diagrama esquemático de otro modo de realización de un controlador de línea de doble canal.

FIG. 8 es un diagrama esquemático de otro modo de realización de un controlador de línea de doble canal.

FIG. 9 es un diagrama esquemático de otro modo de realización de un controlador de línea de doble canal.

FIG. 10 es un diagrama esquemático de otro modo de realización de un controlador de línea multicanal.

Descripción detallada Se debe entender desde el comienzo que, aunque a continuación se proporciona una implementación ilustrativa de uno o más modos de realización, los sistemas y/o los métodos que se divulgan se pueden implementar mediante cuantas técnicas se desee, ya sean conocidas en la actualidad o existentes. La divulgación no debe limitarse de ningún modo a las implementaciones, dibujos y técnicas de ejemplo ilustrados más abajo, incluyendo los ejemplos de diseño e implementación que se ilustran y describen en la presente solicitud, sino que se puede modificar dentro del alcance de las reivindicaciones adjuntas junto con el alcance completo de sus equivalentes.

La amplitud de una señal DSL transmitida mediante, por ejemplo, tecnologías de modulación como Modulación por Multitono Discreto (DMT) o Multiplexación por División Ortogonal de Frecuencia (OFDM) , puede tener una relación entre el valor de pico y el valor promedio relativamente alta, en donde el pico de la señal puede variar entre valores relativamente altos y bajos. Por otro lado, a lo largo del tiempo total de la transmisión el pico alto de la señal puede aparecer con menos frecuencia... [Seguir leyendo]

Reivindicaciones:

1. Un equipo que comprende:

un primer controlador de línea (66) ;

un segundo controlador de línea (68) ;

un multiplicador de voltaje (64) ; y caracterizado por que un circuito lógico de control acoplado al primer controlador de línea (66) y al segundo controlador de línea (68) y configurado para deshabilitar el multiplicador de voltaje (64) cuando tanto una primera señal de control asociada con el primer controlador de línea (66) como una segunda señal de control asociada con el segundo controlador de línea (68) indican un estado deshabilitado del multiplicador de voltaje, en donde el primer controlador de línea (66) y el segundo controlador de línea (68) están configurados para conmutar entre un nivel de voltaje bajo y un nivel de voltaje alto de una fuente de alimentación para amplificar una señal de pico baja o alta, respectivamente; el primer controlador de línea (66) y el segundo controlador de línea (68) utilizan el multiplicador de voltaje (64) para conmutar el valor del voltaje de la fuente de alimentación desde el nivel bajo hasta valor alto.

2. El equipo de la reivindicación 1, en donde la primera señal de control, la segunda señal de control, o ambas indican el estado deshabilitado del multiplicador de voltaje, un estado preparado del multiplicador de voltaje, o un estado activo del multiplicador de voltaje.

3. El equipo de la reivindicación 1, en donde la lógica de control está acoplada a un tercer controlador de línea y está configurada para deshabilitar el multiplicador de voltaje cuando la primera señal de control, la segunda señal de control y una tercera señal de control asociada al tercer controlador de línea indican un estado deshabilitado del multiplicador de voltaje.

4. El equipo de la reivindicación 1, en donde el circuito lógico de control comprende un primer diodo (62) situado entre el multiplicador de voltaje (64) y el primer controlador de línea (66) , un segundo diodo (63) situado entre el multiplicador de voltaje (64) y el segundo controlador de línea (68) , un condensador (65) acoplado al primer diodo (62) , al segundo diodo (63) , y al multiplicador de voltaje (64) , un primer interruptor (67) situado entre el primer diodo

(62) y el condensador (65) , un segundo interruptor (69) situado entre el segundo diodo (63) y el condensador (65) , y un espejo de corriente (61) acoplado al multiplicador de voltaje (64) y al condensador (65) .

5. El equipo de la reivindicación 4, en donde el primer diodo (62) y el segundo diodo (63) se someten a polarización directa, el primer interruptor (67) , el segundo interruptor (69) , o ambos están cerrados, y el condensador (65) se carga a través del espejo de corriente (61) cuando la primera señal de control y la segunda señal de control indican el estado deshabilitado del multiplicador de voltaje.

6. El equipo de la reivindicación 4, en donde el multiplicador de voltaje (64) se activa, el primer diodo (62) o el segundo diodo (63) se somete a polarización inversa, el primer interruptor (67) o el segundo interruptor (69) se cierra, y el condensador (65) se descarga para elevar el voltaje para uno de los controladores de línea, primero (66)

o segundo (68) , cuando una de las señales de control, la primera o la segunda, indica un estado activo del multiplicador de voltaje.

7. El equipo de la reivindicación 4, en donde la lógica de control comprende un tercer diodo, uno de los interruptores, primero o segundo, se cierra cuando una de las señales de control, primera o segunda, indica un estado activo del controlador de línea, y el primer o el segundo interruptor se abre y el condensador se carga a través del espejo de corriente cuando ninguna de las señales de control, ni la primera ni la segunda, indican un estado activo del multiplicador de voltaje.

8. El equipo de la reivindicación 4, en donde el espejo de corriente no se desconecta cuando se deshabilita el multiplicador de voltaje, y

en donde el espejo de corriente se desconecta cuando se desconectan el primer controlador de línea y el segundo controlador de línea 9. Un componente de red, caracterizado por que comprende:

al menos un procesador configurado para implementar un método que comprende:

recibir una primera señal de control y una segunda señal de control;

deshabilitar un multiplicador de voltaje cuando tanto la primera señal de control como la segunda señal de control indican un estado deshabilitado del multiplicador de voltaje; y

activar el multiplicador de voltaje para elevar un voltaje cuando la primera señal de control, la segunda señal de control, o ambas indican un estado activo del multiplicador de voltaje; en donde un primer controlador de línea y un segundo controlador de línea están configurados para conmutar entre un nivel de voltaje bajo y un nivel de voltaje alto de una fuente de alimentación para amplificar una señal de pico baja o alta, respectivamente; el primer controlador de línea y el segundo controlador de línea utilizan el multiplicador de voltaje para conmutar el valor del voltaje de la fuente de alimentación desde el nivel bajo hasta el valor alto.

10. El componente de red de la reivindicación 9, en donde la primera señal de control, la segunda señal de control, o ambas indican el estado deshabilitado del multiplicador de voltaje cuando se predice una señal de entrada de pico de entrada relativamente baja, o indican el estado activo del multiplicador de voltaje cuando se predice una señal de entrada de pico relativamente ata.

11. El componente de red de la reivindicación 9, en donde el método comprende, además, deshabilitar el multiplicador de voltaje después de que el tiempo que empieza desde la detección de que el multiplicador de voltaje se encuentra en estado activo exceda un tiempo predeterminado.

Patentes similares o relacionadas:

Ecualización inteligente para un sistema multifásico de tres transmisores, del 29 de Julio de 2020, de QUALCOMM INCORPORATED: Un sistema de tres transmisores para transmitir símbolos multifásicos sucesivos, que comprende:

un codificador configurado para codificar […]

Ecualización inteligente para un sistema multifásico de tres transmisores, del 29 de Julio de 2020, de QUALCOMM INCORPORATED: Un sistema de tres transmisores para transmitir símbolos multifásicos sucesivos, que comprende:

un codificador configurado para codificar […]

Estimación de canal de antenas múltiples de grupo iterativo ordenado disperso, del 22 de Julio de 2020, de Altiostar Networks, Inc: Un método implementado por procesador para proporcionar una respuesta de impulso de canal estimado final, implementable por uno o más procesadores de datos que forman parte […]

Método y dispositivo de transmisión de datos de red de área local inalámbrica, del 15 de Julio de 2020, de HUAWEI TECHNOLOGIES CO., LTD.: Un método de transmisión de información de estimación de canal en un sistema de comunicación, en un extremo de transmisión, que comprende: […]

Procedimiento la lucha antiinterferencias por filtrado espacial o filtrado espacio-temporal en un receptor multicanal, del 24 de Junio de 2020, de THALES: Procedimiento de recepción de una señal y de rechazo de las interferencias en un receptor multicanal , comprendiendo dicho procedimiento las […]

Acuses de recibo retardados para comunicación de baja sobrecarga en una red, del 24 de Junio de 2020, de QUALCOMM INCORPORATED: Un procedimiento para comunicación entre estaciones a través de un medio compartido , comprendiendo el procedimiento: recibir una primera […]

Extremo frontal de transceptor para comunicación mediante líneas eléctricas, del 13 de Mayo de 2020, de Landis+Gyr Technologies, LLC: Circuito de comunicación mediante líneas eléctricas para su uso en un sistema de comunicación mediante líneas eléctricas, comprendiendo el circuito (100; […]

Procedimiento de asociación univalente y unívoca entre emisores y receptores de transmisión a partir del canal de propagación, del 25 de Marzo de 2020, de THALES: Procedimiento de asociación univalente y unívoca, antes del establecimiento de un protocolo de comunicación, a partir del canal (AU_CP) de propagación […]

Estación base, equipo de usuario y métodos en los mismos en un sistema de comunicaciones, del 25 de Marzo de 2020, de TELEFONAKTIEBOLAGET LM ERICSSON (PUBL): Un método en un equipo de usuario para transmitir información del estado de canal a una primera estación base , cuyo equipo de usuario está comprendido […]

Estación base, equipo de usuario y métodos en los mismos en un sistema de comunicaciones, del 25 de Marzo de 2020, de TELEFONAKTIEBOLAGET LM ERICSSON (PUBL): Un método en un equipo de usuario para transmitir información del estado de canal a una primera estación base , cuyo equipo de usuario está comprendido […]