Método de transmisión y de recepción de información de control en enlace ascendente y un terminal y una estación base.

Un método para transmitir Información de Control en Enlace Ascendente,

que comprende:

calcular (501) el número Q' de símbolos de modulación ocupados por la Información de Control en Enlace Ascendente, UCI, a transmitir;

dividir (502) una secuencia de bits de información de la UCI a transmitir en dos partes;

utilizar (503) un código de Reed Muller RM (32, O) para codificar cada parte de la secuencia de bits de información de la UCI a transmitir para obtener una secuencia de bits codificada entre **Fórmula** bits, respectivamente;

realizar (503) una correspondencia de tasas para cada secuencia de bits codificada en **Fórmula** bits respectivamente para establecer una primera secuencia de bits codificada en **Fórmula**bits a una secuencia de bits codificada en bits por intermedio de una correspondencia de tasa y para establecer una segunda secuencia de bits codificada en **Fórmula** bits a una secuencia de bits codificada en bits por intermedio de una correspondencia de tasa, en donde Qm es un orden de modulación correspondiente a la UCI a transmitir y se refiere a un redondeo al valor superior; y

efectuar un mapeado (504) de las dos partes de la secuencia de bits codificadas que han sufrido una correspondencia de tasa en un Canal Compartido de Enlace Ascendente Físico, PUSCH y transmitir las dos partes de la secuencia de bits codificadas a una estación base;

estando dicho método caracterizado por cuanto que:

el establecimiento de la primera secuencia de bits codificada en **Fórmula** bits a una secuencia de bits codificada en bits por intermedio de una correspondencia de tasa comprende:

si el valor de es menor que o igual a **Fórmula**, seleccionar los primeros bits en la primera secuencia de bits codificada en **Fórmula** bits;

si el valor de es mayor que **Fórmula**, según , realizar la correspondencia

de tasa para establecer la primera secuencia de bits codificada en **Fórmula** bits a una secuencia de bits codificada en bits en donde qi es una salida de secuencia de bits codificada después de que la primera secuencia de bits codificada en **Fórmula** bits se establezca a una secuencia de bits codificada en mediante una correspondencia de tasa, siendo , la primera secuencia de bits codificada en **Fórmula** bits, On es un bits en la secuencia de bits de información correspondiente a la primera secuencia de bits codificada en **Fórmula** bits, Mj,n es una secuencia básica de código de RM (32, O) y O' es el número de bits de la secuencia de bits de información correspondiente a la primera secuencia de bits codificada en **Fórmula** bits y

el establecimiento de la segunda secuencia de bits codificada en **Fórmula** bits a una secuencia de bits codificada en bits por intermedio de la correspondencia de tasa comprende:

Tipo: Patente Internacional (Tratado de Cooperación de Patentes). Resumen de patente/invención. Número de Solicitud: PCT/CN2011/075504.

Solicitante: HUAWEI TECHNOLOGIES CO., LTD..

Nacionalidad solicitante: China.

Dirección: HUAWEI ADMINISTRATION BUILDING BANTIAN LONGGANG DISTRICT SHENZHEN, GUANGDONG 518129 CHINA.

Inventor/es: LV,Yongxia, CHENG,YAN.

Fecha de Publicación: .

Clasificación Internacional de Patentes:

- H04L1/00 ELECTRICIDAD. › H04 TECNICA DE LAS COMUNICACIONES ELECTRICAS. › H04L TRANSMISION DE INFORMACION DIGITAL, p. ej. COMUNICACION TELEGRAFICA (disposiciones comunes a las comunicaciones telegráficas y telefónicas H04M). › Disposiciones para detectar o evitar errores en la información recibida.

PDF original: ES-2513596_T3.pdf

Fragmento de la descripción:

Método de transmisión y de recepción de información de control en enlace ascendente y un terminal y una estación base.

Campo de la Invención

La presente Invención se refiere al campo de las radiocomunicaciones y en particular, a un método para transmitir y recibir Información de Control en Enlace Ascendente (UCI), un terminal y una estación base.

Antecedentes de la Invención

Un sistema de TDD (Time División Duplexlng, Duplexaclón por División de Tiempo) envía y recibe Información en un canal de frecuencia, pero la recepción y el envío de la Información utilizan diferentes Intervalos temporales de una portadora de frecuencia. La transmisión de datos de la sub-trama de enlace descendente corresponde a UCI tal como Información de respuesta, que se suele realimentar por Intermedio de una trama de enlace ascendente.

Un sistema de TDD LTE (Long Term Evolutlon, Evolución a Largo Plazo) incluye 7 configuraciones de sub-tramas de enlace ascendente-enlace descendente. En algunas de las configuraciones de sub-tramas de enlace ascendente- enlace descendente, el número de sub-tramas de enlace descendente es mayor que el número de sub-tramas de enlace ascendente y es posible que UCI correspondiente a la transmisión de datos de múltiples sub-tramas de enlace descendente necesiten realimentarse en la misma sub-trama de enlace ascendente, la UCI se suele codificar por intermedio de un código de RM (Reed Muller) (32, O) antes de que se transmita a la estación base.

Un sistema de LTE-A (Long Term Evolutlon Advanced, Evolución a Largo Plazo Avanzada) es un sistema de LTE más evolucionado y mejorado. En un sistema de TDD de LTE-A, se introduce la agregación de portadoras. Cuando un terminal accede a múltiples portadoras componentes simultáneamente, el terminal necesita realimentar la UCI en la misma portadora de enlace ascendente, en donde la UCI es la UCI de múltiples sub-tramas de enlace descendente desde múltiples portadoras componentes de enlace descendente. Por lo tanto, los bits ocupados por la UCI en una sub-trama de enlace ascendente aumentan en gran medida. Cuando el número de bits ocupados por UCI supera el número máximo de bits (11 bits) soportados por un código RM (32, O), es urgente establecer una solución para transmitir UCI, lo que no existía en la técnica anterior.

El documento de LG ELECTRONICS: Codificación de canal para UCI en PUSCH", 3GPP DRAFT; R1-1616 da a conocer la codificación de canal para UCI en el canal PUSCH.

El documento de CMCC, CATT, CATR, Ericsson, ST-Erlcsson, Huawei, HiSilicon, III, New Postcom, Potevio, ZTE: Forma de reenvío en soporte de carga útil de ACK/NACK mayor que 11 bits en Rel-1 TDD", 3GPP; R1-15776 da a conocer la codificación de RM dual se soporta para la carga útil de ACK/NACK mayor que 11 bits.

Huawei y Hisilicon: Sistemas de codificación de A/N para una gran carga útil utilizando DFT-OFDM", 3GPP; R1- 15247 da a conocer el sistema de codificación para el formato DFT-S-OFDM en el canal PUCCH.

Sumario de la Invención

Una forma de realización de la presente invención da a conocer un método para transmitir y recibir la UCI, un terminal y una estación base para transmitir la UCI para resolver el problema de que el número de bits ocupados supera el número máximo de bits soportados por el código de RM (32, O). La solución técnica de la presente invención es como sigue:

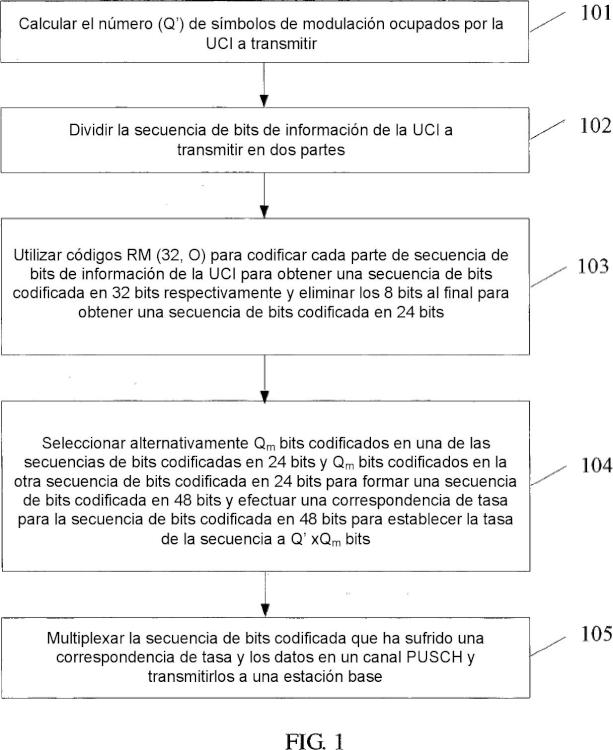

Un método para transmitir la UCI comprende:

calcular Q de símbolos de modulación ocupados por UCI a transmitir; dividir una secuencia de bits de información de la UCI a transmitir en dos partes;

utilizar un código de RM (32, O) para codificar cada parte de la secuencia de bits de información de la UCI a transmitir para obtener una secuencia de bits codificada en 32 bits respectivamente y la realización de una correspondencia de tasa para cada secuencia de bits codificada en 32 bits respectivamente para establecer una

primera secuencia de bits codificada en 32 bits para una secuencia de bits codificada en bits por

Intermedio de una correspondencia de tasa y para establecer una segunda secuencia de bits codificada en 32 bits

para una secuencia de bits codificada en (£?íí?/2T)xfi. bits por intermedio de una correspondencia de tasa, en donde Qm es el orden de modulación correspondiente a la UCI a transmitir y f 1 se refiere a un redondeo al valor superior y

el mapeado de las dos partes de secuencias de bits codificadas que han sufrido una correspondencia de tasa en un canal PUSCH y transmitir las dos partes de las secuencias de bits codificadas a una estación base.

en donde el establecimiento de la primera secuencia de bits codificada en 32 bits a una secuencia de bits codificada en bits por intermedio de una correspondencia de tasa incluye: si un valor de es menor que o

igual a 32, seleccionar los primeros b¡ts en |a pr¡mera secuencia de bits codificada en 32 bits; si el valor de

fe«l*aes mayorque 32, según q = >(/mod32) ^ = ), rea|¡zar una correspondencia de tasa

para establecer la primera secuencia de bits codificada en 32 bits a una secuencia de bits codificada en

bits en donde q es una salida de secuencia de bits codificada después de que la primera secuencia de bits

codificada en 32 bits se establezca a una secuencia de bits codificada en Íí?^]xQ, b¡ts pr ¡ntermedio de una

b¡ = Z(G.x^/.>mod2

correspondencia de tasa, siendo »-< ' (/= ,1,...,31) la primera secuencia de bits codificada en

32 bits, On es un bit en la secuencia de bits de información correspondiente a la primera secuencia de bits codificada en 32 bits, Mjn es una secuencia básica de un código de RM (32, O) y O es el número de bits de la secuencia de bits de información correspondiente a la primera secuencia de bits codificada en 32 bits;

el establecimiento de la segunda secuencia de bits codificada en 32 bits a una secuencia de bits codificada en (G-fG^xQ,, bits por intermedio de una correspondencia de tasa incluye: si el valor de ©ÍG^ljxg, es menor qUe o igual a 32, seleccionar primero los b¡ts en |a segunda secuencias de bits codificadas en 32 bit; si el

valor de es mayor que 32, según q. = )(/mod32) = ~\Q ^21)X £?» _1)X realizar una

correspondencia de tasa para establecer la secuencia de bits codificada en 32 bits a una secuencia de bits

codificada en (G-TG^xQ, b¡tS| en qonc|e q. es una salida de secuencia de bits codificada cada después de que se establezca la segunda secuencia de bits codificada en 32 bits a una secuencia de bits codificada en

bj = M jjná2

bits, por intermedio de una correspondencia de tasa, siendo »-o (j = ,1,...,31) la segunda

secuencia de bits codificada en 32 bits, On es un bit en la secuencia de bit de información correspondiente a la segunda secuencia de bits codificada en 32 bits, Mjn es una secuencia básica de un código de RM (32, O) y O es el número de la secuencia de bits de información correspondiente a la segunda secuencia de bits codificada en 32 bits.

En un aspecto de la idea inventiva, el mapeado de correspondencia de las dos partes de secuencias de bits codificadas que han sufrido una correspondencia de tasa en el canal PUSCH y la transmisión de las dos partes de las secuencias de bits codificadas a la estación base incluye: la concatenación de las dos partes de secuencias de bits codificadas que han sufrido una correspondencia de tasa para formar una nueva secuencia de bits, el mapeado de correspondencia de la nueva secuencia de bits en el canal PUSCH y la transmisión de la nueva secuencia de bits a la estación base o seleccionar alternativamente 4Q bits codificados en una de las dos partes de secuencias de bits codificadas que han sufrido una correspondencia de tasa y 4Qm bits codificados en la otra parte de las secuencias de bits codificadas que han sufrido una correspondencia de tasa para formar una nueva secuencia de bits, el mapeado de la nueva secuencia de bits en el canal PUSCH y la transmisión de la nueva secuencia de bits a la estación base o la selección alternativa de Qm bits codificados en una de las dos partes de las secuencias de bits codificadas que han sufrido una correspondencia de tasa y Qm bits codificados en la otra parte de las secuencias de bits codificadas que han sufrido una correspondencia de tasa; después de que se seleccionen los 4Qm bits codificados, conmutar el orden de selección alternativa de las dos partes de las secuencias de bits codificadas que han sufrido una correspondencia de tasa, prosiguiendo la selección alternativa de los bits codificados para formar una nueva secuencia de bits, el mapeado de la nueva secuencia de bits en el canal PUSCH y la transmisión de la nueva secuencia de bits a la estación... [Seguir leyendo]

Reivindicaciones:

1. Un método para transmitir Información de Control en Enlace Ascendente, que comprende:

calcular (51) el número Q' de símbolos de modulación ocupados por la Información de Control en Enlace Ascendente, UCI, a transmitir;

dividir (52) una secuencia de bits de información de la UCI a transmitir en dos partes;

utilizar (53) un código de Reed Muller RM (32, O) para codificar cada parte de la secuencia de bits de información de la UCI a transmitir para obtener una secuencia de bits codificada entre 32 bits, respectivamente;

realizar (53) una correspondencia de tasas para cada secuencia de bits codificada en 32 bits respectivamente para

establecer una primera secuencia de bits codificada en 32 bits a una secuencia de bits codificada en bits

por intermedio de una correspondencia de tasa y para establecer una segunda secuencia de bits codificada en 32

bits a una secuencia de bits codificada en 4@~l/2b*(L bits por intermedio de una correspondencia de tasa, en donde Qm es un orden de modulación correspondiente a la UCI a transmitir y \ 1 se refiere a un redondeo al valor superior; y

efectuar un mapeado (54) de las dos partes de la secuencia de bits codificadas que han sufrido una correspondencia de tasa en un Canal Compartido de Enlace Ascendente Físico, PUSCH y transmitir las dos partes de la secuencia de bits codificadas a una estación base;

estando dicho método caracterizado por cuanto que:

el establecimiento de la primera secuencia de bits codificada en 32 bits a una secuencia de bits codificada en [/21*, bits por intermedio de una correspondencia de tasa comprende:

si el valor de í*/2l*O es menor que o igual a 32, seleccionar los primeros [/2l*O de bits codificada en 32 bits;

bits en la primera secuencia

si el valor de í*/2l*O es mayor que 32, según 4 -,1....realizar la correspondencia

de tasa para establecer la primera secuencia de bits codificada en 32 bits a una secuencia de bits codificada en

f/2l*O bits en donde q es una salida de secuencia de bits codificada después de que la primera secuencia de bits codificada en 32 bits se establezca a una secuencia de bits codificada en [Wa, mediante una

O-l

b, - 51 ( x M. ) mod 2 / - n i 31

correspondencia de tasa, siendo Í3 J...... , la primera secuencia de bits codificada en 32

bits, On es un bits en la secuencia de bits de información correspondiente a la primera secuencia de bits codificada en 32 bits, Mjn es una secuencia básica de código de RM (32, O) y O' es el número de bits de la secuencia de bits de información correspondiente a la primera secuencia de bits codificada en 32 bits y

el establecimiento de la segunda secuencia de bits codificada en 32 bits a una secuencia de bits codificada en (~f/2l)xQ1

bits por intermedio de la correspondencia de tasa comprende:

si el valor de (Q es menor que o igual a 32, seleccionar los primeros /2])*O b¡ts en |a segunda

secuencia de bits codificada en 32 bits;

si el valor de (~Í/2l)xO es mayor que 32, según í,1,...,((Q-[Q /2_|)xQni 1)| realizar la

correspondencia de tasa para establecer la segunda secuencia de bits codificada en 32 bits a una secuencia de bits

codificada en (Q bits en donde q. es una salida de secuencia de bits codificada después de que la

segunda secuencia de bits codificada en 32 bits se establezca a una secuencia de bits codificada en <4/2l)x&

«.........

bits por intermedio de la correspondencia de tasa, siendo > > la segunda

secuencia de bits codificada en 32 bits, On es un bit en la secuencia de bits de información correspondiente a la segunda secuencia de bits codificada entre 32 bits, Mjn es una secuencia básica de código de RM (32, O) y O' es el

número de bits de la secuencia de bits de información correspondiente a la segunda secuencia de bits codificada en 32 bits.

2. El método según la reivindicación 1, caracterizado por cuanto que

el mapeado de correspondencia de las dos partes de secuencias de bits codificadas que han sufrido la correspondencia de tasa en el canal PUSCH y la transmisión de las dos partes de la secuencia de bits codificada a la estación base comprenden:

la concatenación de las dos partes de secuencia de bits codificada que han sufrido una correspondencia de tasa para formar una nueva secuencia de bits, el mapeado de la nueva secuencia de bits en el canal PUSCH y la transmisión de la nueva secuencia de bits a la estación base o

seleccionar alternativamente 4Qm bits codificados en una de las dos partes de la secuencia de bits codificada que han sufrido una correspondencia de tasa y 4Qm bits codificados en la otra parte de secuencia de bits codificada que han sufrido una correspondencia de tasa para formar una nueva secuencia de bits, el mapeado de la nueva secuencia de bits a través del canal PUSCH y la transmisión de la nueva secuencia de bits a la estación base o

seleccionar alternativamente Qm bits codificados en una de las dos partes de las secuencias de bits codificadas que han sufrido una correspondencia de tasa y Qm bits codificados en la otra parte de las secuencias de bits codificadas que han sufrido una correspondencia de tasa; después de que se hayan seleccionado los 4Qm bits codificados, conmutar el orden de selección alternativa de las dos partes de las secuencias de bits codificadas que han sufrido una correspondencia de tasa, proseguir seleccionando los bits codificados alternativamente para formar una nueva secuencia de bits, efectuar el mapeado de la nueva secuencia de bits en el canal PUSCH y transmitir la nueva secuencia de bits a la estación base.

3. El método según cualquiera de las reivindicaciones 1 a 2 caracterizado por cuanto que:

realizar una correspondencia de tasa para cada secuencia de bits codificada en 32 bits, respectivamente, comprende la etapa siguiente:

realizar una correspondencia de tasa para cada secuencia de bits codificada en 32 bits, respectivamente, mediante una repetición circular.

4. Un método para la recepción de una Información de Control en Enlace Ascendente, que comprende:

recibir (61) la Información de Control en Enlace Ascendente enviada por un terminal y calcular el número Q' de símbolos de modulación ocupados por la Información de Control en Enlace Ascendente;

determinar (62) las secuencias de bits de información de control candidatas según el número de bits de la Información de Control en Enlace Ascendente;

dividir (43) cada secuencia de bits de información de control candidata en dos partes;

utilizar un código de Reed Muller RM (32, O) para codificar cada parte de cada secuencia de bits de información de control candidata para obtener una secuencia de bits codificada en 32 bits, respectivamente,

realizar la correspondencia de tasa para cada secuencia de bits codificada en 32 bits para establecer una primera secuencia de bits codificada en 32 bits a una secuencia de bits codificada en [/2|x&

bits por intermedio de la

correspondencia de tasa y establecer una segunda secuencia de bits codificada en 32 bits a una secuencia de bits codificada en (~[/2l)xO bits por intermedio de la correspondencia de tasa, en donde Qm es un orden de

modulación correspondiente a la Información de Control en Enlace Ascendente y \ 1 se refiere al redondeo al valor superior y

detectar (63) la Información de Control en Enlace Ascendente utilizando las dos partes de secuencias de bits codificadas que corresponden a cada secuencia de bits de información de control candidata y que han sufrido la correspondencia de tasa, estando dicho método caracterizado por:

el establecimiento de la primera secuencia de bits codificada en 32 bits a una secuencia de bits codificada en [/2l*O bjts pr ¡ntermedio de la correspondencia de tasa comprende:

si el valor de [/21*. es menor que o igual a 32, seleccionar los primeros [/21*, bits en la primera secuencia

de bits codificada en 32 bits y

si el valor de \Q^xQn es mayor que 32, según *-,1...,([Q 1), rea|¡zar |a correspondencia de

tasa para establecer la primera secuencia de bits codificada en 32 bits a una secuencia de bits codificada en

\Q/2\xQ bitS en donde q es una salida de secuencia de bits codificada después de que la primera secuencia de

bits codificada en 32 bits se establezca para una secuencia de bits codificada en \Q^xQn bits por intermedio de la

bj = £ (O-* 2 j = ,1,..., 31

correspondencia de tasa, siendo »=« la primera secuencia de bits codificada en 32

bits, On es un bit en la secuencia de bits de información correspondiente a la primera secuencia de bits codificada en 32 bits, M es una secuencia básica de código de RM (32, O) y O' es el número de bits de la secuencia de bits de información correspondiente a la primera secuencia de bits codificada en 32 bits y

el establecimiento de la segunda secuencia de bits codificada en 32 bits a una secuencia de bits codificada en (Í?~íb¡ts por intermedio de la correspondencia de tasa comprende:

si el valor de ^3 \Q^xQn es menor que o igual a 32, seleccionar los primeros (2 Í2^21bits en la segunda secuencia de bits codificada en 32 bits y

{ft __ , *7/ ~^(ímod32) i ,1,...;{(Qr [Or/2~hx 1),

si el valor de (2H2'2DX2, es mayor que 32, según > v realizar la

correspondencia de tasa para establecer la segunda secuencia de bits codificada en 32 bits a una secuencia de bits codificada en bits en donde q es una salida de secuencia de bits codificada después de que la

segunda secuencia de bits codificada en 32 bits se establezca a una secuencia de bits codificada en ((2~\8^XQ«

á;=E(O, x M, )raod 2 j = ,1....31

bits por intermedio de la correspondencia de tasa, siendo «» la segunda secuencia

de bits codificada en 32 bits, O es un bit en la secuencia de bits de información correspondiente a la segunda

secuencia de bits codificada en 32 bits, M es una secuencia básica de código de RM (32, O) y O'es el número de bits de la secuencia de bits de información correspondiente a la segunda secuencia de bits codificada en 32 bits.

5. El método según la reivindicación 4, caracterizado por cuanto que:

la detección de la Información de Control en Enlace Ascendente utilizando las dos partes de las secuencias de bits codificadas que corresponden a cada secuencia de bits de información de control candidata y que han sufrido una correspondencia de tasa comprende las etapas siguientes:

la concatenación de las dos partes de las secuencias de bits codificadas que han sufrido una correspondencia de tasa para formar una nueva secuencia de bits y utilizar la nueva secuencia de bits para detectar la Información de Control en Enlace Ascendente o

seleccionar alternativamente 4Qm bits codificados en una de las dos partes de la secuencia de bits codificada que han sufrido una correspondencia de tasa y 4Qm bits codificados en la otra parte de secuencias de bits codificadas que han sufrido una correspondencia de tasa para formar una nueva secuencia de bits y utilizar la nueva secuencia de bits para detectar la UCI o

seleccionar alternativamente Qm bits codificados en una de las dos partes de las secuencias de bits codificadas que han sufrido una correspondencia de tasa y Qm bits codificados en la otra parte de secuencias de bits codificadas que han sufrido una correspondencia de tasa; después de que se han seleccionado 4Qm bits codificados, conmutar el orden de selección alternativa de las dos partes de las secuencias de bits codificadas que han sufrido una correspondencia de tasa, proseguir seleccionando los bits codificados alternativamente para formar una nueva secuencia de bits y utilizar la nueva secuencia de bits para detectar la Información de Control en Enlace Ascendente.

6. Un terminal que comprende:

un módulo de cálculo (71), configurado para calcular el número Q' de símbolos de modulación ocupados por la Información de Control en Enlace Ascendente, UCI a transmitir, y para obtener un orden de modulación Qm correspondiente a la UCI a transmitir;

un primer módulo de división (72), configurado para dividir una secuencia de bits de información de la UCI a

transmitir en el módulo de cálculo en dos partes;

un primer módulo de codificación (73), configurado para utilizar un código de Reed Muller (RM) (32, O) para codificar cada parte de la secuencia de bits de información de la UCI a transmitir para obtener una secuencia de bits codificada en 32 bits respectivamente y realizar la correspondencia de tasa para cada secuencia de bits codificada en 32 bits para establecer una primera secuencia de bits codificada en 32 bits a una secuencia de bits codificada en

en Mxa,

bits por intermedio de la correspondencia de tasa y para establecer una segunda secuencia de bits

codificada en 32 bits a una secuencia de bits codificada en (alai 2V& bits por intermedio de la correspondencia

de tasa, en donde Qm es el orden de modulación correspondiente a la UCI a transmitir y I" 1 se refiere al redondeo al valor superior y

un módulo de transmisión (74), configurado para el mapeado de las dos partes de secuencias de bits codificadas que han sufrido una correspondencia de tasa en un canal compartido de enlace ascendente físico, PUSCH, y para transmitir las dos partes de las secuencias de bits codificadas a una estación base;

en donde el primer módulo de codificación (73) comprende:

una primera unidad de codificación, configurada para utilizar un código de Reed Muller (RM) (32, O) para codificar cada parte de secuencia de bits de información de la UCI a transmitir, que está dividida por el primer módulo de división, para obtener una secuencia de bits codificada en 32 bits, respectivamente;

una primera unidad de obtención, configurada para obtener un bit On de la secuencia de bits de información correspondiente a la primera secuencia de bits codificada en 32 bits obtenida por la primera unidad de codificación, una secuencia básica Mj¡n del código de RM (32, O) y O' siendo el número de bits de la secuencia de bits de información correspondiente a la primera secuencia de bits codificada en 32 bits, estando dicho terminal caracterizado por cuanto que

una primera unidad de correspondencia de tasa, configurada para: seleccionar los primeros bits en la

primera secuencia de bits codificada en 32 bits obtenida por la primera unidad de codificación si el valor de

[G/2|xa

es menor que o igual a 32, o para realizar la correspondencia de tasa para la primera secuencia de bits

codificada en 32 bits para establecer la secuencia para una secuencia de bits codificada en

re'2|*Q, bits según

<rrno432)

< = aj,...,<re'/2lx&-n

si el valor de

fQrfxQ,

es mayor que 32, en donde q. es una salida de

secuencia de bits codificada después de que la primera secuencia de bits codificada en 32 bits se establezca a una secuencia de bits codificada en fe'*[xO. bits por intermedio de una correspondencia de tasa, siendo

bj = xMJ¡Jmod2) j - ,1,...,31;

»= ' la primera secuencia de bits codificada en 32 bits y On, M¡n y O son

parámetros obtenidos por la primera unidad de obtención;

una segunda unidad de obtención, configurada para obtener el bit On de la secuencia de bits de información correspondiente a la segunda secuencia de bits codificada en 32 bits obtenida por la primera unidad de codificación, una secuencia básica Mj¡n del código de RM (32, O) y siendo O el número de bits de la secuencia de bits de información correspondiente a la segunda secuencia de bits codificada en 32 bits y

una segunda unidad de correspondencia de tasa, configurada para: seleccionar los primeros © b¡ts en \a

segunda secuencia de bits codificada en 32 bits obtenida por la primera unidad de codificación si el valor de

es menor que o igual a 32, o realizar la correspondencia de tasa para la segunda secuencia de bits codificada en 32 bits para establecer la secuencia a una secuencia de bits codificada en (SAS^ffxQ, b¡ts según

?¡=Wb) ; = íl,...,«2'4e'/2l)*eB-l) trinan

> , si el valor de 'Q l/2Dx£íi es mayor que 32, en donde q. es una salida

de secuencia de bits codificada después de que la segunda secuencia de bits codificada en 32 bits se establezca a una secuencia de bits codificada en <SAQt 2l)x& bits por intermedio de la correspondencia de tasa, siendo *,=2(. mod2? j = ,1,...,31,

»=o la segunda secuencia de bits codificada en 32 bits y On, M.n y O' son

parámetros obtenidos por la segunda unidad de obtención.

7. El terminal según la reivindicación 6, caracterizado por cuanto que

el módulo de transmisión (74) comprende al menos una de las unidades de transmisión siguientes:

una primera unidad de transmisión, configurada para la concatenación de las dos partes de secuencias de bits codificadas que han sufrido la correspondencia de tasa para formar una nueva secuencia de bits, para el mapeado de la nueva secuencia de bits en el canal PUSCH y para transmitir la nueva secuencia de bits a la estación base;

una segunda unidad de transmisión, configurada para seleccionar alternativamente 4Qm bits codificados en una de las dos partes de secuencias de bits codificadas que han sufrido una correspondencia de tasa y 4Qm bits codificados en la otra parte de secuencias de bits codificadas que han sufrido una correspondencia de tasa para formar una nueva secuencia de bits, para el mapeado de la nueva secuencia de bits en el canal PUSCH y para transmitir la nueva secuencia de bits a la estación base y

una tercera unidad de transmisión, configurada para seleccionar alternativamente Qm bits codificados en una de las dos partes de secuencias de bits codificadas que han sufrido una correspondencia de tasa y Qm bits codificados en la otra parte de secuencias de bits codificadas que han sufrido una correspondencia de tasa y después de que se seleccionen los 4Qm bits codificados, conmutar el orden de selección alternativa de las dos partes de secuencias de bits codificadas que han sufrido una correspondencia de tasa, prosiguiendo la selección alternativa de los bits codificados para formar una nueva secuencia de bits, para el mapeado de la nueva secuencia de bits en el canal PUSCH y para su transmisión a la estación base.

8. Una estación base, que comprende:

un módulo de recepción (81), configurado para recibir Información de Control en Enlace Ascendente enviada por un terminal, para calcular el número Q' de símbolos de modulación ocupados por la Información de Control en Enlace Ascendente y para obtener el orden de modulación Qm correspondiente a la Información de Control en Enlace Ascendente;

un módulo de determinación (82), configurado para determinar secuencias de bits de información de control candidatas según el número de bits de la Información de Control en Enlace Ascendente recibida por el módulo de

recepción;

un segundo módulo de división (83), configurado para dividir cada secuencia de bits de información de control candidata determinada por el módulo de determinación en dos partes,

un segundo módulo de codificación (84), configurado para utilizar un código de Reed Muller (RM) (32, O) para codificar cada parte de cada secuencia de bit de información de control candidata para obtener una secuencia de bits codificada en 32 bits respectivamente y para realizar una correspondencia de tasa para cada secuencia de bits codificada en 32 bits para establecer una primera secuencia de bits codificada en 32 bits a una secuencia de bits

codificada en fe'2l*a bits por intermedio de una correspondencia de tasa y para establecer una segunda

secuencia de bits codificada en 32 bits a una secuencia de bits codificada en <£? Íí?/2l)xfi. bits por intermedio de una correspondencia de tasa, en donde Qm es el orden de modulación correspondiente a la Información de Control

en Enlace Ascendente y \ 1 se refiere al redondeo al valor superior y

un módulo de detección (85), configurado para detectar la Información de Control en Enlace Ascendente utilizando las dos partes de secuencias de bits codificadas que corresponden a cada secuencia de bits de información de control candidata y que han sufrido una correspondencia de tasa;

en donde el segundo módulo de codificación (84) comprende:

una segunda unidad de codificación, configurada para utilizar un código de Reed Muller (RM) (32, O) para codificar cada parte de cada secuencia de bits de información de control candidata para obtener una secuencia de bits codificada en 32 bits respectivamente;

una tercera unidad de obtención, configurada para obtener un bit On de la secuencia de bits de información correspondiente a la primera secuencia de bits codificada en 32 bits obtenida por la segunda unidad de codificación, una secuencia básica Mjn del código de RM (32, O) y O' siendo el número de bits de la secuencia de bits de información correspondiente a la primera secuencia de bits codificada en 32 bits;

estando dicha estación base caracterizada por cuanto que

una tercera unidad de correspondencia de tasa, configurada para: seleccionar los primeros

\Q!Í\xQ, bits en la

primera secuencia de bits codificada en 32 bit si el valor de \Q,A*, es menor que o igual a 32, o para realizar una correspondencia de tasa para la primera secuencia de bits codificada en 32 bits para establecer la secuencia a una

secuencia de bits codificada en bits según 1 «CÍQ^1XQ« 9, s¡ e| va|or de

\Q/2\xQ es mayr qUe 32, en donde q. es una salida de secuencia de bits codificada después de que la primera

secuencia de bits codificada en 32 bits se establezca para una secuencia de bits codificada en I Q^VQm bits

b; = I ( x A/^Jniod 2 j = ,1,...,31

mediante una correspondencia de tasa, siendo »=° la primera secuencia de bits

codificada en 32 bits y On, MJn y O'son parámetros obtenidos por la tercera unidad de obtención;

una cuarta unidad de obtención, configurada para obtener un bit On de la secuencia de bits de información correspondiente a la segunda secuencia de bits codificada en 32 bits obtenida por la segunda unidad de codificación, una secuencia básica M del código de RM (32, O) y O' siendo el número de bits de la secuencia de bits de información correspondiente a la segunda secuencia de bits codificada en 32 bits y

una cuarta unidad de correspondencia de tasa, configurada para: seleccionar los primeros bits en la

segunda secuencia de bits codificada en 32 bits si el valor de (Gffe^xQ, es menor que o igual a 32, o para realizar una correspondencia de tasa para la segunda secuencia de bits codificada en 32 bits para establecer la

secuencia a una secuencia de bits codificada en (qAqiiVü, bits según

<7, 1 - ,t,...,((£) f/2"t)x2B 9 > s¡ e| va|or de >*& es mayor que 32, en donde q. es una salida

de secuencia de bits codificada después de que la segunda secuencia de bits codificada en 32 bits se establezca para una secuencia de bits codificada en ©fe^ljxQ, b¡ts por ¡ntermedio de una correspondencia de tasa, siendo

b. = S (°»x M:.)mod 2> j = ,1, - -,31.

' la segunda secuencia de bits codificada en 32 bits y On Mjn y O' son parámetros obtenidos por la cuarta unidad de obtención.

9. La estación base según la reivindicación 8, caracterizada por cuanto que

el módulo de detección (85) comprende al menos una de las unidades de detección siguientes:

una primera unidad de detección, configurada para la concatenación de las dos partes de secuencias de bits codificadas que han sufrido una correspondencia de tasa para formar una nueva secuencia de bits y para utilizar la nueva secuencia de bits para detectar la Información de Control en Enlace Ascendente;

una segunda unidad de detección, configurada para seleccionar alternativamente 4Qm bits codificados en una de las dos partes de secuencias de bits codificadas que han sufrido una correspondencia de tasa y 4Qm bits codificados en la otra parte de secuencias de bits codificadas que han sufrido una correspondencia de tasa para formar una nueva secuencia de bits y para utilizar la nueva secuencia de bits para detectar la Información de Control en Enlace Ascendente y

una tercera unidad de detección, configurada para seleccionar alternativamente Qm bits codificados en una de las dos partes de secuencias de bits codificadas que han sufrido una correspondencia de tasa y Qm bits codificados en la otra parte de secuencias de bits codificadas que han sufrido una correspondencia de tasa y, después de que se seleccionen 4Qm bits codificados, conmutar el orden de selección alternativa de las dos partes de secuencias de bits codificadas que han sufrido una correspondencia de tasa, para proseguir la selección alternativa de los bits codificados para formar una nueva secuencia de bits y para utilizar la nueva secuencia de bits para detectar la Información de Control en Enlace Ascendente.

Patentes similares o relacionadas:

Aparato de comunicación inalámbrica y procedimiento de generación de señales de referencia, del 29 de Julio de 2020, de Sun Patent Trust: Un aparato de comunicación para una estación base que comprende: un transmisor, el cual, en operación, transmite, a un terminal, información […]

Procedimiento y aparato para inserción de índice de bloque de código en un sistema celular de comunicación inalámbrica, del 29 de Julio de 2020, de SAMSUNG ELECTRONICS CO., LTD.: Un procedimiento de un terminal en un sistema de comunicación inalámbrica, comprendiendo el procedimiento: recibir, de una estación base, un bloque de información maestra, […]

Detección y comprobación de error de señalización de retroalimentación en sistemas de comunicación inalámbrica de MIMO, del 15 de Julio de 2020, de INTERDIGITAL TECHNOLOGY CORPORATION: Un método implementado en una unidad de transmisión recepción inalámbrica, WTRU, caracterizado por que el método comprende: proporcionar una pluralidad […]

Repetición de transmisiones de señales en sistemas de comunicación, del 15 de Julio de 2020, de SAMSUNG ELECTRONICS CO., LTD.: Un procedimiento para que un equipo de usuario, UE, transmita una señal de acuse de recibo en un sistema de comunicación, comprendiendo el procedimiento: transmitir la señal […]

Método y dispositivo de codificación, del 15 de Julio de 2020, de HUAWEI TECHNOLOGIES CO., LTD.: Un método de codificación, que comprende: realizar (S101), mediante un extremo de transmisión basado en un polinomio de verificación de redundancia cíclica, […]

Información de control en un sistema de comunicación inalámbrica, del 15 de Julio de 2020, de QUALCOMM INCORPORATED: Un procedimiento para enviar datos de tráfico e información de control en un sistema de comunicación inalámbrica, que comprende: realizar conformación de haces […]

Método, aparato y sistema para retroalimentar la decodificación de detención temprana, del 1 de Julio de 2020, de ZTE CORPORATION: Un método para retroalimentar un resultado de decodificación de la decodificación de detención temprana, caracterizado porque comprende: en un intervalo de tiempo […]

Tramas Wi-Fi que incluyen extensiones de trama, del 1 de Julio de 2020, de QUALCOMM INCORPORATED: Un procedimiento de comunicación inalámbrica realizado por un aparato, que comprende: generar una trama para activar la transmisión […]