Dispositivo de extracción de reloj con retroalimentación digital de fase sin ajuste externo.

Dispositivo de extracción de reloj a partir de una señal en serie en banda de base,

denominada señal recibida, representativa de unos datos digitales y codificada con una señal de reloj que presenta una frecuencia de reloj bits fsr, que comprende:

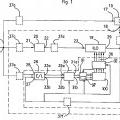

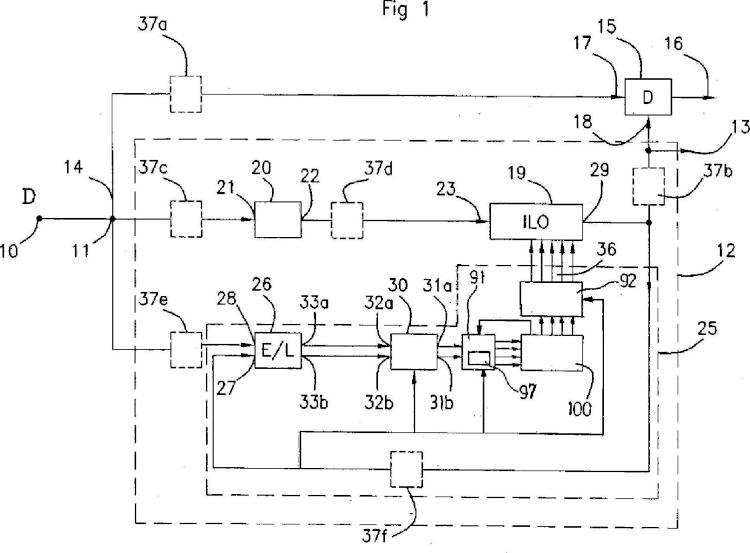

- un circuito (19) que recibe una señal procedente de la señal recibida y acompasada a la frecuencia de reloj bits fsr, y que emite, en al menos una salida de reloj (29), una señal de reloj, denominada señal de reloj de recepción, al menos sustancialmente sincronizada y en fase con la frecuencia de reloj bits fsr de la señal recibida;

- un bucle de retroalimentación de fase (25) que comprende:

- una primera entrada (27) conectada a una salida de reloj (29) del circuito (19) que emite una señal de reloj de recepción;

- una segunda entrada (28) alimentada con una señal procedente de la señal recibida;

- un detector (26) digital de fase que comprende un detector de adelanto-retardo conectado a la primera y a la segunda entradas (27, 28) y adaptado para emitir, en al menos una salida (33a, 33b), al menos una señal digital, denominada señal de estados de fase, representativa de un desplazamiento de fase entre la señal de reloj de recepción y la señal recibida, y del sentido de este desplazamiento;

- una salida (36) que emite una señal, denominada señal de control, conectada a una entrada (24), denominada entrada de control, del circuito (19) que emite una señal de reloj de recepción, adaptada para que el valor de la frecuencia de la señal de reloj de recepción dependa del valor de la señal de control recibida en esta entrada (24) de control;

- un circuito, denominado circuito contador (30, 35, 55, 91, 92, 116, 117), que presenta una entrada conectada a dicha salida (33a, 33b) del detector (26) digital de fase, estando dicho circuito contador adaptado para realizar al menos un filtrado por conteo/desconteo digital en las variaciones de los valores relativos de la señal digital emitidos a lo largo del tiempo por el detector (26) de fase, y para emitir una señal de control en forma digital cuyo valor depende del resultado de este (estos) filtrado(s), estando este valor de la señal de control adaptado para imponer un valor de la frecuencia de la señal de reloj de recepción igual a un valor así filtrado de la frecuencia de reloj bits fsr de la señal de reloj de recepción,

caracterizado por que:

- el circuito (19) que emite una señal de reloj de recepción es un oscilador (19) bloqueado en inyección con control digital, que comprende una entrada (24) digital de control, adaptada para poder recibir la señal de control emitida por el bucle de retroalimentación de fase (25) en forma digital, y para que el valor de la frecuencia propia fos del oscilador (19) dependa del valor de la señal de control recibida en esta entrada (24) de control;

- el circuito contador (91, 92, 116, 117) comprende dos etapas, que son:

- una primera etapa (91, 116) conectada al detector (26) digital de fase y que cuenta/descuenta, a partir de la señal de estados de fase, las variaciones de estados de fase a partir de un valor medio predeterminado, y que emite una señal digital paralela, denominada señal menos significativa, cuyo valor es representativo de una acumulación de variaciones de estados de fase, en un sentido y/o en el otro, a partir del valor medio;

- una segunda etapa (92, 117) conectada a la primera etapa de tal modo que cuenta/descuenta los rebasamientos de la acumulación de variaciones de estados de fase en el mismo sentido más allá de cada valor extremo de la señal menos significativa, y adaptada para suministrar en una salida digital paralela dicha señal de control cuyo valor corresponde a la acumulación de los rebasamientos en un sentido y/o en el otro.

Tipo: Patente Internacional (Tratado de Cooperación de Patentes). Resumen de patente/invención. Número de Solicitud: PCT/FR2008/000480.

Solicitante: CENTRE NATIONAL D'ETUDES SPATIALES (C.N.E.S.).

Nacionalidad solicitante: Francia.

Dirección: 2, PLACE MAURICE QUENTIN 75039 PARIS CEDEX 01 FRANCIA.

Inventor/es: PIGNOL, MICHEL, NEVEU, CLAUDE, DEVAL,YANN, BEGUERET,JEAN-BAPTISTE, MAZOUFFRE,OLIVIER.

Fecha de Publicación: .

Clasificación Internacional de Patentes:

- H04L25/02 ELECTRICIDAD. › H04 TECNICA DE LAS COMUNICACIONES ELECTRICAS. › H04L TRANSMISION DE INFORMACION DIGITAL, p. ej. COMUNICACION TELEGRAFICA (disposiciones comunes a las comunicaciones telegráficas y telefónicas H04M). › H04L 25/00 Sistemas de banda base. › Detalles.

PDF original: ES-2507077_T3.pdf

Fragmento de la descripción:

La invención se refiere a un dispositivo de extracción de reloj, y de manera más particular a un dispositivo de extracción de reloj y de datos digitales, a partir de una señal en serie en banda de base, denominada señal recibida, representativa de datos digitales, y codificada con una señal de reloj que presenta un frecuencia de reloj bits fsr que corresponde al menos sustancialmente a una frecuencia nominal fn.

En numerosas aplicaciones, y en particular en el campo de las muy altas frecuencias (frecuencias nominales fn superiores a 5 MHz, que pueden ser superiores a 1 GHz, que pueden incluso llegar actualmente hasta 4 GHz e incluso superar muy ampliamente estos valores en el futuro) que corresponden a muy altas velocidades (superiores a 5 Mbits/s, que pueden ser superiores a 1 Gbits/s, y que pueden llegar incluso a 4 Gbits/s para los estándares SONET OC-768 y SDH STM-256 y que pueden superar muy ampliamente sus valores en el futuro), se transmite en un canal de transmisión (cuya tecnología de realización puede ser cualquiera: eléctrica, óptica, radiofrecuencia...) de una conexión en serie en banda de base una señal que incorpora unos datos digitales mezclados con una señal de reloj, de tal modo que se evita tener que transmitir estas dos informaciones en dos canales diferentes. Esto permite evitar cualquier emparejamiento delicado de la longitud de los trayectos de las señales. Con dichas señales, al nivel del receptor, es necesario extraer de la señal recibida, de naturaleza analógica, por una parte los valores de los datos digitales y, por otra parte, la señal de reloj correspondiente a estos datos. Para obtener los valores de los datos, se muestrea la señal recibida a partir de la señal de reloj previamente extraída de los datos.

La solución más habitual para realizar dicho dispositivo de extracción de reloj y de datos consiste en utilizar unos circuitos que comprenden al menos un bucle de bloqueo de fase, denominado PLL, que comprende principalmente, en la salida de un circuito que genera impulsos que corresponden a los flancos ascendentes y descendentes de la señal recibida, enviando un comparador de fase una señal de consigna a un oscilador controlado en tensión, denominado VCO, a través de un filtro de bucle. El VCO suministra una señal de reloj interno a un biestable de decisión, que constituye un circuito de muestreo que extrae los datos de la señal recibida. Estos circuitos PLL tradicionales, que utilizan unos osciladores de relajación o unos osciladores de red LC, unos comparadores fase/frecuencia y unos divisores digitales de alta frecuencia, presentan diferentes inconvenientes. Son incompatibles con las conexiones de muy alta velocidad; precisan una referencia de frecuencia externa, precisan una sincronización en el arranque mediante un preámbulo de datos que deben necesariamente estar presentes en la señal recibida, lo que no es aceptable en algunas aplicaciones; presentan una gran complejidad de optimización de funcionamiento y de realización, numerosos parámetros ¡nterdependlentes y contradictorios que se deben tener en cuenta, en particular en lo que se refiere al circuito comparador fase/frecuencia; tienen un consumo energético muy alto; su realización analógica es muy dependiente de la tecnología de fabricación de los componentes semiconductores que se utilizan... Por consiguiente, la realización de un circuito PLL para realizar una funcionalidad de extracción de reloj precisa la Intervención de especialistas de los circuitos analógicos con una gran experiencia y una gran técnica, y, por otra parte, precisa unos tiempos de desarrollo Importantes, hay que renovarlos regularmente cada vez que evoluciona la tecnología, lo que, desde el punto de vista de las exigencias actuales de utilización a escala Industrial, no es admisible.

Otra solución conocida para realizar la extracción de reloj se basa en el uso de un bucle de bloqueo de retardo, denominado DLL. Sin embargo, estos circuitos precisan un código específico en lo que se refiere a la señal recibida, en particular con un bit de arranque y un bit de parada para formar una transición de referencia en cada palabra (lo que reduce la frecuencia de transmisión máxima accesible para los datos, tradlclonalmente del 33 % con unos datos útiles de 8 bits y un código como 8B/12B). Además, los datos recuperados presentan una deriva de fase ("jitter") relativamente importante, que puede conducir a un Importante porcentaje de errores de bits. Igualmente, dicho circuito DLL es muy sensible a los ruidos en la señal recibida. Por último, esta técnica ¡mplementada con unos componentes digitales es difícilmente compatible con unas velocidades de transmisión extremadamente elevadas.

El documento FR 2838265 ha propuesto una solución que consiste en utilizar un oscilador de Inyección, es decir un oscilador bloqueado en inyección en la frecuencia de flancos de la señal recibida en un circuito de bucle abierto. Para ello, el oscilador de inyección es un oscilador de resistencia negativa que utiliza un par acoplado de transistores MOS, y recibe una señal de Impulsos de sincronización acompasada a la frecuencia de reloj bits fsr de la señal recibida, emitiéndose esta señal de Impulso por un generador de Impulsos de sincronización. Este oscilador bloqueado en inyección que presenta una frecuencia de oscilaciones libres fos, tiene la facultad de bloquearse en la señal de impulsos si la frecuencia de esta última está en su Intervalo de funcionamiento, denominado intervalo de captura. Este proporciona entonces una señal de reloj cuya frecuencia corresponde exactamente a la frecuencia de reloj bits fsr.

Sin embargo, el problema que se plantea entonces es garantizar también la sincronización en fase de la señal de reloj que proporciona el oscilador, con respecto a la señal recibida. A este respecto, se sabe que el desplazamiento de fase que introduce el oscilador es proporcional a la diferencia entre la frecuencia de la señal en la entrada del oscilador y la frecuencia propia fos de esta última. Como consecuencia, se puede pensar en ajustar el valor de la frecuencia propia del oscilador en función de la frecuencia de reloj bits fsr de la señal recibida al diseñar el circuito.

Pero esta solución sigue siendo imperfecta en la medida en que justamente el valor de esta frecuencia de reloj bits fsr no se conoce con precisión (lo que constituye el problema técnico inicial principal que precisa la presencia de un circuito de extracción de reloj en el receptor). Además, precisaría en cualquier caso un ajuste del circuito para cada aplicación. Aunque dicho ajuste es admisible en el contexto de un prototipo de laboratorio, no es aceptable en la mayoría de las aplicaciones industriales de dicho circuito.

El documento FR 2838265 ha propuesto resolver este problema de desplazamiento de fase previendo una lógica de decisión para seleccionar un valor entre diferentes valores suministrados por una multitud de biestables de muestreo desplazados de acuerdo con unos tiempos de desplazamiento distintos con respecto a los impulsos de la señal de reloj de recepción. Resulta que, en la práctica, esta solución no es realmente eficaz en todas las situaciones.

También el documento US 692475 describe un circuito PLL que comprende un detector digital de fase, una bomba de carga y un filtro de bucle que controla un oscilador controlado en tensión, recibiendo este último la señal de datos en la entrada a través de un duplicador de frecuencia. Además de que no se indica la realización práctica del detector digital de fase, este circuito presenta el inconveniente de no poder realizarse completamente de forma digital, puesto que la bomba de carga y el filtro de bucle son componentes de tipo analógico. Por consiguiente, la realización de un circuito de acuerdo con este documento es estrechamente dependiente en la práctica de la tecnología del semiconductor que se utiliza y no se puede adaptar simple y rápidamente a otra tecnología de semiconductor, sin precisar previamente un nuevo diseño del circuito. Además, este circuito al presentar un reducido intervalo de frecuencias admisibles en la entrada y al no adaptarse automáticamente a la señal recibida, precisa unos ajustes manuales externos de la frecuencia libre del oscilador y de la diferencia de retardos de propagación entre las diferentes líneas, en particular la que permite extraer los datos y la que permite extraer el reloj. Por lo tanto, el circuito que se describe en este documento no puede ser objeto de una utilización a escala industrial en las aplicaciones en las que el periodo de desarrollo se debe minimizar y/o en aquellas en las que es preciso poder migrar con frecuencia de una tecnología de semiconductor a otra y/o en las que la frecuencia de la señal recibida... [Seguir leyendo]

Reivindicaciones:

1. Dispositivo de extracción de reloj a partir de una señal en serie en banda de base, denominada señal recibida, representativa de unos datos digitales y codificada con una señal de reloj que presenta una frecuencia de reloj bits fsr, que comprende:

- un circuito (19) que recibe una señal procedente de la señal recibida y acompasada a la frecuencia de reloj bits fsr, y que emite, en al menos una salida de reloj (29), una señal de reloj, denominada señal de reloj de recepción, al menos sustancialmente sincronizada y en fase con la frecuencia de reloj bits fsr de la señal

recibida;

- un bucle de retroalimentación de fase (25) que comprende:

- una primera entrada (27) conectada a una salida de reloj (29) del circuito (19) que emite una señal de reloj

de recepción;

- una segunda entrada (28) alimentada con una señal procedente de la señal recibida;

- un detector (26) digital de fase que comprende un detector de adelanto-retardo conectado a la primera y a la segunda entradas (27, 28) y adaptado para emitir, en al menos una salida (33a, 33b), al menos una señal digital, denominada señal de estados de fase, representativa de un desplazamiento de fase entre la señal de reloj de recepción y la señal recibida, y del sentido de este desplazamiento;

- una salida (36) que emite una señal, denominada señal de control, conectada a una entrada (24), denominada entrada de control, del circuito (19) que emite una señal de reloj de recepción, adaptada para que el valor de la frecuencia de la señal de reloj de recepción dependa del valor de la señal de control recibida en esta entrada (24) de control;

- un circuito, denominado circuito contador (3, 35, 55, 91, 92, 116, 117), que presenta una entrada conectada a dicha salida (33a, 33b) del detector (26) digital de fase, estando dicho circuito contador adaptado para realizar al menos un filtrado por conteo/desconteo digital en las variaciones de los valores relativos de la señal digital emitidos a lo largo del tiempo por el detector (26) de fase, y para emitir una señal de control en forma digital cuyo valor depende del resultado de este (estos) filtrado(s), estando este valor de la señal de control adaptado para imponer un valor de la frecuencia de la señal de reloj de recepción igual a un valor asi filtrado de la frecuencia de reloj bits fsr de la señal de reloj de recepción,

caracterizado porque:

- el circuito (19) que emite una señal de reloj de recepción es un oscilador (19) bloqueado en Inyección con control digital, que comprende una entrada (24) digital de control, adaptada para poder recibir la señal de control emitida por el bucle de retroalimentación de fase (25) en forma digital, y para que el valor de la frecuencia propia fos del oscilador (19) dependa del valor de la señal de control recibida en esta entrada (24) de control;

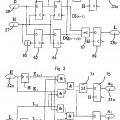

- el circuito contador (91, 92, 116, 117) comprende dos etapas, que son:

- una primera etapa (91, 116) conectada al detector (26) digital de fase y que cuenta/descuenta, a partir de la señal de estados de fase, las variaciones de estados de fase a partir de un valor medio predeterminado, y que emite una señal digital paralela, denominada señal menos significativa, cuyo valor es representativo de una acumulación de variaciones de estados de fase, en un sentido y/o en el otro, a partir del valor medio;

- una segunda etapa (92, 117) conectada a la primera etapa de tal modo que cuenta/descuenta los rebasamientos de la acumulación de variaciones de estados de fase en el mismo sentido más allá de cada valor extremo de la señal menos significativa, y adaptada para suministrar en una salida digital paralela dicha señal de control cuyo valor corresponde a la acumulación de los rebasamientos en un sentido y/o en el otro.

2. Dispositivo de acuerdo con la reivindicación 1, caracterizado porque la primera etapa está adaptada para reiniciar el valor de la señal menos significativa en el valor medio después de cada rebasamiento en un sentido.

3. Dispositivo de acuerdo con una de las reivindicaciones 1 o 2, caracterizado por que la primera etapa (91) comprende un sumador (93) que presenta una salida paralela que emite la señal menos significativa, y por que la segunda etapa (92) comprende un circuito (1) detector de retención de la salida del sumador (93) de la primera etapa (91), y un sumador (94) que recibe la señal de salida de este circuito (1) detector de retención.

4. Dispositivo de acuerdo con una de las reivindicaciones 1 o 2, caracterizado por que la primera etapa (116) comprende un contador/descontador que presenta una salida (113a) superior de retención y una salida (113b) inferior de retención, y por que la segunda etapa (117) comprende un contador/descontador conectado al contador/descontador de la primera etapa (116) para recibir en la entrada los valores de las salidas de retención.

5. Dispositivo de acuerdo con una de las reivindicaciones 1 a 4, caracterizado por que el valor medio se registra en un registro (97) permanente conectado a la primera etapa (91, 116).

6. Dispositivo de acuerdo con una de las reivindicaciones 1 a 5, caracterizado porque la segunda etapa (92, 117) comprende un circuito (17, 18) de entrada limitador de variaciones conectado a la salida digital paralela de la

segunda etapa (92, 117) para recibir la señal emitida en la salida por esta segunda etapa (92, 117), estando este circuito (17, 18) de entrada adaptado para impedir una variación de la señal de control por debajo del valor nulo y por encima del valor máximo de la salida (36) digital paralela de la segunda etapa (92, 117).

7. Dispositivo de acuerdo con una de las reivindicaciones 1 a 6, caracterizado por que el detector (26) de adelanto- retardo está adaptado para emitir en una primera salida (33a) una señal digital (E) representativa de la presencia de un adelanto de fase entre la señal de reloj de recepción y la señal recibida, y en una segunda salida (33b) una señal digital (L) representativa de la presencia de un retardo de fase entre la señal de reloj de recepción y la señal recibida.

8. Dispositivo de acuerdo con una de las reivindicaciones 1 a 7, caracterizado por que el detector (26) de adelanto- retardo está adaptado para muestrear la señal recibida en los flancos ascendentes y descendentes de la señal de reloj de recepción.

9. Dispositivo de acuerdo con una de las reivindicaciones 1 a 8, caracterizado por que el detector (26) de adelanto- retardo está adaptado para realizar un doble muestreo, uno en fase con los flancos de la señal de reloj de recepción, el otro en cuadratura con los flancos de la señal de reloj de recepción de tal modo que determina el estado intermedio de la señal recibida.

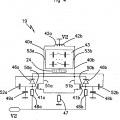

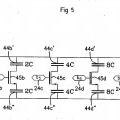

1. Dispositivo de acuerdo con una de las reivindicaciones 1 a 9, caracterizado por que la entrada (24) digital de control del oscilador (19) bloqueado en inyección está conectada a un circuito que comprende una multitud de conmutadores (45a, 45b, 45c, 45d, 45e), estando cada conmutador conectado en serie con al menos un condensador integrado dentro del circuito del oscilador (19) de tal modo que modifica su propia frecuencia, por que cada bit de la entrada (24) digital de control está conectado a uno de los conmutadores.

11. Dispositivo de acuerdo con la reivindicación 1, caracterizado porque comprende, además, un circuito, denominado generador (2) de impulsos de sincronización, que genera una señal de impulsos de corriente en la frecuencia de flancos de la señal recibida, y adaptado al funcionamiento del oscilador (19) bloqueado en inyección, estando este generador (2) de impulsos de sincronización adaptado para emitir la señal de impulsos de corriente en una salida (22) única conectada únicamente a una entrada (23) de corriente del oscilador (19) bloqueado en inyección.

12. Dispositivo de acuerdo con una de las reivindicaciones 1 a 11, de extracción de reloj y de datos digitales, que comprende, además, un circuito (15) de muestreo de la señal recibida con la señal de reloj de recepción, teniendo este circuito (15) de muestreo una primera entrada, denominada entrada de señal (17), conectada a la entrada de recepción, y una segunda entrada, denominada entrada de reloj (18), conectada a una salida de reloj (29) del oscilador bloqueado en inyección, estando este circuito (15) de muestreo adaptado para emitir en al menos una salida (16) de datos, unos datos digitales transmitidos por la señal recibida,

caracterizado por que comprende al menos un circuito desfasador (37a, 37b, 37c, 37d, 37e, 37f) adaptado para introducir una diferencia de fase constante entre la entrada de señal (17) y la entrada de reloj (18) del circuito (15) de muestreo, estando la diferencia de fase total entre estas dos entradas (17, 18) resultante de cada circuito desfasador adaptada para garantizar una alineación de fase de la señal en la entrada de señal (17) y de la señal en la entrada de reloj (18).

13. Dispositivo de acuerdo con la reivindicación 12, caracterizado por que el circuito (15) de muestreo está formado por un simple biestable D.

14. Dispositivo de acuerdo con una de las reivindicaciones 1 a 13, caracterizado porque está adaptado para poder funcionar con una frecuencia de reloj bits fsr superior a 5 MHz.

Patentes similares o relacionadas:

Ecualización inteligente para un sistema multifásico de tres transmisores, del 29 de Julio de 2020, de QUALCOMM INCORPORATED: Un sistema de tres transmisores para transmitir símbolos multifásicos sucesivos, que comprende:

un codificador configurado para codificar […]

Ecualización inteligente para un sistema multifásico de tres transmisores, del 29 de Julio de 2020, de QUALCOMM INCORPORATED: Un sistema de tres transmisores para transmitir símbolos multifásicos sucesivos, que comprende:

un codificador configurado para codificar […]

Estimación de canal de antenas múltiples de grupo iterativo ordenado disperso, del 22 de Julio de 2020, de Altiostar Networks, Inc: Un método implementado por procesador para proporcionar una respuesta de impulso de canal estimado final, implementable por uno o más procesadores de datos que forman parte […]

Método y dispositivo de transmisión de datos de red de área local inalámbrica, del 15 de Julio de 2020, de HUAWEI TECHNOLOGIES CO., LTD.: Un método de transmisión de información de estimación de canal en un sistema de comunicación, en un extremo de transmisión, que comprende: […]

Procedimiento la lucha antiinterferencias por filtrado espacial o filtrado espacio-temporal en un receptor multicanal, del 24 de Junio de 2020, de THALES: Procedimiento de recepción de una señal y de rechazo de las interferencias en un receptor multicanal , comprendiendo dicho procedimiento las […]

Acuses de recibo retardados para comunicación de baja sobrecarga en una red, del 24 de Junio de 2020, de QUALCOMM INCORPORATED: Un procedimiento para comunicación entre estaciones a través de un medio compartido , comprendiendo el procedimiento: recibir una primera […]

Extremo frontal de transceptor para comunicación mediante líneas eléctricas, del 13 de Mayo de 2020, de Landis+Gyr Technologies, LLC: Circuito de comunicación mediante líneas eléctricas para su uso en un sistema de comunicación mediante líneas eléctricas, comprendiendo el circuito (100; […]

Estación base, equipo de usuario y métodos en los mismos en un sistema de comunicaciones, del 25 de Marzo de 2020, de TELEFONAKTIEBOLAGET LM ERICSSON (PUBL): Un método en un equipo de usuario para transmitir información del estado de canal a una primera estación base , cuyo equipo de usuario está comprendido […]

Estación base, equipo de usuario y métodos en los mismos en un sistema de comunicaciones, del 25 de Marzo de 2020, de TELEFONAKTIEBOLAGET LM ERICSSON (PUBL): Un método en un equipo de usuario para transmitir información del estado de canal a una primera estación base , cuyo equipo de usuario está comprendido […]

Procedimiento de asociación univalente y unívoca entre emisores y receptores de transmisión a partir del canal de propagación, del 25 de Marzo de 2020, de THALES: Procedimiento de asociación univalente y unívoca, antes del establecimiento de un protocolo de comunicación, a partir del canal (AU_CP) de propagación […]