Aparato de codificación de un indicador de combinación de formato de transporte para un sistema de comunicación móvil CDMA.

Un aparato de codificación de Indicador de Combinación de Formato de Transporte TFCI para un sistema de comunicación,

que comprende: un generador de secuencia ortogonal (810), para generar una pluralidad de secuencias biortogonales de base, acorde con una primera parte de bits de información; un generador de secuencia de máscara (820), para generar una pluralidad de secuencias de máscaras de base, acorde con una segunda parte de bits de información, y un sumador (860), para sumar las secuencias biortogonales de base y las secuencias de máscara de base, generadas desde el generador de secuencia y el generador de secuencia de máscara.

Tipo: Patente Internacional (Tratado de Cooperación de Patentes). Resumen de patente/invención. Número de Solicitud: PCT/KR2000/000731.

Solicitante: SAMSUNG ELECTRONICS CO., LTD..

Nacionalidad solicitante: República de Corea.

Dirección: 416 MAETAN-DONG, PALDAL-GU SUWON-SHI, KYUNGKI-DO 442-370 REPUBLICA DE COREA.

Inventor/es: KANG, HEE-WON, KIM, JAE-YOEL.

Fecha de Publicación: .

Clasificación Internacional de Patentes:

- H03M13/00 ELECTRICIDAD. › H03 CIRCUITOS ELECTRONICOS BASICOS. › H03M CODIFICACION, DECODIFICACION O CONVERSION DE CODIGO, EN GENERAL (por medio de fluidos F15C 4/00; convertidores ópticos analógico/digitales G02F 7/00; codificación, decodificación o conversión de código especialmente adaptada a aplicaciones particulares, ver las subclases apropiadas, p. ej. G01D, G01R, G06F, G06T, G09G, G10L, G11B, G11C, H04B, H04L, H04M, H04N; cifrado o descifrado para la criptografía o para otros fines que implican la necesidad de secreto G09C). › Codificación, decodificación o conversión de código para detectar o corregir errores; Hipótesis básicas sobre la teoría de codificación; Límites de codificación; Métodos de evaluación de la probabilidad de error; Modelos de canal; Simulación o prueba de códigos (detección o correción de errores para la conversión de código o la conversión analógico/digital, digital/analógica H03M 1/00 - H03M 11/00; especialmente adaptados para los computadores digitales G06F 11/08; para el registro de la información basado en el movimiento relativo entre el soporte de registro y el transductor G11B, p. ej. G11B 20/18; para memorias estáticas G11C).

- H04B1/707 H […] › H04 TECNICA DE LAS COMUNICACIONES ELECTRICAS. › H04B TRANSMISION. › H04B 1/00 Detalles de los sistemas de transmision, no cubiertos por uno de los grupos H04B 3/00 - H04B 13/00; Detalles de los sistemas de transmisión no caracterizados por el medio utilizado para la transmisión. › que usa modulación en secuencia directa.

- H04J11/00 H04 […] › H04J COMUNICACIONES MULTIPLEX (peculiar de la transmisión de información digital H04L 5/00; sistemas para transmitir las señales de televisión simultánea o secuencialmente H04N 7/08; en las centrales H04Q 11/00). › Sistemas múltiplex ortogonales (H04J 13/00 tiene prioridad).

- H04J13/00 H04J […] › Sistemas de multiplexación por división de código (para salto de frecuencia H04B 1/713).

- H04J13/10 H04J […] › H04J 13/00 Sistemas de multiplexación por división de código (para salto de frecuencia H04B 1/713). › Generación de código.

- H04J13/12 H04J 13/00 […] › Generación de códigos ortogonales.

- H04L1/00 H04 […] › H04L TRANSMISION DE INFORMACION DIGITAL, p. ej. COMUNICACION TELEGRAFICA (disposiciones comunes a las comunicaciones telegráficas y telefónicas H04M). › Disposiciones para detectar o evitar errores en la información recibida.

- H04L9/06 H04L […] › H04L 9/00 Disposiciones para las comunicaciones secretas o protegidas. › utilizando el aparato de cifrado registros de desplazamiento o memorias para la codificación por bloques, p. ej. sistema DES.

- H04Q7/38

Fragmento de la descripción:

Aparato de codificación de un indicador de combinación de formato de transporte para un sistema de comunicación.

Antecedentes de la invención

Esta invención se refiere en general a un aparato, y método, de transmisión de información en un sistema IMT 2000, y en particular a un aparato, y método, para transmitir un indicador de combinación de formato de transporte (TFCI) .

Un sistema de comunicación móvil CDMA (en adelante, aludido como sistema IMT 2000) transmite, en general, tramas que proporcionan un servicio de voz, un servicio de imagen, un servicio de caracteres, en un canal físico tal como un canal de datos físico dedicado (DPDCH) , a una velocidad de datos fija, o variable. En el caso en que las tramas de datos que incluyen esa clase de servicios, son transmitidas a una velocidad de datos fija, no hay necesidad de informar a un receptor de la velocidad de esparcimiento de cada trama de datos. Por otra parte, si las tramas de datos son transmitidas a una velocidad de datos variable, lo que implica que cada trama de datos tiene una velocidad de datos diferente, un transmisor debería informar al receptor de la velocidad de esparcimiento de cada trama de datos, determinada mediante su velocidad de datos. Una velocidad de datos es proporcional a la velocidad de transmisión de datos, y la velocidad de transmisión de datos es inversamente proporcional a una velocidad de esparcimiento, en un sistema general IMT 2000.

Para la transmisión de tramas de datos a un velocidad de datos variable, un campo TFCI de una DPCCH, informa a un receptor de la velocidad de datos de la trama de servicio actual. El campo TFCI, incluye un TFCI que indica mucha información, incluida la velocidad de datos de una trama de servicio. El TFCI es información que ayuda a un servicio de voz, o de datos, para que sean proporcionados de forma fidedigna.

Las figuras 1A a 1D, ilustran ejemplos de aplicaciones de TFCI. La figura 1A ilustra la aplicación del TFCI a un enlace ascendente DPDCH, y un canal de control físico dedicado del enlace ascendente (DPCCH) . La figura 1B ilustra la aplicación del TFCI a un canal de acceso aleatorio (RACH) . La figura 1C ilustra la aplicación del TFCI a un enlace descendente DPDCH, y un enlace descendente DPCCH. La figura 1D ilustra la aplicación del TFCI a un canal físico de control común secundario (SCCPCH) .

En referencia a las figuras 1A a 1D, una trama está comprendida de 16 segmentos, y cada segmento tiene un campo TFCI. Así, una trama incluye 16 campos TFCI. Un campo TFCI incluye NTFCI bits, y un TFCI en general tiene 32 bits en una trama. Para transmitir el TFCI de 32 bits en una trama, pueden asignarse 2 bits TFCI a cada una de las 16 segmentos (Tslot = 0, 625 ms) .

La figura 2 es una diagrama de bloques de una estación base transmisora, en un sistema IMT 2000 general.

En referencia a la figura 2, los multiplicadores 211, 231, y 232 multiplican señales de entrada por coeficientes de ganancia G1, G3, y G5. Los multiplicadores 221, 241, y 242 multiplican las palabras de código TFCI (símbolos de código TFCI) , recibidas de los correspondientes codificadores TFCI, por coeficientes de ganancia G2, G4, y G6. Los coeficientes de ganancia G1 a G6 pueden tener diferentes valores, de acuerdo con los tipos de servicio o situaciones de entrega. Las señales de entrada incluyen pilotos y señales de control de potencia (TPCs) , de unos datos de DPCCH y unos datos de DPDCH. Un multiplexor 212 inserta símbolos de código TFCI de 32 bits (palabras de código TFCI) , recibidos desde el multiplicador 221, en los campos TFCI, como se muestra en la figura 1C. Un multiplexor 242 inserta símbolos de código TFCI de 32 bits, recibido desde el multiplexor 241, en los campos TFCI. Un multiplexor 252 inserta símbolos de código TFCI de 32 bits, recibidos desde el multiplexor 242, en los campos TFCI. La inversión de los símbolos de código TFCI en campos TFCI, se muestra en las figuras 1A a 1D. Los 32 símbolos de código se obtienen codificando bits TFCI (bits de información) que definen la velocidad de datos de una señal de datos en un canal de datos correspondiente. Los convertidores de serie a paralelo (S/Ps) 1º, 2º, y 3º 213, 233, y 234 separan las salidas de los multiplexores 212, 242, 252, en canales I y canales Q. Los multiplicadores 214, 222, y 235 a 238, multiplican las salidas de los S/Ps 213, 233, y 234 por códigos de canalización Cch1, Cch2, y Cch3. Los códigos de canalización son códigos ortogonales. Un primer sumador 215 suma las salidas de los multiplicadores 214, 235, y 237, y genera una señal de canal I, y un segundo sumador 223 suma las salidas de los multiplicadores 222, 236, y 238, y genera una señal de canal Q. Un dispositivo de desfasado 224, desfasa la fase de la señal de canal Q recibida desde el segundo sumador 223 en 90º. Un sumador 216 suma las salidas del primer sumador 215 y el dispositivo de desfasado 224, y genera una señal compleja I+jQ. Un multiplicador 217 cifra la señal compleja con una secuencia PN compleja Cscramb asignada a la estación base. Un procesador de señal (S/P) 218, separa la señal cifrada en un canal I y un canal Q. Filtros de paso bajo (LPFs, low pass filters) 219 y 225, limitan los anchos de banda de las señales de canal I y canal Q, recibidas desde el S/P 218, mediante filtrado de paso bajo. Los multiplicadores 220 y 226, multiplican las salidas de los LPFs 219 y 225, por las ondas portadoras cos (2πfct) y sen (2πfct) , respectivamente, transformando de ese modo las salidas de los LPFs 219 y 225, a una banda de RF (Frecuencia de Radio) . Un sumador 227 suma las señales de RF de canal I y canal Q.

La figura 3 es un diagrama de bloques, de un transmisor de estación móvil en el sistema IMT 2000 general.

En referencia a la figura 3, los multiplicadores 311, 321, y 323 multiplican las señales correspondientes mediante códigos de canalización Cch1, Cch2, y Cch3. Las señales 1, 2, 3 son la primera, segunda y tercera señal DPDCH. Una señal de salida 4 incluye pilotos y TPCs de un DPCCH. Los bits de información TFCI son codificados en símbolos de código TFCI de 32 bits, por un codificador TFCI 309. Un multiplicador 310 inserta unos símbolos de código TFCI de 32 bits en la señal 4, como se muestra en la figura 1A. Un multiplicador 325 multiplica una señal DPCCH, que incluye símbolo de código TFCI recibido desde el multiplicador 310, por un código de canalización Cch4. Los códigos de canalización Cch1 a Cch4, son códigos ortogonales. Los 32 símbolos de código TFCI se obtienen codificando los bits de información TFCI que definen la velocidad de datos de las señales DPDCH. Los multiplicadores 312, 322, 324, y 326, multiplican las salidas de los multiplicadores 311, 321, 323, y 325, por coeficientes de ganancia G1 a G4, respectivamente. Los coeficientes de ganancia G1 a G4 pueden tener diferentes valores. Un primer sumador 313, genera una señal de canal I, mediante añadir las salidas de los multiplicadores 312 y 322. Un segundo sumador 327, genera una señal de canal Q mediante sumar las salidas de los multiplicadores 324 y 326. Un dispositivo de desfasado 328, desfasa la fase de la señal de canal Q recibida desde el segundo sumador 327 en 90º. Un sumador 314 suma las salidas del primer sumador 313 y el dispositivo de desfasado 328, y genera una señal compleja I+jQ. Un multiplicador 315 cifra la señal compleja con una secuencia PN Cscramb, asignada a una estación base. Un S/P 329 divide la señal cifrada en un canal I y un canal Q. Los LPFs 316 y 330 hacen una filtración de paso bajo, de las señales de canal I y canal Q recibidas desde el S/P 329, y generan señales con anchos de banda limitados. Los multiplicadores 317 y 331, multiplican las salidas de los LPFs 316 y 330, por ondas portadoras cos (2πfct) y sen (2πfct) respectivamente, transformando de ese modo las salidas de los LPFs 316 y 330, a una banda RF. Un sumador 318 suma las señales de RF de canal I y canal Q.

Los TFCIs son clasificados en las categorías de TFCI básico y TFCI extendido. El TFCI básico representa 1 a 64 informaciones diferentes, que incluyen velocidades de datos de los canales de datos correspondientes, usando 6 bits de información TFCI, mientras que el TFCI extendido representa 1 a 128, 1 a 256, 1 a 512, ó 1 a 1024 informaciones diferentes, usando 7, 8, 9 ó 10 bits de información TFCI. El TFCI...

Reivindicaciones:

1. Un aparato de codificación de Indicador de Combinación de Formato de Transporte TFCI para un sistema de comunicación, que comprende:

un generador de secuencia ortogonal (810) , para generar una pluralidad de secuencias biortogonales de base, acorde con una primera parte de bits de información;

un generador de secuencia de máscara (820) , para generar una pluralidad de secuencias de máscaras de base, acorde con una segunda parte de bits de información, y

un sumador (860) , para sumar las secuencias biortogonales de base y las secuencias de máscara de base, generadas desde el generador de secuencia y el generador de secuencia de máscara.

2. El aparato de codificación TFCI de la reivindicación 1, donde la pluralidad de secuencias biortogonales de base son un primer código de Walsh W1, un segundo código de Walsh W2, un tercer código de Walsh W4, un cuarto código de Walsh W8, un quinto código de Walsh W16, y una secuencia todo 1

, donde los códigos de Walsh W1, W2, W4, W8 y W16 son códigos de Walsh de base, que son códigos desde los que puede derivarse todos los demás códigos de Walsh, a través de la suma de estos códigos de Walsh de base.

3. El aparato de codificación de la reivindicación 1 o la 2, donde el generador de secuencia de máscara está adaptado para generar una primera secuencia-m y una segunda secuencia-m, la cuales pueden ser sumadas entre sí para formar un código Gold, está además adaptado para formar un primer grupo de secuencia que tiene secuencias formadas mediante desplazar cíclicamente la primera secuencia-m, y un segundo grupo de secuencia que tiene secuencias formadas mediante desplazar cíclicamente la segunda secuencia-m, está además adaptado para generar, y aplicar, una función de transposición por columna a las secuencias en el primer grupo, para transformar las secuencias en el primer grupo en secuencias ortogonales, está además adaptado para insertar una columna de 0

en el frontal de las secuencias en el segundo grupo, y está además adaptado para generar y aplicar una función de transposición por columna inversa, a las secuencias en el segundo grupo, para transformar las frecuencias en el segundo grupo en secuencias de máscara.

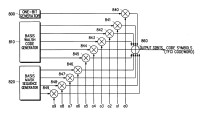

4. El aparato de codificación TFCI de cualquiera de las reivindicaciones 1 a 3, donde el aparato de codificación comprende una pluralidad de primeros multiplicadores (840 a 845) , para multiplicar las secuencias biortogonales de base por la primera parte de los bits de información, una pluralidad de segundos multiplicadores (846 a 849) , para multiplicar las secuencias de máscara de base por la segunda parte de los bits de información, y donde el sumador está adaptado para sumar las salidas de los multiplicadores primero y segundo.

5. El aparato de codificación de cualquiera de las reivindicaciones 1 a 4, donde el generador de secuencia ortogonal (810) está adaptado para entregar secuencias de longitud 30, en las que los símbolos #0 y #16 están excluidos de los códigos de Walsh de longitud 32.

6. El aparato de codificación de cualquiera de las reivindicaciones 1 a 5, donde el generador de secuencia de máscara (820) está adaptado para entregar secuencias de longitud 30, en las que los símbolos #0 y #16 están excluidos de las secuencias de máscara de base de longitud 32.

7. El aparato de codificación de la reivindicación 5 o la 6, donde el código de Walsh de base W1 es 01010101010101010101010101010101

, el código de Walsh de base W2 es 00110011001100110011001100110011

, el código de Walsh de base W4 es 00001111000011110000111100001111

, el código de Walsh de base W8 es 00000000111111110000000011111111

, y el códigos de Walsh de base W16 es 00000000000000001111111111111111

.

8. El aparato de codificación TFCI de cualquiera de las reivindicaciones 5 a 7, donde las secuencias de máscara de base son una primera secuencia de máscara M1 00101000011000111111000001110111

, una segunda secuencia de máscara M2, 00000001110011010110110111000111

, una tercera secuencia de máscara M4 00001010111110010001101100101011

, y una cuarta secuencia de máscara M8 00011100001101110010111101010001

.

9. El aparato de codificación de cualquiera de las reivindicaciones 1 a 4, donde el aparato de codificación comprende medios, adaptados para entregar una secuencia de longitud 30, en la que los símbolos #0 y #16, están excluidos de una secuencia construida sumando las secuencias biortogonales de base y las secuencias de máscara de base.

10. El aparato de codificación de la reivindicación 9, donde las secuencias biortogonales de base son 01010101010101010101010101010101

, 00110011001100110011001100110011

, 00001111000011110000111100001111

, 00000000111111110000000011111111

00000000000000001111111111111111

, y donde las secuencias de máscara de base son 00101000011000111111000001110111

, 00000001110011010110110111000111

, 00001010111110010001101100101011

, 00011100001101110010111101010001

.

Patentes similares o relacionadas:

Aparato de comunicación inalámbrica y procedimiento de generación de señales de referencia, del 29 de Julio de 2020, de Sun Patent Trust: Un aparato de comunicación para una estación base que comprende: un transmisor, el cual, en operación, transmite, a un terminal, información […]

Procedimiento y aparato para inserción de índice de bloque de código en un sistema celular de comunicación inalámbrica, del 29 de Julio de 2020, de SAMSUNG ELECTRONICS CO., LTD.: Un procedimiento de un terminal en un sistema de comunicación inalámbrica, comprendiendo el procedimiento: recibir, de una estación base, un bloque de información maestra, […]

Método y dispositivo de codificación, del 15 de Julio de 2020, de HUAWEI TECHNOLOGIES CO., LTD.: Un método de codificación, que comprende: realizar (S101), mediante un extremo de transmisión basado en un polinomio de verificación de redundancia cíclica, […]

Información de control en un sistema de comunicación inalámbrica, del 15 de Julio de 2020, de QUALCOMM INCORPORATED: Un procedimiento para enviar datos de tráfico e información de control en un sistema de comunicación inalámbrica, que comprende: realizar conformación de haces […]

Detección y comprobación de error de señalización de retroalimentación en sistemas de comunicación inalámbrica de MIMO, del 15 de Julio de 2020, de INTERDIGITAL TECHNOLOGY CORPORATION: Un método implementado en una unidad de transmisión recepción inalámbrica, WTRU, caracterizado por que el método comprende: proporcionar una pluralidad […]

Repetición de transmisiones de señales en sistemas de comunicación, del 15 de Julio de 2020, de SAMSUNG ELECTRONICS CO., LTD.: Un procedimiento para que un equipo de usuario, UE, transmita una señal de acuse de recibo en un sistema de comunicación, comprendiendo el procedimiento: transmitir la señal […]

Control adaptativo de sobrecarga de pares en redes móviles, del 1 de Julio de 2020, de Microsoft Technology Licensing, LLC: Un método informatizado para ajustar adaptativamente una tasa de transacción en un nodo de la red móvil , el método informatizado que comprende: recibir […]

Método y aparato para determinar el tamaño de bloque de transporte, del 1 de Julio de 2020, de HUAWEI TECHNOLOGIES CO., LTD.: Un método para determinar un tamaño de bloque de transporte, que comprende: recibir (S24), mediante un dispositivo de terminal, información de control enviada […]