Dispositivo interruptor de potencia controlado por semiconductores y sistema interruptor asociado.

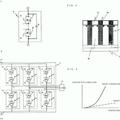

Sistema interruptor (SI) que comprende una pluralidad N de dispositivos interruptores de potencia controlados porsemiconductores (DI) dispuestos en serie,

comprendiendo un dispositivo interruptor de potencia controlado porsemiconductores (DI):

- un circuito de control (CC) capaz de efectuar un desfase de la tensión eléctrica y una adaptación encorriente eléctrica y tensión eléctrica;

- una pluralidad de interruptores elementales de semiconductores (IEa, IEb, IEc e IEd) montados en paralelo;

y

- un circuito común de limitación de tensión eléctrica (CCL) para mantener la tensión eléctrica en los bornesde dichos interruptores elementales (IEa, IEb, IEc e IEd) inferior a una tensión eléctrica de umbral (S) inferior ala tensión eléctrica máxima intrínseca de un interruptor elemental (IEa, IEb, IEc e IEd), estando dispuesto dichocircuito común de limitación (CCL) en paralelo con dichos interruptores elementales (IEa, IEb, IEc e IEd);

caracterizado porque N respeta la relación:

(N - 1) x S >V

en la que:

S representa una tensión eléctrica de umbral de un dispositivo interruptor de potencia controlado porsemiconductor (DI); y

V representa una tensión eléctrica máxima admisible en los bornes del sistema interruptor (SI)implementando un dispositivo adicional que no es necesario para soportar la tensión máxima en los bornes delsistema interruptor permitiendo al sistema interruptor permanecer operativo en caso de avería de cortocircuito de noimporta cuál de los dispositivos interruptores de potencia controlado por semiconductores (DI) de la pluralidad quecomponen el sistema interruptor (SI).

Tipo: Patente Europea. Resumen de patente/invención. Número de Solicitud: E10151113.

Solicitante: THALES.

Nacionalidad solicitante: Francia.

Dirección: 45, RUE DE VILLIERS 92200 NEUILLY SUR SEINE FRANCIA.

Inventor/es: LAMBERT,MARC, SAUSSEZ,YVES, MICHEL,RAYMOND.

Fecha de Publicación: .

Clasificación Internacional de Patentes:

- H03K17/0814 ELECTRICIDAD. › H03 CIRCUITOS ELECTRONICOS BASICOS. › H03K TECNICA DE IMPULSO (medida de las características de los impulsos G01R; modulación de oscilaciones sinusoidales por impulsos H03C; transmisión de información digital, H04L; circuitos discriminadores de detección de diferencia de fase entre dos señales de conteo o integración de ciclos de oscilación H03D 3/04; control automático, arranque, sincronización o estabilización de generadores de oscilaciones o de impulsos electrónicos donde el tipo de generador es irrelevante o esta sin especificar H03L; codificación, decodificación o conversión de código, en general H03M). › H03K 17/00 Conmutación o apertura de puerta electrónica, es decir, por otros medios distintos al cierre y apertura de contactos (amplificadores controlados H03F 3/72; disposiciones de conmutación para los sistemas de centrales que utilizan dispositivos estáticos H04Q 3/52). › por medidas tomadas en el circuito de salida.

PDF original: ES-2438781_T3.pdf

Fragmento de la descripción:

Dispositivo interruptor de potencia controlado por semiconductores y sistema interruptor asociado La presente invención se refiere a una pluralidad N de dispositivos de interruptor de potencia controlado, a semiconductores y sistema asociado de limitación de tensión eléctrica.

Un interruptor es un dispositivo que permite interrumpir o restablecer el paso de corriente en un circuito eléctrico mediante la apertura o cierre de este circuito.

Un interruptor de potencia controlado por semiconductores elemental puede comprender un MOSFET, acrónimo de “Metal-Oxide Semiconductor Field Effect Transistor”, un IGBT, acrónimo de “Isolated Gate Bipolar Transistors”, unos transistores bipolares o cualquier otro componente que module la corriente que lo atraviesa según una señal aplicada a su electrodo de control. En el caso de los MOSFET y de los IGBT, este electrodo se denomina comúnmente la “rejilla”.

La invención se puede utilizar para constituir un interruptor de potencia. En lo que sigue en la descripción, de manera no limitativa, la invención se describirá mediante unos modos de realización que comprenden unos MOSFET.

Un MOSFET posee tres electrodos: una fuente que permite emitir unos electrodos en un canal, un drenaje que recoge los electrodos en el otro extremo del canal y una rejilla cuya tensión fuente-rejilla controla el paso de electrones.

La tensión eléctrica de umbral intrínseca VGS THRESHOLD (“threshold” significa umbral en lengua anglosajona) se define como la tensión eléctrica entre la rejilla y la fuente para la que aparece la zona de inversión, es decir la creación del canal de conducción entre el drenaje y la fuente. Cuanto más se incrementa esta tensión eléctrica más allá del umbral VGS THRESHOLD, más dejará pasar la corriente el componente. Si se aplica una tensión eléctrica rejilla-fuente VGS inferior a este umbral, el componente no deja pasar corriente entre el drenaje y la fuente. Esto es verdad mientras que la tensión eléctrica drenaje-fuente Vds permanezca inferior a la tensión eléctrica drenaje-fuente máxima Vdss que puede soportar el MOSFET cuando está bloqueado. El valor de esta tensión eléctrica se especifica por el fabricante. El valor proporcionado corresponde a esta tensión eléctrica máxima Vdss, en ausencia de tensión eléctrica rejilla-fuente (cortocircuito) . Su sigla normal es Vdss (por Vds “shorted” en lengua anglosajona) . Si se sobrepasa esta tensión eléctrica máxima Vdss, el MOSFET deja pasar corriente eléctrica, pero puede destruirse durante este paso.

Aunque ciertos componentes se conciban para soportar una puesta en conducción fugaz por sobrepaso de la tensión eléctrica máxima Vdss, es preferible no aplicar esta tensión eléctrica al componente porque, a un paso de corriente eléctrica con la tensión eléctrica importante, corresponde una potencia importante disipada en el componente. Esto puede comunicar al componente una energía que sobrepase la energía máxima que puede almacenar y por tanto destruirlo.

Por otro lado, en ciertos campos de aplicación, tal como el campo espacial, las reglas de diseño imponen permanecer netamente por debajo de esta tensión máxima, generalmente por debajo del 80% de esta tensión máxima.

Finalmente, los componentes de semiconductor son sensibles a las partículas energizadas, tales como los iones pesados. Estos iones pesados están presentes en el entorno espacial. El diseño de los equipos destinados a los lanzamientos astronáuticos o en cohetes, en los satélites, en las estaciones orbitales, en las sondas y otros vehículos espaciales, deben imperativamente tener en cuenta estas radiaciones.

Para los MOSFET, esta sensibilidad surge cuando la tensión eléctrica Vds aplicada entre el drenaje y la fuente sobrepasa un umbral propio de cada modelo de componente. El impacto de una partícula energizada sobre un MOSFET sometido a una tensión eléctrica drenaje-fuente Vds superior al umbral de sensibilidad puede provocar su destrucción. Existen unos MOSFET cualificados como “endurecidos”, o “radiation hardened” o “RadHard” en lengua anglosajona, resistentes a las partículas energizadas. Su precio de coste es de quinientas a mil veces superior al de los componentes ordinarios.

Como se ha indicado anteriormente, la vulnerabilidad de los componentes surge cuando la tensión eléctrica a la que están sometidos sobrepasa una tensión eléctrica de umbral. Así, a título de ejemplo, un MOSFET ordinario, no endurecido, especificado para una diferencia de tensión eléctrica Vds entre el drenaje y la fuente máxima Vdss de 100 V, es insensible a las partículas energizadas cuando la tensión eléctrica Vds entre el drenaje y la fuente permanece inferior a 50 V.

Para unos componentes ordinarios, la relación entre la tensión eléctrica máxima admisible y la tensión eléctrica máxima para la que son insensibles a las partículas energizadas, disminuye con la tensión máxima permitida: del 50 al 65% para un MOSFET de Vdss de 100 V, contra el 45% para un MOSFET de Vdss de 400 V. Por el contrario, la resistencia eléctrica intrínseca Rdson del MOSFET crece con la tensión Vdss máxima admisible.

Los documentos “Paralleling Of Power MOSFETs For Higher Power Output” de James B. Forsythe, “Application Note AN-941 Paralleling HEXFET Power MOSFETs”, “Parallel Connection of IGBT and MOSFET Power Modules” de Serge Bontemps, y “Analysis of Avalanche Behaviour for Paralleled MOSFETs” de Jingdong Chen, Scott Downer, Anthony Murray y David Divins, divulgan unas conexiones en paralelo de interruptores elementales, tales como unos MOSFET, o IGBT.

La tesis “Le transistor MOSFET en commutation : Application aux associations série et parallèle de composants à grille isolée.” de Pierre-Olivier JEANNIN defendida en el Institut National Polytechnique de Grenoble presenta el estado de la técnica para las colocaciones en serie o paralelo de componentes interruptores. No presenta combinaciones en serie y paralelo simultáneas.

Los documentos siguientes dan el estado de la técnica para la colocación en serie de componentes interruptores: “Suitability and Optimization of High-Voltage IGBTs for Series Connection With Active Voltage Clamping” Friedhelm Bauer, Member, IEEE, Luc Meysenc, Member, IEEE y Alice Piazzesi, Member, IEEE en IEEE TRANSACTIONS ON POWER ELECTRONICS, VOL. 20, Nº 6, noviembre de 2005, “Active Voltage Control of IGBTs for High Power Applications” Patrick R. Palmer, Member, IEEE y Haile S. Rajamani en IEEE TRANSACTIONS ON POWER

ELECTRONICS, VOL. 19, Nº 4, julio de 2004, “Optimisation and integration of an active clamping circuit for IGBT series association.” J. Saiz, M. Mermet D. Frey, P.O. Jeannin, JL. Schanen Member IEEE, P. Muszicki en IEEE Volumen 2, Edición 30 Sep-4 Oct 2001 página (s) :1046 - 1051 vol.2.

Estos documentos divulgan siempre unos dispositivos de limitación de tensión eléctrica que no generan más que un componente y explotan éste mediante una acción sobre su electrodo de control. Este tipo de solución no se puede utilizar para unos componentes montados en paralelo, porque el componente que tenga el umbral de limitación más bajo será el único en efectuar esta limitación lo que implica un desequilibrio de las disipaciones entre los elementos montados en paralelo.

Estos documentos no divulgan interruptores elementales montados en paralelo para los que se pueda garantizar que su tensión eléctrica permanece inferior a un valor inferior a su tensión eléctrica máxima entre el drenaje y la fuente Vdss.

Un objetivo de la invención es proponer un dispositivo interruptor de potencia controlado por semiconductores, que soporte el caso de avería simple de cortocircuito y que tenga una duración de funcionamiento mejorada (por disminución de las cargas en tensión, corriente y potencia, impuestas a los componentes) , que utilizan una colocación en serie y en paralelo de interruptores elementales, para los que se puede garantizar que la tensión eléctrica Vds permanece inferior a un valor inferior a una tensión eléctrica elegida, con el fin adecuado para unas aplicaciones que requieran esta condición.

También, según la invención, se propone un sistema interruptor que comprende una pluralidad N de dispositivos interruptores de potencia controlados por semiconductores dispuestos en serie, que comprende un dispositivo interruptor de potencia controlado por semiconductores:

- un circuito de control capaz de efectuar un desfase de la tensión eléctrica y una adaptación de la señal de tensión y de corriente;... [Seguir leyendo]

Reivindicaciones:

1. Sistema interruptor (SI) que comprende una pluralidad N de dispositivos interruptores de potencia controlados por semiconductores (DI) dispuestos en serie, comprendiendo un dispositivo interruptor de potencia controlado por semiconductores (DI) :

-un circuito de control (CC) capaz de efectuar un desfase de la tensión eléctrica y una adaptación en corriente eléctrica y tensión eléctrica;

-una pluralidad de interruptores elementales de semiconductores (IEa, IEb, IEc e IEd) montados en paralelo; y

-un circuito común de limitación de tensión eléctrica (CCL) para mantener la tensión eléctrica en los bornes de dichos interruptores elementales (IEa, IEb, IEc e IEd) inferior a una tensión eléctrica de umbral (S) inferior a la tensión eléctrica máxima intrínseca de un interruptor elemental (IEa, IEb, IEc e IEd) , estando dispuesto dicho circuito común de limitación (CCL) en paralelo con dichos interruptores elementales (IEa, IEb, IEc e IEd) ;

caracterizado porque N respeta la relación:

(N – 1) x S > V

en la que:

S representa una tensión eléctrica de umbral de un dispositivo interruptor de potencia controlado por semiconductor (DI) ; y V representa una tensión eléctrica máxima admisible en los bornes del sistema interruptor (SI)

implementando un dispositivo adicional que no es necesario para soportar la tensión máxima en los bornes del sistema interruptor permitiendo al sistema interruptor permanecer operativo en caso de avería de cortocircuito de no importa cuál de los dispositivos interruptores de potencia controlado por semiconductores (DI) de la pluralidad que componen el sistema interruptor (SI) .

2. Sistema interruptor (SI) según la reivindicación 1, en el que un interruptor elemental (IEa, IEb, IEc e IEd) comprende un transistor de efecto de campo de rejilla metal-óxido (M1a, M1b, M1c, M1d) .

3. Sistema interruptor (SI) según la reivindicación 1 o 2, en el que dicho circuito común de limitación (CCL) comprende un circuito derivador de corriente eléctrica (CD) y un generador de señal de control (GSC) de dicho circuito derivador (CD) .

4. Sistema interruptor (SI) según la reivindicación 3, en el que dicho circuito derivador de corriente eléctrica (CD) comprende un transistor de efecto de campo de rejilla metal-óxido (M2) , y dicho generador de señal de control (GSC) de dicho circuito derivador (CD) comprende unos medios para asegurar una referencia constante de tensión eléctrica y un amplificador de la diferencia entre la tensión eléctrica aplicada a los bornes del dispositivo interruptor (DI) y dicha tensión eléctrica de referencia.

5. Sistema interruptor (SI) según una de las reivindicaciones precedentes, que comprende, además, un circuito de amortiguación de oscilaciones (CAO) .

6. Sistema interruptor (SI) según la reivindicación 5, en el que dicho circuito de amortiguación de oscilaciones comprende una resistencia (R) y un condensador (C) montados en serie.

7. Sistema interruptor según una de las reivindicaciones precedentes, que comprende, además, un circuito de recuperación de energía (CRE) .

8. Sistema interruptor según la reivindicación 7, en el que dicho circuito de recuperación de energía (CRE) comprende un conjunto de cuatro diodos montados en el mismo sentido, dispuestos en paralelo a dicha pluralidad de dispositivos interruptores de potencia controlados por semiconductores (DI1, DI2, DI3, DI4, DI5) , comprendiendo dicho conjunto de cuatro diodos dos subconjuntos de dos diodos montados en paralelo, montados en serie.

9. Ondulador de control (OND) de un motor síncrono polifásico caracterizado porque comprende, por fase, dos sistemas de interruptores según una de las reivindicaciones precedentes.

Patentes similares o relacionadas:

Procedimiento para la descarga de un acumulador de energía eléctrica, del 27 de Mayo de 2020, de Siemens Energy Global GmbH & Co. KG: Procedimiento para la descarga de un acumulador de energía eléctrica que está conectado con un circuito electrónico mediante un primer conductor eléctrico y […]

Dispositivo con voltaje de extremo de interruptor controlable, del 17 de Julio de 2019, de Shanghai Shift Electrics Co. Ltd: Un dispositivo con voltaje controlable entre contactos de interruptor, que comprende: una unidad de señal del interruptor, en el que la unidad de señal […]

Un método para el control de un voltaje en terminales de un semiconductor de potencia en un circuito de potencia eléctrica y un circuito de potencia eléctrica, del 3 de Diciembre de 2018, de Energy Technology S.r.l: Un método para controlar un voltaje de un semiconductor de potencia de un circuito de potencia eléctrica, que comprende los siguientes pasos: - predisponer […]

Dispositivo inversor, dispositivo de accionamiento de motor eléctrico, dispositivo de refrigeración/acondicionador de aire y sistema de generación de potencia eléctrica, del 27 de Septiembre de 2018, de MITSUBISHI ELECTRIC CORPORATION: Un dispositivo de accionamiento de motor para accionar un motor , que comprende:

un dispositivo inversor;

un detector (3a, 3b) de corriente que […]

Dispositivo inversor, dispositivo de accionamiento de motor eléctrico, dispositivo de refrigeración/acondicionador de aire y sistema de generación de potencia eléctrica, del 27 de Septiembre de 2018, de MITSUBISHI ELECTRIC CORPORATION: Un dispositivo de accionamiento de motor para accionar un motor , que comprende:

un dispositivo inversor;

un detector (3a, 3b) de corriente que […]

Convertidor de potencia, del 24 de Agosto de 2016, de FAIVELEY TRANSPORT: Convertidor de potencia que comprende una pluralidad de transformadores, estando los devanados primarios (P0, P1, P2) de estos transformadores conectados entre sí por unos […]

Módulo de conmutación para uso en un dispositivo para limitar y/o cortar la corriente de una línea de transmisión o distribución de potencia, del 9 de Abril de 2014, de ABB TECHNOLOGY AG: Un dispositivo para limitar y/o cortar una corriente eléctrica que fluye a través de una línea de transmisión o distribución […]

Desviador de nivel para un conmutador de accionamiento para componentes semiconductores de potencia, del 11 de Abril de 2012, de SEMIKRON ELEKTRONIK GMBH & CO. KG: Desviador de nivel para la transmisión unidireccional de una señal desde una primera sección del circuito a un primer potencial hasta una segunda sección […]

CIRCUITO DE CONTROL, del 4 de Marzo de 2011, de FLEXTRONICS INTERNATIONAL KFT: Circuito de control para al menos una carga inductiva (M1, M2), que comprende primeras y segundas ramas de carga situadas entre una primera conexión de tensión […]

CIRCUITO DE CONTROL, del 4 de Marzo de 2011, de FLEXTRONICS INTERNATIONAL KFT: Circuito de control para al menos una carga inductiva (M1, M2), que comprende primeras y segundas ramas de carga situadas entre una primera conexión de tensión […]