Circuito y procedimiento de selección de señal analógica.

Sistema para selección de señal de entrada analógica para sistemas que tienen más de una señal de entrada analógica,

para seleccionar la señal de entrada analógica requerida caracterizado porque comprende;

- un puerto de GPIO que tiene capacidad de salida de la señal PWM (32),

- un filtro paso bajo (R26, C22) que está conectado a dicho puerto de GPIO para obtener diferentes niveles analógicos para diferentes ciclos de trabajo de la señal PWM,

- transistores (Q1, Q2, Q3, Q7, Q8, Q9, Q10) para seleccionar la señal de entrada analógica requerida,

- resistencias (R8, R9, R10, R11, R15, R16, R17, R21, R23, R25) que están conectadas a la base de los transistores para ser utilizados como divisores de tensión para activar o desactivar los transistores de selección,

- diodos (D6, D7, D8, D9) para enviar la señal de entrada analógica seleccionada a una salida del sistema de selección de señal de entrada analógica.

Tipo: Patente Europea. Resumen de patente/invención. Número de Solicitud: E11152863.

Solicitante: VESTEL ELEKTRONIK SANAYI VE TICARET A.S.

Nacionalidad solicitante: Turquía.

Dirección: ORGANIZE SANAYI BÖLGESI 45030 MANISA TURQUIA.

Inventor/es: YILMAZLAR ISMAIL.

Fecha de Publicación: .

Clasificación Internacional de Patentes:

- G06F13/38 FISICA. › G06 CALCULO; CONTEO. › G06F PROCESAMIENTO ELECTRICO DE DATOS DIGITALES (sistemas de computadores basados en modelos de cálculo específicos G06N). › G06F 13/00 Interconexión o transferencia de información u otras señales entre memorias, dispositivos de entrada/salida o unidades de procesamiento (circuitos de interfaz para dispositivos de entrada/salida específicos G06F 3/00; sistemas multiprocesadores G06F 15/16). › Transferencia de informaciones, p. ej. sobre un bus (G06F 13/14 tiene prioridad).

PDF original: ES-2441952_T3.pdf

Fragmento de la descripción:

Circuito y procedimiento de selección de señal analógica.

Campo de la invención [0001] La presente invención se refiere a un procedimiento y un circuito que resuelve el problema de asignación de puerto para la selección señales analógicas, que se requiere en receptores de TV, AV etc., mediante la expansión de puertos.

Técnica anterior

Durante los procesos internos, los aparatos de televisión utilizan un gran número de señales de entrada analógicas. Sin embargo, la mayoría de los ICs (circuitos integrados) , tales como el convertidor A/D (CAD) , el decodificador de vídeo, el decodificador de audio de un aparato de TV, no pueden manejar todos las citadas entradas analógicas ya que dichos ICs no tienen suficientes entradas de señal analógica. Para superar el problema explicado, se utiliza conmutador analógico controlado por puerto. Mediante la utilización de dicho conmutador analógico, las señales analógicas 2n son conmutadas a n puertos utilizados. Por ejemplo, para conmutar 4 señales analógicas, se deben utilizar 2 puertos de entrada/salida de propósito general (GPIO) ; para conmutar 8 señales analógicas, deben utilizarse 3 puertos de GPIO. Por tanto, son requeridos más puertos de GPIO para procesar más señales analógicas, y esto produce un problema de asignación de puerto.

Como se muestra en el caso del ejemplo ilustrado en la figura 1 con respecto a la técnica anterior, entradas analógicas 1 a 2n y señales de control, que conmutan las señales analógicas, son enviadas a través de los puertos de GPIO 1 a n. Dichas señales analógicas y de control son procesadas por un multiplexor (11) , obteniéndose la salida analógica requerida (12) . Como se representa en la figura 2, 8 señales de entrada analógicas (XO-X7) se conmutan por un decodificador binario (21) , utilizando dichas señales de control (A, B, C) . En la figura 2, A, B, C representan dichas señales de control enviadas a través de 3 puertos de GPIO para conmutar dichas 8 señales analógicas de entrada (XO-X7) y representando X (23) la salida requerida. Ya que dichos puertos de GPIO emiten señales digitales, tabla de verdad, que se muestra en la figura 2, que explica el proceso de conmutación para 8 estados de acuerdo a condiciones alto y bajo de 3 señales de control (A, B, C) . Para cada estado, una señal de entrada es conectada a la salida.

En el documento de patente EP 1970817 (A2) , se describe un procedimiento y circuito para expansión de puertos. Según la solicitud mencionada, una pluralidad de puertos, es controlada mediante un microprocesador con el fin de activar o desactivar diversos dispositivos. En el documento EP 1970817 (A2) , el estado de más de un puerto de GPIO se controla mediante un controlador de puerto y dicho controlador de puerto está controlado por un solo puerto de dicho microprocesador. Para controlar dichos puertos de GPIO, se utiliza una fuente de modulación de anchura de impulso (PWM) incluida en un microprocesador. Al utilizar el procedimiento explicado, son controlados secuencialmente puertos en espera conectado/desconectado, panel de potencia conectado/desconectado, retroiluminación conectada/desconectada.

De acuerdo con el sistema mencionado en la solicitud de patente con número de publicación US 2006 / 047866 A1, se proporciona un sistema de ordenador en el que una unidad de procesamiento central (UCP) , una memoria y un elemento periférico están conectados a un bus de sistema común y que incluye un circuito de control de acceso a memoria directo (DMAC) para controlar la transferencia de datos entre la memoria y el elemento periférico o entre una primera y una segunda zonas dentro de la memoria, utilizando el bus del sistema sin la participación de la UCP de acuerdo con una instrucción de dicha UCP. El sistema informático también incluye una unidad de generación de impulsos variables, conectada al bus del sistema, para generar una señal de impulsos que tiene un período y una anchura de impulso que se especifica por la UCP. En dicho sistema informático, el DMAC está dispuesto para controlar la transferencia de datos entre las primera y segunda zonas interiores de la memoria de acuerdo con la señal de impulso generada por la unidad de generación de impulso variable. Sin embargo, en el documento US 2006 / 047866, la señal PWM no controla la tasa de transferencia del controlador de DMA mediante la alteración de un nivel de corriente, en contraposición la temporización de la señal de PWM controla directamente el comportamiento del controlador de DMA.

En otro documento de patente, KR 20040093890 (A) , se proporciona un dispositivo para expansión de puertos para comunicar con un dispositivo externo deseado, con una simple operación de selección en un sistema de procesamiento de señal, ofreciendo un dispositivo de expansión de puerto equipado con puertos de expansión. Dicho dispositivo comprende un convertidor de nivel TTL (lógica transistor-transistor) /señal de puerto serie, un controlador y un multiplexor. Dicho convertidor de nivel TTL (lógica transistor-transistor) /señal de puerto serie, está conectado a un puerto serie, y mutuamente convierte una señal de puerto serie y una señal TTL. Por otra parte, dicho controlador genera una señal para seleccionar el dispositivo externo deseado, mediante una señal de control del sistema de procesamiento de señal. Además, dicho multiplexor realiza una operación de conmutación necesaria mediante la señal generada desde el controlador. Dicho convertidor de nivel TTL/señal puerto serie, es operado mediante la operación de conmutación del multiplexor y convierte mutuamente la señal TTL y la señal de puerto serie. El puerto serie expandido está conectado al convertidor de nivel de señal TTL – puerto serie y al dispositivo externo.

Breve descripción de la invención [0007] La presente invención es un procedimiento como se define en la reivindicación 4 y un sistema de circuitos de acuerdo con la reivindicación 1, que resuelve el problema de asignación de puerto para la selección de la señal analógica, que se requiere en receptores de TV, AV etc., mediante la expansión de puertos. Para resolver el problema de asignación de puertos, se utiliza un puerto de GPIO que tiene capacidad de salida de señal PWM. Por tanto, de acuerdo a las características PWM, ciclo de trabajo de la señal PWM se ajusta y se obtienen diferentes niveles de tensión. Además, se concibe un circuito para selección de señal de entrada analógica. Mediante la utilización de dichos diferentes niveles de tensión como entrada de control del circuito de selección de señal de entrada analógica, se selecciona la señal de entrada analógica requerida y se envía a la salida de dicho circuito de selección de señal de entrada analógica.

Objeto de la invención [0008] El objeto de la presente invención es resolver el problema de asignación de puertos para selección de señales analógicas.

Otro objeto de la presente invención es resolver el problema de asignación de puertos mediante utilización de un puerto de GPIO que tiene capacidad de salida de señales PWM.

Otro objeto de la presente invención es seleccionar la señal de entrada analógica requerida mediante el ajuste del ciclo de trabajo de la señal PWM.

Otro objeto de la presente invención es seleccionar de forma independiente la señal de entrada analógica requerida.

Breve descripción de los dibujos [0012]

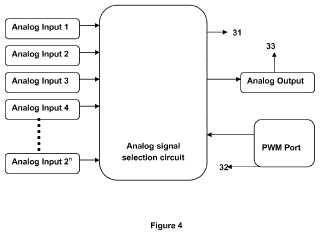

Figura 1: muestra un diagrama de bloques de aplicación de la técnica anterior. Figura 2: muestra un diagrama de circuito de aplicación de la técnica anterior. Figura 3: muestra la señal PWM Figura 4: muestra un diagrama de bloques de la presente invención. Figura 5: muestra un diagrama de circuito de la presente invención. Figura 6: muestra todas las señales de entrada y una señal de salida para una tensión de referencia. Figura 7: muestra el comportamiento del circuito para una señal de control de 0, 5 V. Figura 8: muestra el comportamiento del circuito para una señal de control de 1, 5 V. Figura 9: muestra el comportamiento del circuito para una señal de control de 2, 5 V. Figura 10: muestra el comportamiento del circuito para una señal de control de 3, 5 V. [0013] Las partes que se muestran en las figuras están numeradas individualmente y los términos correspondientes

a estos números son como sigue: Señal PWM (1) Tiempo tensión alta (Vcc) (2) Multiplexor (11) Salida analógica de la técnica anterior (12) Entradas de control de la técnica anterior (A, B, C)

Entradas analógicas de la técnica anterior (XO - X7)

Codificador binario para 1-de-8 con inhibición (21)

Convertidor de nivel (22)

Salida analógica de la técnica anterior (23)... [Seguir leyendo]

Reivindicaciones:

1. Sistema para selección de señal de entrada analógica para sistemas que tienen más de una señal de entrada analógica, para seleccionar la señal de entrada analógica requerida caracterizado porque comprende;

- un puerto de GPIO que tiene capacidad de salida de la señal PWM (32) ,

- un filtro paso bajo (R26, C22) que está conectado a dicho puerto de GPIO para obtener diferentes niveles analógicos para diferentes ciclos de trabajo de la señal PWM,

- transistores (Q1, Q2, Q3, Q7, Q8, Q9, Q10) para seleccionar la señal de entrada analógica requerida,

- resistencias (R8, R9, R10, R11, R15, R16, R17, R21, R23, R25) que están conectadas a la base de los transistores para ser utilizados como divisores de tensión para activar o desactivar los transistores de selección,

- diodos (D6, D7, D8, D9) para enviar la señal de entrada analógica seleccionada a una salida del sistema de selección de señal de entrada analógica.

2. Sistema según la reivindicación 1 caracterizado porque comprende además una fuente de PWM que está conectada a dicho un puerto de GPIO de dicho sistema para selección de señal de entrada analógica, para salida de una señal PWM (1) .

3. Sistema de acuerdo con la reivindicación 2 caracterizado porque dicha señal PWM (1) es utilizada como una entrada de control por dicho sistema para selección de señal de entrada analógica.

4. Procedimiento para selección de señal de entrada analógica para sistemas que tienen más de una señal de entrada analógica, para seleccionar la señal de entrada analógica requerida, caracterizado porque dicho procedimiento comprende las siguientes etapas de:

- conectar una fuente de PWM a un puerto de GPIO del sistema para selección de señal de entrada analógica de la reivindicación 1;

- enviar al sistema una señal PWM (1) de entrada que es generada por dicha fuente de PWM,

- ajustar un ciclo de trabajo de dicha señal PWM para conmutar transistores,

- activar o desactivar transistores de selección por medio de resistencias que están conectadas como divisores de tensión a la base de dichos transistores,

- enviar la señal de entrada analógica requerida seleccionada a una salida del sistema para selección de señal de entrada analógica.

5. Procedimiento según la reivindicación 4 caracterizado porque dichos transistores se conmutan mediante una entrada de control que se obtiene mediante la fuente PWM conectada.

6. Procedimiento según la reivindicación 4 caracterizado porque los diferentes valores de tensión continua se obtienen mediante el ajuste de dicho ciclo de trabajo de dicha señal PWM (1) .

7. Procedimiento según la reivindicación 4 caracterizado porque dichos valores de tensión continua se dividen por dichas resistencias para activar o desactivar dichos transistores de selección.

REFERENCIAS CITADAS EN LA DESCRIPCIÓN

La lista de referencias citada por el solicitante lo es solamente para utilidad del lector, no formando parte de los documentos de patente europeos. Aún cuando las referencias han sido cuidadosamente recopiladas, no pueden excluirse errores u omisiones y la OEP rechaza toda responsabilidad a este respecto.

Documentos de patente citados en la descripción

• EP 1970817 A [0004] • US 2006047866 A [0005]

• US 2006047866 A1 [0005] • KR 20040093890 A [0006]

Patentes similares o relacionadas:

Dispositivo electrónico y procedimiento de realización de comunicación híbrida con dispositivo electrónico externo, del 3 de Junio de 2020, de SAMSUNG ELECTRONICS CO., LTD.: Un dispositivo electrónico que comprende: un primer circuito de comunicación que realiza comunicación inalámbrica utilizando un primer protocolo de comunicación; […]

Módulo de interfaz física, del 13 de Mayo de 2020, de NAGRAVISION S.A.: Un sistema en chip (SYS) que comprende un primer módulo (PER) y un segundo módulo (PROC), el primer módulo (PER) que comprende una primera interfaz física […]

Procedimiento, dispositivo y sistema para transferencia de paquetes en NVME sobre tejido, del 22 de Abril de 2020, de HUAWEI TECHNOLOGIES CO., LTD.: Un dispositivo de transferencia y procesamiento en memoria no volátil exprés sobre tejido, NVMe sobre tejido, en el que el dispositivo […]

Dispositivo de conmutación, sistema de interconexión de componentes periféricos rápida y procedimiento de inicialización del mismo, del 13 de Noviembre de 2019, de HUAWEI TECHNOLOGIES CO., LTD.: Un dispositivo de conmutación que comprende: múltiples puertos de Interconexión de Componentes Periféricos rápidos, PCIe, aguas arriba , […]

Método de desconexión de enlace entre un equipo PCIe y un concentrador y dispositivo que utiliza este último, del 14 de Agosto de 2019, de HUAWEI TECHNOLOGIES CO., LTD.: Un método para desconectar un enlace entre un dispositivo de Interconexión de Componente Periférico Exprés, PCIe, y un concentrador, en donde el dispositivo […]

Método y sistema para poner dispositivos funcionales a disposición de participantes de reuniones, del 4 de Julio de 2019, de BARCO N.V.: 1. Un sistema para conectar un dispositivo de procesamiento a un dispositivo funcional conectado a, o en, una unidad base de una red de comunicaciones, teniendo el dispositivo […]

Interfaz serie de capa de enlace a capa física (PHY), del 21 de Marzo de 2019, de QUALCOMM INCORPORATED: Un circuito integrado, IC, que comprende: un circuito de capa de enlace ; un puente de enlace acoplado operativamente al […]

Sistema informático y procedimiento para acceder a un dispositivo de punto extremo del mismo, del 20 de Marzo de 2019, de HUAWEI TECHNOLOGIES CO., LTD.: Un sistema informático , que comprende un subsistema informático y un subsistema de gestión , en el que el subsistema informático comprende una unidad de […]