Oscilador MOS de alta frecuencia integrado.

Un circuito oscilador MOS de alta frecuencia (20) que comprende al menos un elemento activo (F1,

F2) y un circuito de determinación de frecuencia (L1, L2, C), en el que el al menos un elemento activo es un MOSFET con un electrodo de puerta (G), un electrodo de fuente (S) y un electrodo de drenaje (D),

caracterizado porque el circuito oscilador está también provisto de al menos una red de selección de frecuencia que comprende

- una resistencia de puerta parásita presente inherentemente en combinación con un condensador (C1, C2) dispuesto entre el electrodo de puerta y el electrodo de fuente, o

- una capacitancia de puerta-fuente parásita presente inherentemente en combinación con un resistor (R1, R2) conectado con el electrodo de puerta,

siendo la red de selección de frecuencia tal que la oscilación en la frecuencia de oscilador deseada puede tener lugar substancialmente atenuada, mientras que las oscilaciones a frecuencias de oscilación parásitas se han suprimido en el que a las frecuencias de oscilación parásitas la ganancia de bucle se reduce hasta un valor absoluto menor que 1.

Tipo: Patente Internacional (Tratado de Cooperación de Patentes). Resumen de patente/invención. Número de Solicitud: PCT/NL2001/000115.

Solicitante: TELEFONAKTIEBOLAGET LM ERICSSON (PUBL).

Nacionalidad solicitante: Suecia.

Dirección: 164 83 STOCKHOLM SUECIA.

Inventor/es: VAN ZEIJL, PAULUS, THOMAS, MARIA, TANGENBERG,Jurjen.

Fecha de Publicación: .

Clasificación Internacional de Patentes:

- H03K3/354 ELECTRICIDAD. › H03 CIRCUITOS ELECTRONICOS BASICOS. › H03K TECNICA DE IMPULSO (medida de las características de los impulsos G01R; modulación de oscilaciones sinusoidales por impulsos H03C; transmisión de información digital, H04L; circuitos discriminadores de detección de diferencia de fase entre dos señales de conteo o integración de ciclos de oscilación H03D 3/04; control automático, arranque, sincronización o estabilización de generadores de oscilaciones o de impulsos electrónicos donde el tipo de generador es irrelevante o esta sin especificar H03L; codificación, decodificación o conversión de código, en general H03M). › H03K 3/00 Circuitos para la generación de impulsos eléctricos; Circuitos monoestables, biestables o multiestables (H03K 4/00 tiene prioridad; para generadores de funciones digitales en ordenadores G06F 1/02). › Circuitos astables.

PDF original: ES-2379162_T3.pdf

Descripción:

Oscilador MOS de alta frecuencia integrado La invención se refiere a un circuito oscilador MOS de alta frecuencia integrado que comprende al menos un elemento activo y un circuito de determinación de frecuencia.

Tales circuitos osciladores son ya conocidos y se implementan típica aunque no necesariamente como circuitos equilibrados. Un ejemplo de tal circuito oscilador MOS implementado como un circuito equilibrado se describe en el documento IBM Technical Disclosure Bulletin Vol. 40, No. 10, de Octubre de 1997.

Los transistores MOS se aplican normalmente sobre todo en tecnología de circuitos de control y determinación tales como procesadores y memorias. En este tipo de circuitos, miniaturización, tasa de reloj y precio de coste son los aspectos claves más importantes. El interés de estos aspectos claves ha llevado también a que los transistores MOS se hayan vuelto cada vez más útiles para circuitos de muy alta frecuencia tales como osciladores que trabajan bien dentro del intervalo de los Gigahercios. El transistor MOS, cuyo rendimiento en el área de procesamiento de señales de alta frecuencia hasta hace poco era considerablemente más pobre que el del transistor bipolar convencional, ahora tiene propiedades comparables, pero con menos área superficial utilizada, lo que mejora la miniaturización. Además, el bajo precio de coste es una ventaja.

Un problema que aparece en los osciladores de alta frecuencia integrados modernos construidos con transistores MOS, no obstante es la existencia de fuertes resonancias parásitas en una o incluso en más frecuencias como resultado de impedancias reactivas parásitas. Estas resonancias parásitas pueden estar muy por encima de la frecuencia de oscilador pretendida, por ejemplo en el intervalo de 50 a 60 GHz. Existe el peligro de que el circuito oscilador empiece a oscilar a estas frecuencias más altas, lo que es altamente indeseable.

De acuerdo con esto, existe la necesidad de un circuito oscilador de alta frecuencia mejorado que no tenga ninguna frecuencia de oscilación parásita y que pueda ser construido utilizando elementos MOS, aún manteniendo substancialmente las buenas propiedades de la técnica de MOS.

El objeto de la invención es proporcionar una solución para la necesidad indicada y de manera general proporcionar un circuito oscilador MOS fiable que no muestre ninguna o substancialmente ninguna oscilación parásita. Para ese fin, de acuerdo con la invención, un circuito oscilador del tipo descrito anteriormente está caracterizado porque el circuito oscilador está provisto también de al menos una red de selección de frecuencias, que está construida a partir de uno o más resistores y de uno o más elementos reactivos, de manera que la oscilación en la frecuencia del oscilador deseada tenga lugar substancialmente atenuada, mientras que las oscilaciones en frecuencias de oscilación parásitas son suprimidas, en el que a las frecuencias de oscilación parásitas la ganancia de bucle se reduce hasta un valor absoluto menor que 1.

En lo que sigue, la invención se describe también con referencia a los dibujos adjuntos.

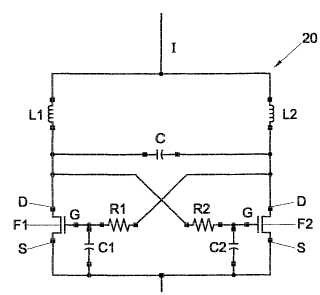

La Fig. 1 muestra esquemáticamente un ejemplo de un circuito oscilador conocido; y la Fig. 2 muestra esquemáticamente un ejemplo de un circuito oscilador de acuerdo con la invención.

La Fig. 1 muestra esquemáticamente un ejemplo de un circuito oscilador de alta frecuencia integrado 1, en este caso implementado como un circuito equilibrado. El circuito oscilador mostrado está construido utilizando elementos MOS activos F1 y F2 que han sido formados en un único microprocesador. En este ejemplo, los elementos F1 y F2 son del tipo FET y cada uno tiene tres electrodos de conexión designados D (drenaje (drain, en inglés) ) , S (fuente (source, en inglés) ) y G (puerta (gate, en inglés) ) . Los dos electrodos de fuente están conectados entre sí. Los electrodos de puerta y de drenaje de los dos elementos F1 y F2 están conectados entrecruzados entre sí, de tal manera que el electrodo de puerta del elemento F1 está conectado, por medio de un conductor 2 proporcionado en el microprocesador, con el electrodo de drenaje del otro elemento F2. De manera similar, el electrodo de puerta del elemento F2 está conectado por medio de un conductor 3 con el electrodo de drenaje del elemento F1.

Además, los dos electrodos de drenaje están conectados entre sí a través de un condensador C formado en el microprocesador, por ejemplo un varactor. Cada uno de los electrodos de drenaje, finalmente, está conectado con el extremo de una bobina L1 y L2 asociadas, respectivamente, formadas en el microprocesador, estando los otros extremos de las bobinas L1 y L2 conectados entre sí y, directa o indirectamente, con una fuente de alimentación, en este ejemplo una fuente de alimentación I.

Debe observarse que la invención que va a describirse a continuación en esta memoria puede ser aplicada tanto en configuraciones de un único extremo como en configuraciones equilibradas. Una ventaja de la utilización de una configuración equilibrada como la mostrada es que tienen lugar en ella señales de fase opuesta. Como resultado, la inyección de señales de oscilador en el substrato o la recogida de señales de ruido del substrato se suprimen.

En los circuitos osciladores del tipo descrito anteriormente, como resultado de impedancias parásitas en la bobina L1, L2 y/o en el condensador C, pueden aparecer fuertes fenómenos de oscilación parásita en frecuencias muy por 2

encima de la frecuencia de oscilación pretendida. Dependiendo de la estructura específica, esto puede incluso implicar varios intervalos de resonancia parásitos. Tales intervalos de resonancia parásitos son altamente indeseables porque como resultado de ellos el oscilador no funciona de la manera pretendida.

La Fig. 2 muestra esquemáticamente un ejemplo de un circuito oscilador 20 de acuerdo con la invención. En la Fig. 2, elementos correspondientes se indican con los mismos símbolos de referencia que en la Fig. 1. El circuito mostrado en la Fig. 2 difiere del de la Fig. 1 en que los electrodos de puerta no están conectados con los electrodos de drenaje de los otros elementos activos directamente, sino a través de un resistor R1 y R2, respectivamente. Además, los electrodos de puerta están cada uno conectados a través de un condensador C1 y C2, respectivamente, al electrodo de puerta asociado y por ello en este ejemplo están también conectados con la tierra. En realidad, entre el electrodo de puerta de un elemento y el electrodo de drenaje del otro elemento está conectada una red RC respectiva. La red RC forma un filtro de paso bajo de primer orden, lo que hace que la ganancia de bucle descienda a medida que aumenta la frecuencia. El polo de la red RC se elige de manera que la oscilación en la frecuencia deseada no resulte influenciada, pero se evite la oscilación parásita a frecuencias más altas.

Debe observarse que no siempre es necesario proporcionar especialmente un elemento resistivo y/o capacitivo. En algunos casos, dependiendo del diseño del circuito, puede ser posible utilizar una resistencia de puerta parásita inherentemente presente y/o una capacitancia de puerta-fuente parásita inherentemente presente, sola o en combinación con un resistor o un condensador adicional. El uso de una parte adicional del material de la puerta como resistencia también es posible. Para este fin, el elemento MOS puede ser de manera opcional deliberadamente diseñado con una arquitectura especial.

Además, es posible utilizar redes de selección de frecuencia estructuradas de manera diferente, que están incluidas en las conexiones de la puerta, siempre que la ganancia del bucle se reduzca lo menos posible a la frecuencia de oscilación deseada y, a la inversa, hasta un nivel suficiente a las frecuencias parásitas. Tal red de selección de frecuencias, si se desea, comprende una o más bobinas pero, a la vista de las dimensiones de las bobinas, es preferible construir sólo a partir de elementos resistivos y de elementos capacitivos. El circuito mostrado en la Fig. 2 puede ser también realizado utilizando elementos PMOS, además de elementos NMOS.

Reivindicaciones:

1. Un circuito oscilador MOS de alta frecuencia (20) que comprende al menos un elemento activo (F1, F2) y un circuito de determinación de frecuencia (L1, L2, C) , en el que el al menos un elemento activo es un MOSFET con un electrodo de puerta (G) , un electrodo de fuente (S) y un electrodo de drenaje (D) , caracterizado porque el circuito oscilador está también provisto de al menos una red de selección de frecuencia que comprende

- una resistencia de puerta parásita presente inherentemente en combinación con un condensador (C1, C2) dispuesto entre el electrodo de puerta y el electrodo de fuente, o

- una capacitancia de puerta-fuente parásita presente inherentemente en combinación con un resistor (R1, R2) conectado con el electrodo de puerta,

siendo la red de selección de frecuencia tal que la oscilación en la frecuencia de oscilador deseada puede tener lugar substancialmente atenuada, mientras que las oscilaciones a frecuencias de oscilación parásitas se han suprimido en el que a las frecuencias de oscilación parásitas la ganancia de bucle se reduce hasta un valor absoluto menor que 1.

2. Un circuito oscilador de acuerdo con la reivindicación 1, caracterizado porque la al menos una red de selección de frecuencia comprende una red RC.

3. Un circuito oscilador de acuerdo con una cualquiera de las reivindicaciones precedentes, implementado como un circuito equilibrado con conexiones entrecruzadas entre un electrodo de puerta y un elemento activo y el electrodo de drenaje del otro elemento activo, mientras que un circuito de selección de frecuencia respectivo está conectado entre el electrodo de puerta y un elemento activo y el electrodo de drenaje del otro elemento activo.

4. Un circuito oscilador de acuerdo con una cualquiera de las reivindicaciones precedentes, caracterizado porque los componentes de la red de selección de frecuencia están formados mediante una arquitectura especial del MOSFET.

5. Un circuito oscilador de acuerdo con una cualquiera de las reivindicaciones precedentes, que comprende una parte adicional del material de puerta como resistencia.

Patentes similares o relacionadas:

DISPOSICION DE CIRCUITO PARA LA GENERACION DE IMPULSOS RECTANGULARES., del 16 de Mayo de 2006, de ROBERT BOSCH GMBH: Disposición de circuito para la generación de impulsos rectangulares, con un Flip-Flop activado por los flancos y con al menos un comparador , cuya salida está conectada […]

LINEA DE RETARDO VARIABLE DE GAMA ANCHA Y OSCILADOR DE ANILLO, del 16 de Agosto de 1997, de AT&T CORP.: UNA LINEA DE RETARDO VARIABLE QUE TIENE UNA SERIE DE INVERSORES LOGICOS "LENTOS" Y UN NUMERO IGUAL DE INVERSORES "RAPIDOS" CON ENTRADAS CONECTADAS PARA […]

OSCILADOR DE TECNICA CMOS, del 16 de Febrero de 1995, de ALCATEL SEL AKTIENGESELLSCHAFT ALCATEL N.V.: LA TAREA CONSISTE EN REALIZAR UN OSCILADOR DE TECNICA CMOS PARA FRECUENCIAS TANTO MUY BAJAS COMO MUY ALTAS, POR EJEMPLO DE MAS DE 100 MHZ. EL […]

PROCEDIMIENTO Y DISPOSITIVO DE RECUPERACION DE RELOJ, del 1 de Mayo de 2008, de CENTRE NATIONAL D'ETUDES SPATIALES (C.N.E.S.) ETABLISSEMENT PUBLIC, SCIENTIFIQUE ET: Procedimiento de transmisión de datos digitales en un enlace serie en banda base según una frecuencia nominal fn superior a 500 MHz entre un emisor […]

PROCEDIMIENTO Y DISPOSITIVO DE RECUPERACION DE RELOJ, del 1 de Mayo de 2008, de CENTRE NATIONAL D'ETUDES SPATIALES (C.N.E.S.) ETABLISSEMENT PUBLIC, SCIENTIFIQUE ET: Procedimiento de transmisión de datos digitales en un enlace serie en banda base según una frecuencia nominal fn superior a 500 MHz entre un emisor […]