Nodo de red, dispositivo de memoria intermedia y el método de programación.

Un dispositivo de memoria intermedia (304) , caracterizado porque comprende al menos dos unidades de conmutación interna (401,

501) y al menos dos unidades de memorias intermedias básicas (402, 502) , en donde cada una de las al menos dos unidades de conmutación interna (401, 501) comprende al menos dos entradas y al menos dos salidas, las al menos dos unidades de conmutación interna (401, 501) y las al menos dos unidades de memorias intermedias básicas (402, 502) forman una conexión cerrada;

en donde las al menos dos unidades de conmutación interna (401, 501) y las al menos dos unidades de memorias intermedias básicas (402, 502) forman la conexión alternándose entre sí, en donde cada de las al menos dos unidades de conmutación interna (401, 501) se conecta con una unidad de memoria intermedia básica, en sentido ascendente, por intermedio de una de las al menos dos entradas y se conecta con una unidad de memoria intermedia básica, en sentido descendente, por intermedio de una de las al menos dos salidas;

otra de las al menos dos entradas de cada una de las al menos dos unidades de conmutación interna (401, 501) recibe una onda luminosa, cada una de las al menos dos unidades de conmutación interna (401, 501) proporciona a la salida la onda luminosa a la unidad de memoria intermedia básica, en sentido descendente, o proporciona a la salida la onda luminosa a un combinador desde otra de las al menos dos salidas en función de una primera señal de control;

y las al menos dos unidades de memorias intermedias básicas (402, 502) están adaptadas para la memorización intermedia de la onda luminosa a partir de las unidades de conmutación interna.

Tipo: Patente Internacional (Tratado de Cooperación de Patentes). Resumen de patente/invención. Número de Solicitud: PCT/CN2007/070737.

Solicitante: HUAWEI TECHNOLOGIES CO., LTD..

Nacionalidad solicitante: China.

Dirección: HUAWEI ADMINISTRATION BUILDING BANTIAN LONGGANG DISTRICT SHENZHEN, GUANGDONG PROVINCE 518129 CHINA.

Inventor/es: ZHANG, YI, WANG,Sheng, PAN,Yongkang, SU,Qingbo, XU,Du.

Fecha de Publicación: .

Clasificación Internacional de Patentes:

- H04J14/02 ELECTRICIDAD. › H04 TECNICA DE LAS COMUNICACIONES ELECTRICAS. › H04J COMUNICACIONES MULTIPLEX (peculiar de la transmisión de información digital H04L 5/00; sistemas para transmitir las señales de televisión simultánea o secuencialmente H04N 7/08; en las centrales H04Q 11/00). › H04J 14/00 que utiliza sensores de imagen de estado sólido. › Sistemas múltiplex de división de longitud de onda.

PDF original: ES-2377216_T3.pdf

Fragmento de la descripción:

Nodo de red, dispositivo de memoria intermedia y el método de programación CAMPO DE LA TECNOLOGÍA

La presente invención se refiere al campo de la tecnología de redes ópticas y más en particular a un nodo de red, un dispositivo de memoria intermedia y un método de programación en una red óptica de conmutación de paquetes.

ANTECEDENTES DE LA INVENCIÓN

Con el rápido crecimiento de los servicios de paquetes, el diseño de las redes de comunicaciones, en el futuro, tendrá como objetivo principal la optimización y soporte de paquetes. La tecnología de la conmutación de paquetes de redes ópticas es capaz de ampliar el ancho de banda de red existente y un nodo de red tiene un alto rendimiento de suministro de información, lo que es idóneo para servir de apoyo a un servicio de paquetes que suele cambiar y es muy imprevisto desde el punto de vista operativo, en particular en un servicio de IP.

Actualmente, una red óptica de conmutación de paquetes suele estar constituida por nodos de borde y un nodo central conectado mediante un enlace de fibra de multiplexión por división en longitud de onda densas (DWDM) . Un paquete de datos se transmite desde un nodo de borde por intermedio del enlace de fibra de DWDM hasta llegar al nodo central, luego se conmuta mediante un módulo de conmutación del nodo central y por último, se envía a un nodo de borde de destino.

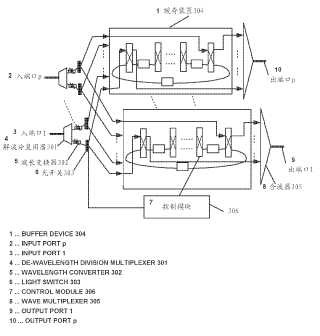

La Figura 1 representa un diagrama de un sistema de conexiones de realimentación de una estructura de nodo central. La estructura tiene P puertos de entrada que están en correspondencia con P puertos de salida, presentando cada puerto M longitudes de onda y utilizando una matriz de conmutación de una escala de PM x PM. Es decir, la matriz de conmutación incluye PM puertos de entrada y PM puertos de salida. Se realiza una conversión de longitudes de onda por intermedio de un convertidor de longitudes de onda sintonizable (TWC) sobre una salida de una onda luminosa desde un demultiplexor por división en longitud de onda en el sistema de conexión y luego, la onda luminosa entra en una memoria intermedia óptica. La onda luminosa, procedente de la memoria intermedia óptica, entra en un combinador de un puerto de salida correspondiente a través de la matriz de conmutación de la escala de PM x PM. Una estructura de la memoria intermedia óptica se representa en la Figura 2, en la que cada línea de retardo de fibra de la unidad de memoria intermedia multinivel (FDL) consiste en cuatro líneas Fels de un solo nivel FDLs.

El sistema de conexión de realimentación presenta los inconvenientes siguientes. Puesto que una línea FDL multinivel dedicada está configurada para cada longitud de onda, se necesita un gran número de FDLs, por lo que la escala del nodo central es grande. Además, se utiliza una estructura de matriz de conmutación de un solo plano, es decir, una estructura de matriz de conmutación de la escala de PM x PM y dicha matriz de conmutación está constituida por conmutadores. Si el conmutador se representa por un conmutador óptico básico de tipo 1 x 2, el número de conmutadores ópticos básicos, que se necesitan, es 2 x PM (PM -1) . En consecuencia, el nodo central presenta una escala todavía mayor y resulta difícil ponerla en práctica en una forma integrada. Puesto que la memoria intermedia óptica utiliza una estructura de conexión lineal, el número de las líneas FDLs está limitado y existe un límite superior de tiempo de memoria intermedia. Cuando el tiempo de memoria intermedia requerido por el paquete de datos supera el límite superior, sólo se puede desechar el paquete de datos. Puesto que la memoria intermedia óptica utilizada está antes del plano de conmutación, existe el problema del bloqueo de la cabecera de línea. Esto es, para dos datos en ráfaga, que tengan la misma longitud de onda, procedentes sucesivamente del mismo puerto de entrada, llegando en diferentes puertos de salida, si los anteriores datos en ráfaga se retardan en la memoria intermedia óptica en un tiempo que se solapa con el tiempo cuando los últimos datos en ráfaga salen de la memoria intermedia óptica, se desecharán inevitablemente dichos últimos datos en ráfaga en la situación de que realmente el plano de conmutación está inactivo y no se puede enviar al puerto de salida correspondiente.

Además, SHELL M. et al: "Rendimiento de las redes, completamente ópticas, de conmutadores de paquetes de arquitectura de memoria compartida utilizando un agrupamiento de canales bajo un tráfico en ráfagas" HIGH PERFORMANCE SWITCHING AND ROUTING, 2001 IEEE WORKSHOP ON 29-31 MAYO 2001, PISCATAWAY, NJ, USA, IEEE, 29 mayo 2001 (2001-05-29) , páginas 208-212, XP010542800 ISBN:978-0-2803-6711-1 presenta un modelo de operación lógica exacto para predecir el rendimiento de la clase de arquitectura de de memoria compartida, completamente óptica, con conmutadores de paquetes, bajo un tráfico aleatorio o en ráfagas. El modelo da a conocer, además, un medio para obtener una aproximación razonable del comportamiento funcional de elementos de conmutadores de OSMA dentro de algunos tipos de redes, incluyendo la familia de Banyan.

KOJI SASAYAMA et al: "FRONTIERNET: Red de Interconexión por división en el tiempo del tipo de encaminamiento de frecuencias" JOURNAL OF LIGHTWAVE TECHNOLOGY, IEEE SERVICE CENTER, NEW YORK, NY, US, vol.15, nº 3, 1 marzo 1997 (1997-03-01) , XP011028790 ISSN: 0733-8724 describe un conmutador de ruta de multiplexión por división en tiempo (TDM) fotónica, denominado FRONTIERNET, que utiliza la frecuencia óptica como medio de encaminamiento de la información. Esta arquitectura de conmutadores se puede aplicar a sistemas de conmutación del modo de transferencia asíncrona (ATM) . El conmutador N x N consiste en N convertidores de frecuencias sintonizables y N memorias intermedias de salida multiplexadas por división en frecuencias (FDM) conectadas mediante un enrutador de frecuencias N x N. El enrutador puede interconectar N rutas de entrada con N rutas de salida en un modo completamente sin interferencias. Es posible direccionar cada ruta de salida, de forma única, mediante la elección de frecuencia (enrutamiento de frecuencias) y cada ruta de salida puede recibir cualquier frecuencia dada desde solamente una entrada.

EP-A-1 217 863 (ALCATEL USA SOURCING LP [US]) 26 Junio 2002 (2002-06-26) da a conocer una red de conmutadores ópticos que incluye enrutadores ópticos, que encaminan la información de rutas en fibras ópticas. Cada fibra transporta una pluralidad de canales de datos, colectivamente denominados un grupo de canales de datos y un canal de control. Los datos se transmiten en los canales de datos en forma de ráfagas de datos y la información de control se transmite a través del canal de control en paquetes de cabeceras de ráfagas. Un paquete de cabeceras de ráfagas incluye información de enrutamiento para una ráfaga de datos asociada y precede a su ráfaga de datos asociada. La programación en paralelo, con múltiples retardos, se puede utilizar para una programación más rápida. En una forma de realización, tiempos e intervalos de separación no programados se pueden procesar en una memoria unificada para un funcionamiento más eficaz.

US 2004/208418 A1 (HANDELMAN DORON [IL]) 21 octubre 2004 (2004-10-21) da a conocer un método en el que una señal óptica retardada se genera a partir de una señal óptica a la entrada mediante la transmisión cíclica de la señal óptica introducida entre al menos dos extremos de un medio de soporte óptico y proporcionando a la salida, la señal óptica a la entrada desde uno de los extremos del medio de soporte óptico después de al menos un ciclo de transmisión a través del medio óptico. Cada transmisión de la señal óptica a la entrada, en una dirección a través del medio de soporte óptico, se transmite por intermedio de un recurso de longitud de onda que es diferente de un recurso de longitud de onda utilizado en una transmisión precedente de la señal óptica entrante en una dirección a través del medio de soporte óptico.

SUMARIO DE LA INVENCIÓN

Las formas de realización de la presente invención están destinadas a un nodo de red, un dispositivo de memoria intermedia y un método de programación, con el fin de reducir la escala de un nodo central y diseñar un nodo central práctico.

Para poder resolver el problema técnico anterior, el objetivo de las formas de realización de la presente invención se realiza por intermedio de los sistemas técnicos siguientes.

Se da a conocer un dispositivo de memoria intermedia. El dispositivo de memoria intermedia... [Seguir leyendo]

Reivindicaciones:

1. Un dispositivo de memoria intermedia (304) , caracterizado porque comprende al menos dos unidades de conmutación interna (401, 501) y al menos dos unidades de memorias intermedias básicas (402, 502) , en donde cada una de las al menos dos unidades de conmutación interna (401, 501) comprende al menos dos entradas y al menos dos salidas, las al menos dos unidades de conmutación interna (401, 501) y las al menos dos unidades de memorias intermedias básicas (402, 502) forman una conexión cerrada;

en donde las al menos dos unidades de conmutación interna (401, 501) y las al menos dos unidades de memorias intermedias básicas (402, 502) forman la conexión alternándose entre sí, en donde cada de las al menos dos unidades de conmutación interna (401, 501) se conecta con una unidad de memoria intermedia básica, en sentido ascendente, por intermedio de una de las al menos dos entradas y se conecta con una unidad de memoria intermedia básica, en sentido descendente, por intermedio de una de las al menos dos salidas;

otra de las al menos dos entradas de cada una de las al menos dos unidades de conmutación interna (401, 501) recibe una onda luminosa, cada una de las al menos dos unidades de conmutación interna (401, 501) proporciona a la salida la onda luminosa a la unidad de memoria intermedia básica, en sentido descendente, o proporciona a la salida la onda luminosa a un combinador desde otra de las al menos dos salidas en función de una primera señal de control;

y las al menos dos unidades de memorias intermedias básicas (402, 502) están adaptadas para la memorización intermedia de la onda luminosa a partir de las unidades de conmutación interna.

2. El dispositivo de memoria intermedia según la reivindicación 1, en donde cada una de las al menos dos unidades de conmutación interna (401, 501) comprende tres o más entradas y tres o más salidas, estando las al menos dos unidades de conmutación interna (401, 501) concatenadas para formar una conexión cerrada por ellas mismas.

3. Un nodo de red, que comprende un demultiplexor por división en longitud de onda (301) , al menos un dispositivo de memoria intermedia (304) según la reivindicación 1 y al menos un combinador (305) , en donde:

el demultiplexor por división en longitud de onda (301) , adaptado para dividir una señal de onda luminosa recibida y proporcionar, a su salida, una onda luminosa, obtenida por división, al por lo menos un dispositivo de memoria intermedia (304) ;

el al menos un combinador (305) , de tipo uno a uno, correspondiente al por lo menos un dispositivo de memoria intermedia (304) , adaptado para multiplexar y proporcionar, a la salida, la onda luminosa procedente de la unidad de conmutación interna del dispositivo de memoria intermedia.

4. El nodo de red según la reivindicación 3, en donde entre el demultiplexor por división en longitud de onda y el dispositivo de memoria intermedia, el nodo de red comprende, además:

un convertidor de longitud de onda sintonizable (302) , adaptado para realizar una conversión de longitud de onda sobre la salida de onda luminosa desde el demultiplexor por división en longitud de onda y para proporcionar, a la salida, una onda luminosa convertida al dispositivo de memoria intermedia.

5. El nodo de red según la reivindicación 4, en donde entre el convertidor de longitud de onda sintonizable y el dispositivo de memoria intermedia, el nodo de red comprende, además:

un conmutador óptico (303) , adaptado para transmitir la salida de onda luminosa procedente del convertidor de longitud de onda sintonizable al dispositivo de memoria intermedia en función de una segunda señal de control.

6. El nodo de red según la reivindicación 3 o 5, en donde cada una de las al menos dos unidades de conmutación interna comprende tres o más entradas y tres o más salidas, las al menos dos unidades de conmutación interna están concatenadas para formar una conexión cerrada por ellas mismas.

7. Un método de programación para transmitir un paquete de datos en una red óptica, incluyendo la red óptica un dispositivo de memoria intermedia según la reivindicación 1 o 2, cuyo método comprende:

la determinación de una ruta en función de un nivel de utilización (603) y la determinación de si cada una de las unidades de memorias intermedias básicas es capaz de reservarse en función de la información del estado operativo del puerto de salida de una unidad de conmutación interna, en sentido ascendente, para cada una de las unidades de memorias intermedias básicas en la ruta (604) ; la determinación de si un primer puerto de una unidad de conmutación interna, conectado a una salida de una última unidad de memoria intermedia básica, es capaz de reservarse en función de la información del estado operativo del puerto de salida de la unidad de conmutación interna conectado a la salida de la última unidad de memoria intermedia básica en la ruta, si cada una de las unidades de memorias intermedias básicas es capaz de reservarse (605) y la transmisión del paquete de datos a través de la ruta y la actualización de la información del estado operativo del puerto de salida de cada una de las unidades de conmutación interna en la ruta, si el primer puerto de la unidad de conmutación interna conectado a la salida de la última unidad de memoria intermedia básica es capaz de reservarse (606) .

8. El método de programación según la reivindicación 7, que comprende además:

la determinación de si un nivel m de una unidad de memoria intermedia básica, que actualmente tiene éxito operativo en la reserva, es menor que el nivel de utilización;

la determinación de si un segundo puerto de una unidad de conmutación interna de nivel (n+1) -ésimo conectado a una unidad de memoria intermedia básica, en sentido descendente, es capaz de reservarse en función de la información del estado operativo del puerto de salida de la unidad de conmutación interna de nivel (n+1) -ésimo conectada a una salida de una unidad de memoria intermedia básica de nivel m-ésimo en la ruta si el nivel m de la unidad de memoria intermedia básica, que actualmente tiene éxito operativo en reserva, es menor que el nivel de utilización y el incremento de m en 1, el incremento de un nivel n, de unidades de conmutación interna que han sido utilizadas, en 1 y la continuación de la determinación de si el nivel m de la unidad de memoria intermedia básica, que actualmente tiene éxito operativo en la reserva, es menor que el nivel de utilización si el segundo puerto de la unidad de de conmutación interna de nivel (n+1) -ésimo conectado a la unidad de memoria intermedia básica, en sentido descendente, es capaz de reservarse y la determinación de si un primer puerto de una unidad de conmutación interna de nivel (n+1) -ésimo es capaz de reservarse en función de la información del estado operativo del puerto de salida de la unidad de conmutación interna de nivel (n+1) -ésimo conectada a la salida de una unidad de memoria intermedia básica de nivel m-ésimo en la ruta si el nivel m de la unidad de memoria intermedia básica, que actualmente tiene éxito operativo en la reserva, no es menor que el nivel de utilización y de proporcionar, a la salida, el paquete de datos desde el primer puerto de la unidad de conmutación interna de nivel (n+1) -ésimo a través de la ruta y la actualización de la información del estado operativo del puerto de salida de cada una de las unidades de conmutación interna en la ruta si el primer puerto de la unidad de conmutación interna de nivel (n+1) -ésimo es capaz de reservarse;

en donde la variable m representa el nivel de la unidad de memoria intermedia básica, que actualmente tiene éxito operativo en la reserva, y se asigna un valor inicial de 0 y la variable n representa un número de las unidades de conmutación interna que se han utilizado y se asigna un valor inicial de 0.

9. El método de programación según la reivindicación 8, en donde la unidad de conmutación interna es un conmutador óptico 3 x 3 y el método comprende, además:

la determinación de si un tercer puerto de la unidad de conmutación interna de nivel (n+1) -ésimo conectado a la unidad de conmutación interna, en sentido descendente, es capaz de reservarse en función de la información del estado operativo del puerto de salida de la unidad de conmutación interna de nivel (n+1) -ésimo cuando el segundo puerto de la unidad de conmutación interna de nivel (n+1) -ésimo conectado a la unidad de memoria intermedia básica, en sentido descendente, no es capaz de reservarse e incrementar n en 1 y la continuación de la determinación de si el segundo puerto de la unidad de conmutación interna de nivel (n+1) -ésimo conectado a la unidad de memoria intermedia básica, en sentido descendente, es capaz de reservarse si el tercer puerto de la unidad de conmutación interna de nivel (n+1) -ésimo conectado a la unidad de conmutación interna, en sentido descendente, es capaz de reservarse.

10. El método de programación según la reivindicación 9, que comprende, además:

el registro de que el segundo puerto de la unidad de conmutación interna de nivel (n+1) -ésimo se requiere cuando el segundo puerto de la unidad de conmutación interna de nivel (n+1) -ésimo conectado a la unidad de memoria intermedia básica, en sentido descendente, es capaz de reservarse; el registro de que el tercer puerto de la unidad de conmutación interna de nivel (n+1) -ésimo se requiere cuando el tercer puerto de la unidad de conmutación interna de nivel (n+1) -ésimo es capaz de reservarse; la determinación de si un tercer puerto de una unidad de conmutación interna de nivel n-ésimo se requiere cuando ni el segundo puerto ni el tercer puerto de la unidad de conmutación interna de nivel (n+1) -ésimo es capaz de reservarse; la reducción de m en 1, la reducción de n en 1 yla continuación de la determinación de si el tercer puerto de la unidad de conmutación interna de nivel (n+1) -ésimo conectado a la unidad de conmutación interna, sentido descendente, es capaz de reservarse, si no se requiere el tercer puerto de la unidad de conmutación interna de nivel n-ésimo y la reducción de n en 1 y la continuación de la determinación de si se requiere el tercer puerto de la unidad de conmutación interna, si se solicita el tercer puerto de la unidad de conmutación interna de nivel n-ésimo.

11. El método de programación según la reivindicación 10, en donde antes de determinar si el nivel m de la unidad de memoria intermedia básica, que actualmente tiene éxito operativo en la reserva, es menor que el nivel de utilización, el método comprende, además: la determinación de si n es mayor que una profundidad de ciclo máximo

preestablecida y la continuación del método si n no es mayor que la profundidad de ciclo máximo preestablecida.

12. El método de programación según la reivindicación 7, 8, 9, 10 o 11, en donde:

antes de determinar la ruta en función del nivel de utilización, el método comprende, además, la adquisición de la información del estado operativo de la longitud de onda, dependiendo del paquete de datos y el cálculo de un nivel de utilización de la unidad de memoria intermedia básica en función de la información del estado operativo de la longitud de onda y cuando se determina que el primer puerto de la unidad de conmutación interna, conectado a la salida de la última unidad de memoria intermedia básica es capaz de reservarse, el método comprende, además:

la actualización de la información del estado operativo de la longitud de onda.

Memoria intermedia Demultiplexor por división TWC Plano de conmutación

óptica

en longitud de onda Combinador

Puerto de entrada 1 Puerto de salida 1

Puerto de entrada 2 Puerto de salida 2

Puerto de entrada p Puerto de salida p

Figura 1

Figura 2

Dispositivo memoria intermedia 304 Puerto de entrada p

Puerto de entrada 1

Demultiplexor por división en longitud de onda Puerto de salida 1

Combinador 305

Figura 3

Longitud de onda luminosa entrada Puerto de salida Figura 4 Unidad conmutación interna 501

Longitud de onda luminosa entrada Puerto de salida Figura 5

Obtener información reenvío paquetes de datos Consultar una tabla de estados de longitud de onda en función del puerto de salida y calcular un número de niveles de uso d de la BMU

Determinar una ruta P en función de d

ÂEs capaz de reservarse cada una de las unidades de memoria intermedia básicas en la ruta P?

ÂEs capaz de reservarse una unidad de conmutación interna conectada a una salida de una última unidad de memoria intermedia básica en la ruta P?

Reservar todos los recursos satisfactoriamente, actualizar la tabla de estados de longitud de onda y las tablas de estados de puertos de salida correspondientes a todas las unidades de conmutación interna en la ruta P y transmitir los paquetes de datos al puerto de salida Figura 6

Falla la reserva de recursos y se registra que se pierde el paquete de datos Obtener información reenvío paquete de datos Consultar una tabla de estados de longitud de onda en función del puerto de salida y calcular un número de niveles de uso d de la BMU y determinar una ruta P

Se supone que un puerto de una unidad de conmutación interna 2x2 conectado a un combinador es un primer puerto, un puerto conectado a un “anillo de BMU” es un segundo puerto y se supone que m es un número de niveles de la BMU, que actualmente tiene éxito operativo en la reserva y varios de niveles de uso de la unidad de conmutación interna y tiene un valor inicial de 0 y MAXDepth es una profundidad de ciclo máximo preestablecida Incrementar m en 1

ÂEstá inactivo un segundo puerto de una unidad de conmutación interna de nivel (m+1) -ésimo?

Falla la función de reserva y se registra que se pierde el paquete de datos

Figura 7

ÂEstá inactivo un primer puerto de una unidad de conmutación interna de nivel (m+1) -ésimo?

Reservar todos los recursos satisfactoriamente, actualizar la tabla de estados de longitud de onda y las tablas de estados de puertos de salida correspondientes a todas las unidades de conmutación interna en la ruta P y transmitir los paquetes de datos al puerto de salida Obtener información reenvío paquete de datos Consultar una tabla de estados de longitud de onda en función del puerto de salida y calcular un número de niveles de uso d de la BMU y determinar una ruta P

Se supone que un puerto de una unidad de conmutación interna 3x3 conectado a un combinador es un primer puerto, un puerto conectado a un “anillo de BMU” es un segundo puerto y un puerto conectado a un “anillo no de BMU” es un tercer puerto, se supone que m es un número de niveles de la BMU, que actualmente tiene éxito operativo en la reserva y tiene un valor inicial de 0. MAXDepth es una profundidad de ciclo máximo y n es un número de niveles de unidades de conmutación interna que se han utilizado y tiene un valor inicial de 0 ÂEstá inactivo un primer puerto de una unidad de conmutación interna de nivel (m+1) -ésimo?

Reservar todos los recursos satisfactoriamente, actualizar la tabla de estados de longitud de onda y las tablas de estados de puertos de salida correspondientes a todas las unidades de conmutación interna en la ruta P y transmitir los paquetes de datos al puerto de salida Incrementar n en 1 e incrementar m en 1

Incrementar n en 1

Falla la función de reserva y se registra que se pierde el paquete de datos m<d ÂEstá inactivo un segundo puerto de una unidad de conmutación interna de nivel (n+1) -ésimo?

ÂEstá inactivo un tercer puerto de una unidad de conmutación interna de nivel (n+1) -ésimo?

m<d Reducir n en 1

Sí

ÂSe ha solicitado un tercer puerto de una unidad de conmutación interna de nivel nésimo?

Reducir m en 1 y reducir n en 1

Figura 8

Patentes similares o relacionadas:

Procedimiento y dispositivo de ecualización de potencia óptica, del 24 de Junio de 2020, de HUAWEI TECHNOLOGIES CO., LTD.: Un procedimiento de equilibrio de potencia óptica, donde el procedimiento se aplica a un dispositivo transversal óptico que se basa en un cristal líquido sobre silicio, […]

Generador de luz roja de banda ancha para pantalla RGB, del 6 de Mayo de 2020, de IPG Photonics Corporation: Un generador de luz roja de línea ancha para una pantalla RGB, que comprende: una sola fuente de bomba láser de fibra Yb de pulso de […]

Método y aparato para establecer una relación de vinculación de enlace entre capas, del 15 de Abril de 2020, de HUAWEI TECHNOLOGIES CO., LTD.: Un método para establecer una relación de vinculación de enlace entre capas, que comprende: la recepción , por un primer nodo, de un mensaje […]

Dispositivo de red, del 12 de Febrero de 2020, de DEUTSCHE TELEKOM AG: Dispositivo de red para modular una pluralidad de señales de abonado de red, que están asignadas a diferentes abonados de red, según el esquema de modulación […]

Método y dispositivo de control de longitud de onda, del 8 de Enero de 2020, de HUAWEI TECHNOLOGIES CO., LTD.: Un método de control de longitud de onda, que comprende: ajustar , las potencias de todas las subportadoras en un supercanal en un […]

Método para determinar parámetros de enlace y red óptica de transmisión WDM modulada por OFDM, del 25 de Diciembre de 2019, de DEUTSCHE TELEKOM AG: Método para determinar parámetros de enlace de un primer enlace de comunicación entre un primer y un segundo nodos de red de una red óptica de transmisión que […]

Suministro de potencia remoto de separadores ópticos, del 17 de Octubre de 2019, de ARRIS Enterprises LLC: Un sistema óptico que comprende al menos un separador/combinador óptico de agregación , una pluralidad de separadores/combinadores ópticos de contribución situados […]

Procedimiento y sistema para implementar rutas alternativas en la red de transmisión óptica de la red óptica conmutada en longitud de onda (wson), del 2 de Octubre de 2019, de ZTE CORPORATION: Un procedimiento para implementar rutas alternativas en la red de transmisión óptica de la red óptica conmutada en longitud de onda, WSON, que comprende: una […]