CONTROLADOR DE ACCESO DIRECTO A MEMORIA (DMAC) PARA GESTIONAR TRANSFERENCIAS DE LONGITUDES DESCONOCIDAS.

Método de realización de operaciones de Acceso Directo a Memoria (DMA) con intervención mínima por parte de un procesador (12),

mediante un controlador (20) de DMA, operativo para transferir datos de longitud desconocida, que tiene uno o más canales, que comprende, para por lo menos un canal de DMA: ejecutar una primera transferencia (66, 68) de DMA y mantener un recuento de los datos transferidos (70); almacenar el recuento de datos transferidos (76, 77, 78), e iniciar la ejecución de una segunda transferencia de DMA antes de que el procesador lea el recuento almacenado de datos transferidos

Tipo: Patente Internacional (Tratado de Cooperación de Patentes). Resumen de patente/invención. Número de Solicitud: PCT/EP2007/062728.

Solicitante: TELEFONAKTIEBOLAGET LM ERICSSON (PUBL).

Nacionalidad solicitante: Suecia.

Dirección: ERICSSON AB PATENT UNIT MOBILE PLATFORMS NYA VATTENTORNET 221 83 LUND SUECIA.

Inventor/es: BARROW, DAVID, ROBERTS,PATRICIA.

Fecha de Publicación: .

Fecha Solicitud PCT: 23 de Noviembre de 2007.

Fecha Concesión Europea: 18 de Agosto de 2010.

Clasificación Internacional de Patentes:

- G06F13/28 FISICA. › G06 CALCULO; CONTEO. › G06F PROCESAMIENTO ELECTRICO DE DATOS DIGITALES (sistemas de computadores basados en modelos de cálculo específicos G06N). › G06F 13/00 Interconexión o transferencia de información u otras señales entre memorias, dispositivos de entrada/salida o unidades de procesamiento (circuitos de interfaz para dispositivos de entrada/salida específicos G06F 3/00; sistemas multiprocesadores G06F 15/16). › utilizando la transferencia por ráfaga, p. ej. acceso directo a la memoria, robo de ciclo (G06F 13/32 tiene prioridad).

Clasificación PCT:

- G06F13/28 G06F 13/00 […] › utilizando la transferencia por ráfaga, p. ej. acceso directo a la memoria, robo de ciclo (G06F 13/32 tiene prioridad).

Países PCT: Austria, Bélgica, Suiza, Alemania, Dinamarca, España, Francia, Reino Unido, Grecia, Italia, Liechtensein, Luxemburgo, Países Bajos, Suecia, Mónaco, Portugal, Irlanda, Eslovenia, Finlandia, Rumania, Chipre, Lituania, Letonia.

Fragmento de la descripción:

ANTECEDENTES

La presente invención se refiere a circuitos de proceso de datos, y en particular a un controlador de Acceso Directo a Memoria (DMA) operativo para mantener y almacenar un recuento de transferencias.

5 Las operaciones de DMA son bien conocidas en la técnica. Un controlador de DMA funciona de manera que libera de tareas rutinarias de transferencia de datos a un procesador u otro controlador del sistema. En una operación ilustrativa de transferencia de DMA, un procesador inicializa el controlador de DMA con información de origen y de destino, información de control, y un tamaño de la transferencia. El controlador de DMA lee de forma autónoma datos del origen, que puede comprender un periférico, tal como una interfaz de comunicaciones, o una posición de memoria, y escribe los datos en el destino, que también puede comprender un periférico o una memoria. Por consiguiente, la transferencia de DMA puede ser desde un periférico a un periférico, de periférico a memoria, de memoria a periférico, o de memoria a memoria. El controlador de DMA almacena típicamente el tamaño de la transferencia en un contador, y lo decrementa tras escribir cada dato (por ejemplo, byte, media palabra, etcétera). Cuando el tamaño de la transferencia se ha decrementado hasta cero, se ha completado la operación de transferencia de DMA, y el controlador de DMA puede interrumpir el procesador, activar una bandera en un registro de estados o

20 de control, o indicar de otra manera que se ha completado la transferencia de datos. Un controlador de DMA multicanal realiza dos o más operaciones de transferencia de DMA en paralelo, típicamente mediante el multiplexado por división de tiempo de las transferencias de DMA. Las operaciones de transferencia de DMA pueden estar enlazadas. Por ejemplo, una transferencia de datos de mucho tamaño se puede descomponer en una secuencia de transferencias más pequeñas. El controlador de DMA se puede inicializar con información de origen, de destino, de tamaño de la transferencia, y otra información de control, y se le puede proporcionar adicionalmente una dirección de enlace. Cuando el controlador de DMA completa la transferencia de DMA, lee un conjunto nuevo de información de origen, de destino, de tamaño de transferencia y de control a partir de la dirección de enlace, así como una dirección de enlace nueva, y comienza inmediatamente una operación nueva de transferencia de DMA. De este modo, un número elevado de operaciones de transferencia de DMA puede estar enlazado, o encadenado, entre sí para mover grandes cantidades de datos.

35 En muchos casos, la longitud de una transferencia de DMA no se conoce por

adelantado. Por ejemplo, una transferencia de DMA desde un periférico de comunicaciones a memoria puede transferir uno o más paquetes cuya longitud no sea conocida antes de recibirlos en el periférico. Adicionalmente, las transferencias de DMA de una longitud nominalmente conocida pueden finalizar de forma prematura, por 5 ejemplo, si se acaba el tiempo de espera de un periférico, o si se llena una memoria intermedia de destino. En cualquier caso, el software necesita averiguar la cantidad de datos transferidos para poder procesarlos. En controladores de DMA convencionales, el recuento de transferencias (o bien incrementado desde cero o bien decrementado desde un recuento de transferencias nominal) debe ser leído por el procesador antes

10 de que el controlador de DMA comience una transferencia de DMA sucesiva, la cual se escribirá encima del registro de recuentos o contador de transferencias de DMA. Incluso si el controlador de DMA interrumpe al procesador cuando finaliza la operación de transferencia de DMA, el cambio de contexto requerido para que el procesador detenga la ejecución, cargue una rutina de servicio de interrupción, y lea el recuento de transferencias de DMA – liberando de este modo al controlador de DMA para realizar una operación sucesiva de transferencia de DMA – requiere un retardo elevado y en muchos casos inaceptable. A medida que aumenta la funcionalidad y la complejidad de los sistemas informáticos, aumenta en su totalidad el número de periféricos que comparten datos, la cantidad de datos a transferir, y las velocidades de datos del sistema, reduciéndose el retardo aceptable máximo entre operaciones de transferencia de DMA. Por consiguiente, existe en la técnica una necesidad de “desacoplar” el procesador con respecto al controlador de DMA en el caso de transferencias de DMA de tamaño desconocido. El documento US6253261 da a conocer el uso de órdenes de “continuación” para dichas transferencias.

SUMARIO

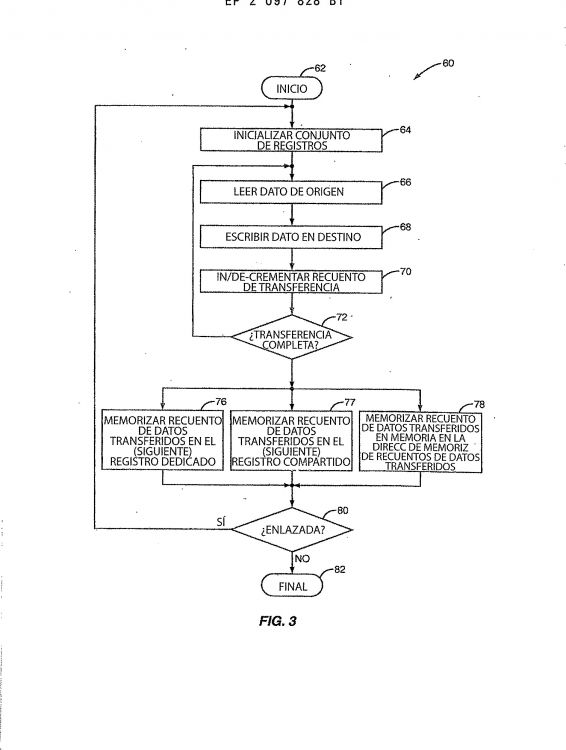

Según una o más realizaciones, un controlador de DMA mantiene un recuento de datos transferidos en cada operación de DMA, y memoriza el recuento de datos transferidos al final de la operación de DMA. El controlador de DMA puede dar comienzo entonces a una operación sucesiva de transferencia de DMA, sin esperar a que un procesador lea el recuento de datos transferidos. El recuento de datos transferidos se puede escribir en memoria en una dirección especificada en un registro de direcciones de memorización de recuentos de datos transferidos; se puede memorizar en un registro de recuentos de datos transferidos dedicado al canal de DMA; o se puede memorizar en un registro de recuentos de datos transferidos compartido entre dos o más canales de DMA. El procesador puede leer el recuento de datos transferidos y, si procede, borrar el registro pertinente de recuentos de datos transferidos, después de que el controlador de DMA dé inicio a otra operación de DMA en ese canal de DMA.

5 En una realización, la presente invención se refiere a un método de desacoplamiento de operaciones de DMA con respecto a un procesador, mediante un controlador de DMA que tiene uno o más canales. Para por lo menos un canal de DMA, se ejecuta una primera transferencia de DMA y se mantiene un recuento de los datos transferidos. El recuento de datos transferidos se almacena. La ejecución de una segunda transferencia de DMA da comienzo antes de que el procesador lea el recuento almacenado de datos transferidos. En otra realización, la presente invención se refiere a un controlador de DMA que soporta uno o más canales de DMA. El controlador de DMA incluye un conjunto de registros asociados a cada canal de DMA, incluyendo el conjunto por lo menos un contador operativo para mantener un recuento de datos transferidos en cada operación de DMA. El controlador de DMA incluye también un circuito de control operativo para memorizar el recuento de datos transferidos después de cada operación de DMA, y operativo además para dar inicio a una operación de DMA sucesiva antes de que un procesador lea el recuento memorizado de datos transferidos.

20 Todavía en otra realización, la presente invención se refiere a un sistema de proceso de datos. El sistema incluye un procesador, una memoria, y un controlador de DMA que soporta uno o más canales de DMA. El sistema incluye también un conjunto de registros en el controlador de DMA asociado a cada canal de DMA, incluyendo el conjunto por lo menos un contador operativo para mantener un recuento de datos transferidos en cada operación de DMA. El sistema incluye además un circuito de control en el controlador de DMA, operativo para memorizar el recuento de datos transferidos después de cada operación de DMA, y operativo además para dar inicio a una operación de DMA sucesiva antes de que el procesador lea el recuento memorizado de datos transferidos.

BREVE DESCRIPCIÓN DE LOS DIBUJOS

La Figura 1 es un diagrama de bloques funcionales de un sistema de proceso de datos. La Figura 2 es un diagrama de bloques de un conjunto de registros asociado a

35 cada canal de DMA.

La Figura 3 es un diagrama de flujo de un método de ejecución de operaciones de DMA.

DESCRIPCIÓN DETALLADA

5 La Figura 1 representa un diagrama de bloques funcionales de un sistema representativo de proceso de datos, indicado de forma general con el número 10. El sistema 10 incluye un procesador 12, u otro controlador tal como un Procesador de Señales Digitales (DSP), un microcontrolador integrado, una máquina de estados implementada en un ASIC ó FPGA, o similares. El procesador 12 está conectado a un bus 14 de alta velocidad, y transfiere datos a través del bus de alta velocidad hacia y desde la memoria 16. Otros componentes del sistema 10 con comunicación de gran ancho de banda hacia la memoria 16, tales como un controlador 18 de gráficos y un controlador 20 de DMA, están conectados también al bus 14 de alta velocidad....

Reivindicaciones:

1. Método de realización de operaciones de Acceso Directo a Memoria (DMA) con intervención mínima por parte de un procesador (12), mediante un controlador (20) de DMA, operativo para transferir datos de longitud desconocida, que tiene uno o más canales, que comprende, para por lo menos un canal de DMA:

ejecutar una primera transferencia (66, 68) de DMA y mantener un recuento de los datos transferidos (70); almacenar el recuento de datos transferidos (76, 77, 78), e iniciar la ejecución de una segunda transferencia de DMA antes de que el procesador lea el recuento almacenado de datos transferidos.

2. Método de la reivindicación 1, en el que el almacenamiento del recuento de

15 datos transferidos comprende escribir el recuento en una posición predeterminada de memoria.

3. Método de la reivindicación 2, en el que la posición predeterminada de memoria la especifica el procesador para cada transferencia de DMA.

4. Método de la reivindicación 1, en el que el almacenamiento del recuento de datos transferidos comprende memorizar el recuento en un registro de recuentos de transferencias de DMA en el controlador de DMA.

25 5. Método de la reivindicación 4, en el que el registro de recuentos de transferencias de DMA se asocia al canal de DMA o en el que el registro de recuentos de transferencias de DMA es compartido por dos o más canales de DMA.

6. Método de la reivindicación 5, en el que el registro de recuentos de

30 transferencias de DMA es uno de una pluralidad de registros de recuentos de transferencias de DMA asociados al canal de DMA o compartidos por los dos o más canales de DMA respectivamente.

7. Controlador (20) de Acceso Directo a Memoria (DMA), operativo para 35 transferir datos de longitud desconocida, que soporta uno o más canales de DMA, que comprende:

un conjunto de registros (40) asociado a cada canal de DMA, incluyendo el conjunto por lo menos un contador operativo para mantener un recuento de datos transferidos en cada operación (54a, 54b, 54c) de DMA; y un circuito de control operativo para memorizar el recuento de datos transferidos después de cada operación de DMA, y operativo además para iniciar una operación sucesiva de DMA antes de que un procesador (12) lea el recuento memorizado de datos transferidos.

8. Controlador de DMA de la reivindicación 7, en el que cada conjunto de registros incluye además un registro de direcciones de memorización de recuentos de datos transferidos, y en el que el circuito de control es operativo además para escribir el recuento de datos transferidos en memoria en una dirección almacenada en el

15 registro de direcciones de memorización de recuentos de datos transferidos.

9. Controlador de DMA de la reivindicación 7, en el que cada conjunto de registros incluye además un registro de recuentos de datos transferidos encima del cual no se escribe antes de cada operación de DMA, y en el que el circuito de control

20 es operativo para memorizar el recuento de datos transferidos en el registro de recuentos de datos transferidos.

10. Controlador de DMA de la reivindicación 9, en el que cada conjunto de registros incluye además una pluralidad de registros de recuentos de datos

25 transferidos, y en el que el circuito de control memoriza el recuento de datos transferidos para una pluralidad de operaciones sucesivas de DMA en los registros de recuentos de datos transferidos.

11. Controlador de DMA de la reivindicación 10, en el que el circuito de control

30 memoriza adicionalmente una indicación de tiempo con cada recuento de datos transferidos.

12. Controlador de DMA de la reivindicación 7, que comprende además un

registro compartido de recuentos de datos transferidos encima del cual no se escribe 35 antes de cada operación de DMA, y en el que el circuito de control es operativo para memorizar el recuento de datos transferidos de cualquier canal de DMA en el registro compartido de recuentos de datos transferidos.

13. Controlador de DMA de la reivindicación 12, que comprende además una pluralidad de registros compartidos de recuentos de datos transferidos, y en el que el circuito de control memoriza el recuento de datos transferidos para una pluralidad de operaciones sucesivas de DMA en los registros compartidos de recuentos de datos transferidos.

10 14. Controlador de DMA de la reivindicación 13, en el que el circuito de control memoriza adicionalmente una indicación de tiempo con cada recuento de datos transferidos.

15. Sistema de proceso de datos, que comprende:

15 un procesador; una memoria; y el controlador de Acceso Directo a Memoria (DMA), de cualquiera de las reivindicaciones 7 a 14.

Patentes similares o relacionadas:

Sistema de procesamiento de datos y método de procesamiento de datos, del 1 de Enero de 2020, de HUAWEI TECHNOLOGIES CO., LTD.: Un sistema de procesamiento de datos , que comprende una unidad central de procesamiento, CPU , una memoria , un controlador […]

Solución Ethernet universal, del 2 de Octubre de 2019, de SCHNEIDER ELECTRIC INDUSTRIES SAS: Un circuito integrado monolítico , que comprende: al menos un núcleo de procesador de aplicaciones utilizable para ejecutar una aplicación industrial y código de […]

Comunicación de audio multicanal en un sistema de bus multimedia inter-chip serie de baja potencia (SLIMbus), del 28 de Marzo de 2019, de QUALCOMM INCORPORATED: Una fuente de audio que comprende: un puerto de salida multicanal (302(X)) configurado para ser acoplado a un bus de multiplexado por división de tiempo, TDM, que comprende […]

Método de migración en directo de máquina virtual, método de procesamiento de datos de memoria de máquina virtual, servidor y sistema de máquina virtual, del 27 de Marzo de 2019, de HUAWEI TECHNOLOGIES CO., LTD.: Un método de procesamiento de datos de memoria de máquina virtual, aplicado a un sistema de máquina virtual, en donde el sistema de máquina virtual comprende una […]

Sistema informático, método para acceder a un terminal de interconexión de componentes periféricos exprés y equipo, del 26 de Octubre de 2018, de HUAWEI TECHNOLOGIES CO., LTD.: Un proxy de acceso, en donde el proxy de acceso se aplica a un sistema informático, el sistema informático comprende un procesador y un bus de interconexión […]

Método de lectura/escritura de fichero y terminal móvil, del 14 de Diciembre de 2015, de HUAWEI DEVICE CO., LTD: Un método de lectura/escritura de fichero utilizado en un terminal móvil, que comprende:

determinar si un fichero objeto de lectura […]

Método de lectura/escritura de fichero y terminal móvil, del 14 de Diciembre de 2015, de HUAWEI DEVICE CO., LTD: Un método de lectura/escritura de fichero utilizado en un terminal móvil, que comprende:

determinar si un fichero objeto de lectura […]

Sistema y método para permitir la extracción rápida de datos de imagen entrelazados, del 3 de Diciembre de 2014, de Core Wireless Licensing S.a.r.l: Método de procesado de una unidad de datos entrelazados que incluye una pluralidad de fragmentos de datos de un primer tipo y una pluralidad de […]

Adaptadores de habilitación/deshabilitación de un entorno de ordenadores, del 12 de Febrero de 2014, de INTERNATIONAL BUSINESS MACHINES CORPORATION: Un método para habilitar adaptadores en un entorno de ordenadores, que comprende las etapas de: responder para ejecutar una instrucción de Procesador Lógico de […]