APARATO DE PROCESADO DE DATOS, APARATO DE ALMACENAMIENTO EXTERNO, SISTEMA DE PROCESADO DE DATOS Y METODO DE TRANSMISION DE DATOS.

Aparato externo que comprende: una E/S de señales para comunicar datos hacia/desde un aparato (10) de procesado de datos usando señales en serie a través de una primera línea (33) de señal5 ;

una entrada de señales de sincronización para capturar una señal de sincronización de dichos datos desde dicho aparato (10) de procesado de datos a través de una tercera línea (31) de señal, caracterizado porque dicho aparato externo comprende además una entrada de señales de control para capturar una señal de control con el fin de controlar la temporización de la transmisión de dichos datos desde dicho aparato (10) de procesado de datos a través de una segunda línea (32) de señal, en el que dicha E/S de señales está adaptada para transmitir datos a través de dicha primera línea (33) de señal en un periodo de tiempo en el que a dicha entrada de señales de control se le suministra dicha señal de control y para transmitir una señal de estado que indica un estado del funcionamiento de dicho aparato externo (20) a través de dicha primera línea (33) de señal en un periodo de tiempo en el que a dicha entrada de señales de control no se le suministra dicha señal de control

Tipo: Patente Europea. Resumen de patente/invención. Número de Solicitud: E07122151.

Solicitante: SONY CORPORATION.

Nacionalidad solicitante: Japón.

Dirección: 1-7-1 KONAN MINATO-KU TOKYO 108-0075 JAPON.

Inventor/es: HIRABAYASHI, MITSUHIRO, NAKANISHI, KENICHI.

Fecha de Publicación: .

Fecha Solicitud PCT: 2 de Junio de 1998.

Fecha Concesión Europea: 11 de Agosto de 2010.

Clasificación PCT:

- G06F13/42 FISICA. › G06 CALCULO; CONTEO. › G06F PROCESAMIENTO ELECTRICO DE DATOS DIGITALES (sistemas de computadores basados en modelos de cálculo específicos G06N). › G06F 13/00 Interconexión o transferencia de información u otras señales entre memorias, dispositivos de entrada/salida o unidades de procesamiento (circuitos de interfaz para dispositivos de entrada/salida específicos G06F 3/00; sistemas multiprocesadores G06F 15/16). › Protocolo de transferencia para bus, p. ej. interbloqueo; Sincronización.

Países PCT: Alemania, España, Francia, Reino Unido, Italia, Países Bajos, Suecia, Finlandia.

Fragmento de la descripción:

Campo de la invención

La presente invención se refiere a un aparato de procesado de datos, un sistema de procesado de datos y un método de transmisión de datos para comunicar datos a un aparato de almacenamiento externo usando una interfaz serie, y se refiere también a un aparato de almacenamiento externo adaptable al aparato de procesado 5 de datos, al sistema de procesado de datos y al método de transmisión de datos.

Anterioridades relacionadas

Hasta el momento, se ha conocido un aparato de procesado de datos al que se conecta una tarjeta de memoria que incluye un soporte de almacenamiento, tal como una memoria flash. A continuación, en referencia a los dibujos, se describirán un 10 aparato convencional de procesado de datos del tipo anterior y una tarjeta de memoria dispuesta para conectarse al aparato de procesado de datos.

Tal como se muestra en la Fig. 1, un aparato 100 de procesado de datos incluye un bloque 101 de procesado de datos, un registro 102, un circuito 103 de interfaz serie en el lado del anfitrión y un controlador 104 en el lado del anfitrión. La 15 tarjeta 110 de memoria incluye una memoria 111, un registro 112, un circuito 113 de interfaz serie en el lado de la tarjeta y un controlador 114 en el lado de la tarjeta.

El bloque 101 de procesado de datos del aparato 100 de procesado de datos lee datos almacenados en la tarjeta 110 de memoria para someter datos leídos a una variedad de procesos. Además, el bloque 101 de procesado de datos ejecuta la 20 variedad de los procesos de datos para generar datos que se escribirán en la tarjeta 110 de memoria. Es decir, el bloque 101 de procesado de datos actúa como circuito de procesado de datos para una variedad de aparatos de un tipo que utiliza la tarjeta 110 de memoria.

El registro 102 es una memoria intermedia entre el bloque 101 de procesado de 25 datos y el circuito 103 de interfaz serie del lado del anfitrión. Es decir, cuando se suministran datos desde el bloque 101 de procesado de datos al circuito 103 de interfaz serie del lado del anfitrión, el aparato 100 de procesado de datos almacena temporalmente datos en el registro 102, y a continuación suministra datos al circuito 103 de interfaz serie del lado del anfitrión. De modo similar, el aparato 100 de 30 procesado de datos almacena temporalmente datos en el registro 102, y a continuación suministra datos al bloque 101 de procesado de datos cuando se suministran datos desde el circuito 103 de interfaz serie del lado del anfitrión al bloque 101 de procesado de datos.

El circuito 103 de interfaz serie del lado del anfitrión convierte datos 35 suministrados desde el bloque 101 de procesado de datos a través del registro 102 y una orden suministrada desde el controlador 114 del lado de la tarjeta en señales en serie para suministrar las señales en serie a la tarjeta 110 de memoria. Por otra parte, el circuito 103 de interfaz serie del lado del anfitrión convierte datos de la señal en serie y la orden suministrada desde la tarjeta 110 de memoria en señales en paralelo 5 para suministrar las señales en paralelo al bloque 101 de procesado de datos y el controlador 114 del lado de la tarjeta.

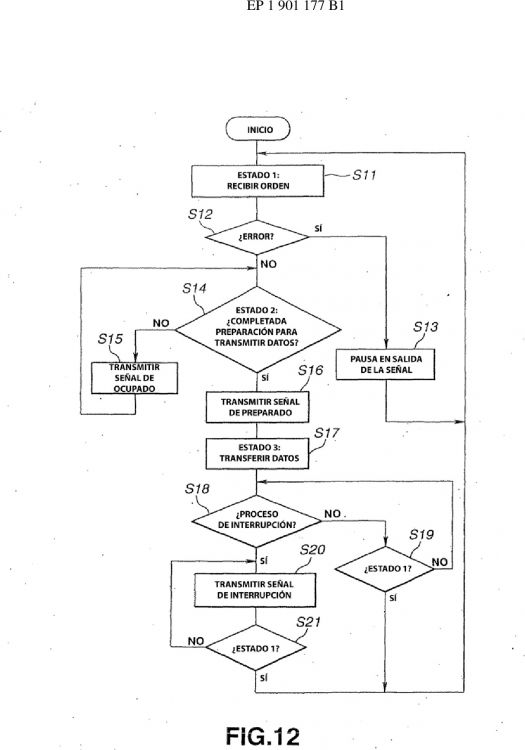

El circuito 103 de interfaz serie del lado del anfitrión suministra una señal de sincronización (CLK) de datos y la orden y una señal de selección de chip (CS) a la tarjeta 110 de memoria. El circuito 103 de interfaz serie del lado del anfitrión captura 10 una señal de ocupado (OCUPADO) y una señal de interrupción (INTERRUPCIÓN) suministradas desde la tarjeta 110 de memoria.

El controlador 104 del lado del anfitrión controla la operación de procesado de datos que es realizada por el bloque 101 de procesado de datos y una operación de transmisión de datos que es realizada por el circuito 103 de interfaz serie del lado del 15 anfitrión. El controlador 104 del lado del anfitrión suministra una orden, que es una orden de control para la tarjeta 110 de memoria, a la tarjeta 110 de memoria a través del registro 112.

Por otro lado, la memoria 111 de la tarjeta 110 de memoria incluye, por ejemplo, una memoria flash, en la que se almacenan datos suministrados desde el 20 bloque 101 de procesado de datos.

El registro 112 es una memoria intermedia entre la memoria 111 y el circuito 113 de interfaz serie del lado de la tarjeta. Es decir, la tarjeta 110 de memoria almacena temporalmente datos en el registro 102, y a continuación suministra datos, que se deben escribir, a la memoria 111 cuando en la memoria 111 se escriben datos 25 suministrados desde el aparato 100 de procesado de datos. De modo similar, la tarjeta 110 de memoria almacena temporalmente datos en el registro 102, y a continuación suministra datos, que deben ser leídos, al circuito 113 de interfaz serie del lado de la tarjeta cuando el aparato 100 de procesado de datos lee datos de la memoria 111. Es decir, el registro 112 es un circuito que tiene una función para actuar como memoria 30 intermedia de páginas para la memoria flash.

El circuito 113 de interfaz serie del lado de la tarjeta es controlado por el controlador 114 del lado de la tarjeta de tal manera que convierte datos de la señal en paralelo suministrada desde la memoria 111 y la orden suministrada desde el controlador 114 del lado de la tarjeta en señales en serie para suministrar las señales 35 en serie al aparato 100 de procesado de datos. El circuito 113 de interfaz serie del lado de la tarjeta convierte datos de la señal en serie y la orden suministrada desde el aparato 100 de procesado de datos en señales en paralelo para suministrar las señales en paralelo a la memoria 111 y el controlador 114 del lado de la tarjeta.

El circuito 113 de interfaz serie del lado de la tarjeta captura la señal de 5 sincronización (CLK) de datos y la orden y la señal de selección de chip (CS) desde el aparato 100 de procesado de datos. El circuito 113 de interfaz serie del lado de la tarjeta suministra la señal de ocupado (OCUPADO) y la señal de interrupción (INTERRUPCIÓN) al aparato 100 de procesado de datos.

El controlador 114 del lado de la tarjeta controla operaciones de 10 almacenamiento, lectura y borrado de datos que son realizadas por la memoria 111 según una orden o similar suministrada desde el aparato 100 de procesado de datos. El controlador 114 del lado de la tarjeta controla la operación de transmisión de datos que es realizada por el circuito 113 de interfaz serie del lado de la tarjeta. El controlador 104 del lado del anfitrión captura, desde la tarjeta 110 de memoria, la 15 señal de ocupado y la señal de interrupción que actúan como señales de estado para la tarjeta 110 de memoria.

Una operación para transmitir datos entre el aparato 100 de procesado de datos y la tarjeta 110 de memoria se realiza a través de una línea de transmisión dispuesta entre el circuito 103 de interfaz serie del lado del anfitrión y el circuito 113 de 20 interfaz serie del lado de la tarjeta.

Entre el circuito 113 de interfaz serie del lado de la tarjeta del aparato 100 de procesado de datos y el circuito 113 de interfaz serie del lado de la tarjeta de la tarjeta 110 de memoria, hay dispuestas cinco líneas de señal consistentes en una línea de CLK, una línea de CS, una línea de DT, una línea de OCUPADO y una línea de INT. 25

A la línea de DT se le suministran datos principales, es decir, datos procesados por el bloque 101 de procesado de datos para ser escritos en la memoria 111 y datos que se deben escribir desde la memoria 111 para ser suministrados al bloque 101 de procesado de datos. Por otra parte, hacia la línea de DT se transmiten una orden que se suministra desde el aparato 100 de procesado de datos a la tarjeta 110 de memoria 30 y que actúa como orden de control y una orden que se suministra desde la tarjeta 110 de memoria al aparato 100 de procesado de datos. Es decir, a la línea de DT se transmiten bidireccionalmente datos principales y la orden constituidos en señales en serie.

Una señal de sincronización de datos principales y las órdenes que se 35 transmiten a la línea de DT se suministra desde el aparato 100 de procesado de datos a la tarjeta 110 de memoria a través de la línea de CLK.

La señal denominada de selección de chip se suministra desde el aparato 100 de procesado de datos a la tarjeta 110 de memoria a través de la línea de CS. En un periodo de tiempo en el que el nivel de la señal de selección de chip es alto, se indica 5 el hecho de que los datos principales, las órdenes y las señales de sincronización son efectivos.

Reivindicaciones:

1. Aparato externo que comprende:

una E/S de señales para comunicar datos hacia/desde un aparato (10) de procesado de datos usando señales en serie a través de una primera línea (33) de señal; 5

una entrada de señales de sincronización para capturar una señal de sincronización de dichos datos desde dicho aparato (10) de procesado de datos a través de una tercera línea (31) de señal, caracterizado porque dicho aparato externo comprende además

una entrada de señales de control para capturar una señal de control con el fin 10 de controlar la temporización de la transmisión de dichos datos desde dicho aparato (10) de procesado de datos a través de una segunda línea (32) de señal, en el que

dicha E/S de señales está adaptada para transmitir datos a través de dicha primera línea (33) de señal en un periodo de tiempo en el que a dicha entrada de señales de control se le suministra dicha señal de control y para transmitir una señal 15 de estado que indica un estado del funcionamiento de dicho aparato externo (20) a través de dicha primera línea (33) de señal en un periodo de tiempo en el que a dicha entrada de señales de control no se le suministra dicha señal de control.

2. Aparato externo de la reivindicación 1, en el que

dicha E/S de señales está adaptada para transmitir una señal de interrupción 20 (INT) que indica una interrupción desde dicho aparato externo (20) a través de dicha primera línea (33) de señal en un periodo de tiempo en el que a dicha entrada de señales de control y a dicha entrada de señales de sincronización no se les suministra respectivamente dicha señal de control y dicha señal de sincronización.

3. Aparato externo de la reivindicación 1 ó 2, en el que 25

dicha E/S de señales está adaptada para transmitir dichos datos en un periodo de tiempo en el que a dicha entrada de señales de control se le suministra dicha señal de control y para transmitir, en un periodo de tiempo en el que a dicha entrada de señales de control no se le suministra dicha señal de control, una señal de ocupado que indica que se realiza un proceso basándose en dicha orden de control. 30

4. Aparato externo de una cualquiera de las reivindicaciones 1 a 3, en el que

dicha E/S de señales está adaptada para transmitir y recibir datos a través de tres líneas de señal de reserva en paralelo con dicha primera línea (33) de señal, en donde dichas líneas de señal de reserva se usan además de dicha primera línea (33) de señal para transmitir dichos datos, cuando dicho aparato externo (20) y dicho 35 aparato (10) de procesado de datos están en comunicación paralela.

5. Aparato externo de la reivindicación 4, en el que

dicha E/S de señales está adaptada para transmitir y recibir datos a través de cuatro líneas paralelas formadas por dichas líneas de señal de reserva y dicha primera línea (33) de señal, cuando dicho aparato externo (20) y dicho aparato (10) de 5 procesado de datos están en comunicación paralela.

6. Aparato externo de una cualquiera de las reivindicaciones 1 a 5, que comprende además:

un circuito (21) de almacenamiento para almacenar dichos datos;

una memoria intermedia (22) para almacenar temporalmente datos leídos de 10 dicho circuito (21) de almacenamiento y datos recibidos desde dicho aparato (10) de procesado de datos mediante dicha E/S de señales; y

un circuito (24) de control para controlar dicha E/S de señales con el fin de transmitir/recibir dichos datos hacia/desde dicho aparato (10) de procesado de datos y para controlar dicha unidad (21) de almacenamiento con el fin de realizar una 15 operación para almacenar, leer y borrar datos.

7. Aparato externo de una cualquiera de las reivindicaciones 1 a 6, en el que

el aparato externo (20) está adaptado para determinar, sobre la base de la señal de control, si desde dicho aparato (10) de procesado de datos se transmiten datos de órdenes de control y datos principales o dicho aparato (10) de procesado de 20 datos espera una señal de preparado (RDY) que indica que se ha completado una preparación del aparato externo (20) para transmitir o recibir datos.

8. Aparato externo de una cualquiera de las reivindicaciones 1 a 7, en el que

el aparato externo es una tarjeta de memoria que tiene una forma de tipo tarjeta. 25

9. Sistema de procesado de datos para comunicar datos entre un aparato (10) de procesado de datos y el aparato externo de la reivindicación 1, en el que

dicho aparato (10) de procesado de datos comprende un controlador (14) para generar órdenes hacia dicho aparato externo (20) con el fin de controlar la transmisión de datos hacia y la recepción de datos desde dicho aparato externo (20). 30

10. Método de comunicación de datos entre un aparato (10) de procesado de datos y un aparato externo (20) con forma de tipo tarjeta, que comprende la etapa de:

generar una señal de control para controlar la temporización de la transmisión de datos;

35

generar una señal de sincronización de dichos datos;

transmitir dichos datos a través de una primera línea (33) de señal en un periodo de tiempo en el que dicha señal de control se transmite a través de una segunda línea (32) de señal y dicha señal de sincronización a través de una tercera línea (31) de señal; y 5

transmitir una señal de estado que indica un estado del funcionamiento de dicho aparato externo (20) a través de dicha primera línea (33) de señal en un periodo de tiempo en el que dicha señal de control no se transmite a través de dicha segunda línea (32) de señal.

Patentes similares o relacionadas:

Aparato para establecer la dirección de un módulo utilizando un reloj, del 17 de Junio de 2020, de LEXMARK INTERNATIONAL, INC.: Un circuito integrado específico de la aplicación (ASIC) que comprende: un pin de alimentación; un pin de masa; un pin de reloj I2C; un pin […]

Método para implementar un bus industrial de banda ancha de campo de internet, del 17 de Junio de 2020, de Kyland Technology Co., Ltd: Un método para implementar un bus industrial de banda ancha de campo de internet, caracterizado por que, el método es aplicable a un sistema de arquitectura […]

Sistema de arquitectura de bus de banda ancha de campo de internet de la industria, del 3 de Junio de 2020, de Kyland Technology Co., Ltd: Un sistema de arquitectura de bus de banda ancha de campo de Internet de la industria, caracterizado por que, el sistema comprende un controlador de bus […]

Método para gestionar la configuración del bus de banda ancha del campo de internet industrial, del 3 de Junio de 2020, de Kyland Technology Co., Ltd: Un método para gestionar la configuración de un bus de banda ancha del campo de internet industrial, caracterizado por que, el método es aplicable a […]

Método para implementar un bus de campo en tiempo real de banda ancha de Internet industrial, del 29 de Abril de 2020, de Kyland Technology Co., Ltd: Un método para implementar un bus de campo en tiempo real de banda ancha de Internet industrial, en donde el método puede aplicarse a una red de transferencia […]

Procedimiento para hacer funcionar un sistema de transmisión de datos y sistema de transmisión de datos, del 29 de Abril de 2020, de Siemens Mobility GmbH: Procedimiento para hacer funcionar un sistema de transmisión de datos en el que - un primer equipo de transmisión de datos está conectado […]

Método y aparato para detectar contrapresión de mensajes, del 8 de Abril de 2020, de HUAWEI TECHNOLOGIES CO., LTD.: Un método de detección de contrapresión de paquetes, en donde el método se aplica a un dispositivo que tiene un puerto de Interconexión de […]

Sistema de autenticación e información para instrumentos quirúrgicos reutilizables, del 8 de Abril de 2020, de Covidien LP (100.0%): Un método para comunicar datos a través de un bus, el método que comprende: autenticar un componente quirúrgico utilizando un microchip […]