SISTEMA Y METODO PARA CONTROLAR UN BUS.

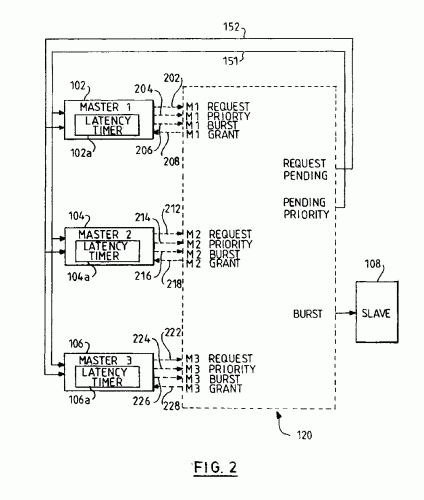

SE PODRA MEJORAR EL RENDIMIENTO DE UN BUS EN UN SISTEMA DE ORDENADOR CON DISPOSITIVOS MULTIPLES 102,

104, 106 ACCEDIENDO A UN BUS 132 COMPARTIDO COMUN MEDIANTE EL INCREMENTO DE LA PRODUCCION Y DISMINUYENDO LA LATENCIA MIENTRAS SE REALIZAN CAMBIOS DINAMICOS EN EL USO DEL BUS. LOS DISPOSITIVOS PRESENTAN UN NIVEL DE PRIORIDAD CONJUNTAMENTE CON UNA PETICION DE BUS AL CONTROLADOR DE BUS 120. TRAS LA RECEPCION DE SOLICITUDES MULTIPLES, UN ARBITRO DEL CONTROLADOR 130 DE BUS COMPARA LOS NIVELES DE PRIORIDAD ASOCIADOS CON LAS DIFERENTES PETICIONES DE BUS Y OTORGA EL CONTROL DEL BUS AL DISPOSITIVO QUE TIENE EL NIVEL DE PRIORIDAD MAS ALTO. DURANTE CADA CICLO EN QUE EL DISPOSITIVO TIENE EL CONTROL DEL BUS, UN CIRCUITO LOGICO DE REALIMENTACION DEL CONTROLADOR DEL BUS DETERMINA SI EXISTEN OTRAS PETICIONES DE BUS PENDIENTES Y SI ES ASI DETERMINA EL NIVEL DE PRIORIDAD DE PETICION PENDIENTE MAS ALTO. LAS SEÑALES CORRESPONDIENTES A LOS RESULTADOS DE DICHAS DETERMINACIONES SON REALIMENTADAS A CADA DISPOSITIVO. EL DISPOSITIVO QUE TIENE EL CONTROL DEL BUS USA LA COMBINACION DEL NIVEL DE PRIORIDAD DE PETICION PENDIENTE EN CURSO Y EL PROPIO TEMPORIZADOR DE LATENCIA 102A, 104A, 106A DEL DISPOSITIVO PARA DETERMINAR SI DEBE MANTENER EL CONTROL DEL BUS O LIBERAR DICHO CONTROL. SI EL TEMPORIZADOR DE LATENCIA DEL DISPOSITIVO NO HA EXPIRADO, EL DISPOSITIVO CONTINUARA CONTROLANDO EL BUS INCLUSO SI EL NIVEL DE PRIORIDAD DE PETICION PENDIENTE EN CURSO ES MAYOR QUE EL NIVEL DE PRIORIDAD DEL DISPOSITIVO. SI EL NIVEL DE PRIORIDAD DE PETICION PENDIENTE EN CURSO NO ES SUPERIOR AL PROPIO NIVEL DE PRIORIDAD DEL DISPOSITIVO, EL DISPOSITIVO CONTINUARA CON EL CONTROL DEL BUS INCLUSO UNA VEZ QUE HA EXPIRADO EL TEMPORIZADOR DE LATENCIA DEL DISPOSITIVO HASTA QUE EL DISPOSITIVO NO NECESITE EL BUS. FINALMENTE, SI EL NIVEL DE PRIORIDAD DE SOLICITUD PENDIENTE EN CURSO ES SUPERIOR QUE EL PROPIO NIVEL DE PRIORIDAD DEL DISPOSITIVO, Y EL TEMPORIZADOR DE LATENCIA DEL DISPOSITIVO HA EXPIRADO, EL DISPOSITIVO ABANDONARA EL CONTROL DEL BUS. DE DICHA FORMA, EL TEMPORIZADOR DE LATENCIA DEL DISPOSITIVO SE EXTIENDE DINAMICAMENTE TRAS LA EXPIRACION EN TANTO EN CUANTO EL DISPOSITIVO TENGA UN NIVEL DE PRIORIDAD AL MENOS TAN GRANDE COMO LA PRIORIDAD DE SOLICITUD PENDIENTE EN CURSO.

Tipo: Resumen de patente/invención.

Solicitante: INTERNATIONAL BUSINESS MACHINES CORPORATION.

Nacionalidad solicitante: Estados Unidos de América.

Dirección: OLD ORCHARD ROAD,ARMONK, N.Y. 10504.

Inventor/es: REVILLA, JUAN G., SATORIUS, THOMAS A., SCHAFFER, MARK M.

Fecha de Publicación: .

Fecha Concesión Europea: 17 de Mayo de 2006.

Clasificación Internacional de Patentes:

- G06F13/364 FISICA. › G06 CALCULO; CONTEO. › G06F PROCESAMIENTO ELECTRICO DE DATOS DIGITALES (sistemas de computadores basados en modelos de cálculo específicos G06N). › G06F 13/00 Interconexión o transferencia de información u otras señales entre memorias, dispositivos de entrada/salida o unidades de procesamiento (circuitos de interfaz para dispositivos de entrada/salida específicos G06F 3/00; sistemas multiprocesadores G06F 15/16). › utilizando señales independientes de petición o de autorización, p. ej. utilizando líneas separadas de petición y de autorización.

Clasificación PCT:

- G06F13/364 G06F 13/00 […] › utilizando señales independientes de petición o de autorización, p. ej. utilizando líneas separadas de petición y de autorización.

Patentes similares o relacionadas:

Circuito eléctrico para la transmisión de señales entre dos maestros y uno o varios esclavos, del 22 de Enero de 2016, de ROBERT BOSCH GMBH: Circuito eléctrico que comprende dos maestros y uno o varios esclavos , diseñado para la transmisión de señales entre dos maestros (11, […]

Circuito eléctrico para la transmisión de señales entre dos maestros y uno o varios esclavos, del 22 de Enero de 2016, de ROBERT BOSCH GMBH: Circuito eléctrico que comprende dos maestros y uno o varios esclavos , diseñado para la transmisión de señales entre dos maestros (11, […]

MECANISMO DE ARBITRAJE EN COLAS DE ESPERA PARA SISTEMA DE TRATAMIENTO DE DATOS., del 16 de Mayo de 2003, de INTERNATIONAL BUSINESS MACHINES CORPORATION: UN MECANISMO DE ARBITRAJE DE COLAS QUE TRANSFIERE TODAS LAS PETICIONES DE LA VIA PRINCIPAL TRANSMISORA DEL PROCESADOR DE COLAS AL CONTROLADOR/ARBITRADOR […]

SISTEMA DE ASIGNACION DE BUS PARA PROCESADORES DE SEÑALES DIGITALES., del 16 de Abril de 1999, de IONICA INTERNATIONAL LIMITED: TRES PROCESADORES DSP REQUIEREN SELECTIVAMENTE EL ACCESO A UNA FUENTE COMPARTIDA, TAL COMO UNA MEMORIA EXTERNA, A TRAVES DE UN BUS DE COMUNICACION […]

METODO PARA UNA SERIE DE INTERVENCIONES TEMPORALES DE LAS UNIDADES DE TRANSMISION DE DATOS Y DE LAS UNIDADES DE ELABORACION SOBRE EL CAMPO DE UN MULTIPORT., del 1 de Junio de 1997, de SIEMENS NIXDORF INFORMATIONSSYSTEME AKTIENGESELLSCHAFT: UN SISTEMA BUSSY CON UN ACUMULADOR (MEM) SIRVE COMO CAMPO MULTIPORT (MUPO). MEDIANTE LA INTERVENCION ALTERNA (ZUG) SOBRE ESTE ACUMULADOR (MEM) SE TRANSMITEN […]

SISTEMA DE COMUNICACIONES PARA EJECUTAR TAREAS EN PARALELO MEDIANTE ORDENADORES PERSONALES, del 25 de Agosto de 2009, de UNIVERSIDAD DE CORDOBA: Sistema de comunicaciones para ejecutar tareas en paralelo mediante ordenadores personales.#Comprende un nodo maestro y una pluralidad de nodos […]

SISTEMA DE COMUNICACIONES PARA EJECUTAR TAREAS EN PARALELO MEDIANTE ORDENADORES PERSONALES, del 25 de Agosto de 2009, de UNIVERSIDAD DE CORDOBA: Sistema de comunicaciones para ejecutar tareas en paralelo mediante ordenadores personales.#Comprende un nodo maestro y una pluralidad de nodos […]