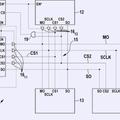

SISTEMA DE ASIGNACION DE BUS PARA PROCESADORES DE SEÑALES DIGITALES.

TRES PROCESADORES DSP REQUIEREN SELECTIVAMENTE EL ACCESO A UNA FUENTE COMPARTIDA,

TAL COMO UNA MEMORIA EXTERNA, A TRAVES DE UN BUS DE COMUNICACION COMUN. UNA UNIDAD DE CONTROL CONTROLA LA ASIGNACION DEL BUS A LOS PROCESADORES PARA PERMITIR ESTE ACCESO. EL BUS ES ASIGNADO POR DEFECTO A LA UNIDAD DE CONTROL EN LUGAR DE A UN PROCESADOR.

Tipo: Resumen de patente/invención.

Solicitante: IONICA INTERNATIONAL LIMITED.

Nacionalidad solicitante: Reino Unido.

Dirección: COWLEY ROAD,CAMBRIDGE CB4 4AS.

Inventor/es: IRVING, CLIVE, RUSSELL, SPREADBURY, DAVID, JOHN.

Fecha de Publicación: .

Fecha Solicitud PCT: 8 de Septiembre de 1995.

Fecha Concesión Europea: 2 de Diciembre de 1998.

Clasificación Internacional de Patentes:

- G06F13/364 FISICA. › G06 CALCULO; CONTEO. › G06F PROCESAMIENTO ELECTRICO DE DATOS DIGITALES (sistemas de computadores basados en modelos de cálculo específicos G06N). › G06F 13/00 Interconexión o transferencia de información u otras señales entre memorias, dispositivos de entrada/salida o unidades de procesamiento (circuitos de interfaz para dispositivos de entrada/salida específicos G06F 3/00; sistemas multiprocesadores G06F 15/16). › utilizando señales independientes de petición o de autorización, p. ej. utilizando líneas separadas de petición y de autorización.

Países PCT: Austria, Bélgica, Suiza, Alemania, Dinamarca, España, Francia, Reino Unido, Grecia, Italia, Liechtensein, Luxemburgo, Países Bajos, Mónaco, Irlanda, Oficina Europea de Patentes, Burkina Faso, Benin, República Centroafricana, Congo, Costa de Marfil, Camerún, Gabón, Guinea, Malí, Mauritania, Niger, Senegal, Chad, Togo, Organización Africana de la Propiedad Intelectual.

Patentes similares o relacionadas:

Circuito eléctrico para la transmisión de señales entre dos maestros y uno o varios esclavos, del 22 de Enero de 2016, de ROBERT BOSCH GMBH: Circuito eléctrico que comprende dos maestros y uno o varios esclavos , diseñado para la transmisión de señales entre dos maestros (11, […]

Circuito eléctrico para la transmisión de señales entre dos maestros y uno o varios esclavos, del 22 de Enero de 2016, de ROBERT BOSCH GMBH: Circuito eléctrico que comprende dos maestros y uno o varios esclavos , diseñado para la transmisión de señales entre dos maestros (11, […]

SISTEMA Y METODO PARA CONTROLAR UN BUS., del 1 de Febrero de 2007, de INTERNATIONAL BUSINESS MACHINES CORPORATION: SE PODRA MEJORAR EL RENDIMIENTO DE UN BUS EN UN SISTEMA DE ORDENADOR CON DISPOSITIVOS MULTIPLES 102, 104, 106 ACCEDIENDO A UN BUS 132 COMPARTIDO COMUN […]

MECANISMO DE ARBITRAJE EN COLAS DE ESPERA PARA SISTEMA DE TRATAMIENTO DE DATOS., del 16 de Mayo de 2003, de INTERNATIONAL BUSINESS MACHINES CORPORATION: UN MECANISMO DE ARBITRAJE DE COLAS QUE TRANSFIERE TODAS LAS PETICIONES DE LA VIA PRINCIPAL TRANSMISORA DEL PROCESADOR DE COLAS AL CONTROLADOR/ARBITRADOR […]

METODO PARA UNA SERIE DE INTERVENCIONES TEMPORALES DE LAS UNIDADES DE TRANSMISION DE DATOS Y DE LAS UNIDADES DE ELABORACION SOBRE EL CAMPO DE UN MULTIPORT., del 1 de Junio de 1997, de SIEMENS NIXDORF INFORMATIONSSYSTEME AKTIENGESELLSCHAFT: UN SISTEMA BUSSY CON UN ACUMULADOR (MEM) SIRVE COMO CAMPO MULTIPORT (MUPO). MEDIANTE LA INTERVENCION ALTERNA (ZUG) SOBRE ESTE ACUMULADOR (MEM) SE TRANSMITEN […]

SISTEMA DE COMUNICACIONES PARA EJECUTAR TAREAS EN PARALELO MEDIANTE ORDENADORES PERSONALES, del 25 de Agosto de 2009, de UNIVERSIDAD DE CORDOBA: Sistema de comunicaciones para ejecutar tareas en paralelo mediante ordenadores personales.#Comprende un nodo maestro y una pluralidad de nodos […]

SISTEMA DE COMUNICACIONES PARA EJECUTAR TAREAS EN PARALELO MEDIANTE ORDENADORES PERSONALES, del 25 de Agosto de 2009, de UNIVERSIDAD DE CORDOBA: Sistema de comunicaciones para ejecutar tareas en paralelo mediante ordenadores personales.#Comprende un nodo maestro y una pluralidad de nodos […]