MODULO ELECTRONICO INTEGRADO CON LOGICA CENTRAL DUPLICADA Y ALIMENTACION DE FALLOS DEL HARDWARE CON FINES DE COMPROBACION.

Módulo (ICT) electrónico integrado con un número de conexiones (INP,

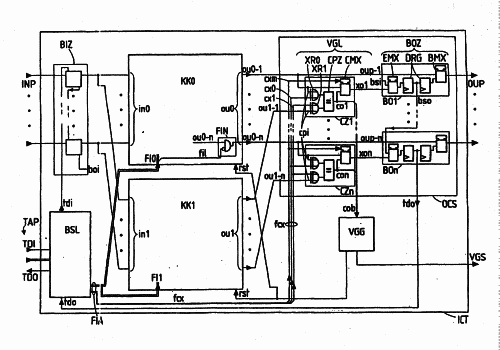

OUP), con - como mínimo dos circuitos (KK0, KK1) centrales del mismo tipo que pueden hacerse funcionar en un modo de funcionamiento sincrónico, así como con un dispositivo (VGL) de comparación al que se alimentan, por medio de entradas (cpi) de comprobación, las señales de salidas (ou0-1, ou1-1; ...; ou0-n, ou1-n) correspondientes entre sí de los circuitos (KK0, KK1) centrales para la comparación mutua, el cual agrupa las señales (co1-con) locales del resultado de la comparación, y el cual presenta una salida (vgs) del comparador para emitir una señal de fallo en el caso de una coincidencia insuficiente entre estas señales, - una alimentación (XR0, XR1) de fallos del hardware para la comprobación de cada grupo de salidas correspondientes entre sí de los circuitos centrales, con lo que como mínimo antes de una de las entradas (cpi) de comprobación del dispositivo local de comparación está conectada una alimentación (XR0, XR1) de fallos, la cual puede controlarse por como mínimo una entrada (cx0, cx1) de control de fallos, - una lógica de comprobación de la exploración periférica con un número de celdas (BO1, ..., BOn) de salida de la exploración periférica cuyas entradas (oup- 1, ..., oup-n) están conectadas en cada caso con una salida (ou0-1, ..., ou0-n) de uno de los circuitos centrales y cuyas salidas están conectadas con conexiones (OUP) conducidas fuera del módulo (ITC) como salidas de señales, así como - un medio (CMX) multiplexor controlado por la lógica de comprobación de exploración periférica, por medio del cual, para cada grupo de salidas correspondientes entre sí de los circuitos centrales, una señal (co1-con) local del resultado de la comparación, derivada al dispositivo (VGL) de comparación procedente de entradas (cpi) de comprobación, se alimenta a una celda (BO1-BOn) de salida de exploración periférica.

Tipo: Resumen de patente/invención.

Solicitante: SIEMENS AKTIENGESELLSCHAFT.

Nacionalidad solicitante: Alemania.

Dirección: WITTELSBACHERPLATZ 2,80333 MUNCHEN.

Inventor/es: GHAMESHLU, MAJID, KRAUSE, KARLHEINZ.

Fecha de Publicación: .

Fecha Solicitud PCT: 24 de Octubre de 2000.

Fecha Concesión Europea: 25 de Febrero de 2004.

Clasificación Internacional de Patentes:

- G06F11/00 FISICA. › G06 CALCULO; CONTEO. › G06F PROCESAMIENTO ELECTRICO DE DATOS DIGITALES (sistemas de computadores basados en modelos de cálculo específicos G06N). › Detección de errores; Corrección de errores; Monitorización (detección, corrección o monitorización de errores en el almacenamiento de información basado en el movimiento relativo entre el soporte de registro y el transductor G11B 20/18; monitorización, es decir, supervisión del progreso del registro o reproducción G11B 27/36; en memorias estáticas G11C 29/00).

Países PCT: Austria, Bélgica, Suiza, Alemania, Dinamarca, España, Francia, Reino Unido, Grecia, Italia, Liechtensein, Luxemburgo, Países Bajos, Suecia, Mónaco, Portugal, Irlanda, Finlandia, Chipre, Oficina Europea de Patentes.

Patentes similares o relacionadas:

Detección de daño de pantalla para dispositivos, del 8 de Julio de 2020, de Hyla, Inc: Un procedimiento para identificar una condición de una o más pantallas de un dispositivo electrónico, comprendiendo el procedimiento: recibir una solicitud […]

Sistema electrónico que comprende dispositivos electrónicos, disyuntor que comprende dicho sistema, procedimiento de generación de un indicador de desviación en caso de incompatibilidad entre dispositivos y producto de programa de ordenador asociado, del 15 de Enero de 2020, de SCHNEIDER ELECTRIC INDUSTRIES SAS: Sistema electrónico que comprende un conjunto de dispositivos (12A, 12B, 12C, 12D) electrónicos, comprendiendo cada dispositivo (12A, 12B, 12C, 12D) […]

UN MÉTODO Y UN DISPOSITIVO DE PROCESAMIENTO EN PARALELO DE INSTRUCCIONES DE PROGRAMA E INSTRUCCIONES DE TRAZA, del 26 de Septiembre de 2019, de UNIVERSIDAD POLITECNICA DE MADRID: Método y dispositivo de sincronización y ejecución paralela de instrucciones de traza sobre un procesador RISC segmentado. La invención consiste en un dispositivo cuya estructura […]

Sistema y método de calificación para el funcionamiento de plantas de agua helada, del 26 de Junio de 2019, de SIEMENS INDUSTRY, INC: Programa informático integrado en un medio tangible para determinar uno o más efectos de los cambios en una planta de agua helada, que consta […]

Sistema de ciberseguridad, del 29 de Mayo de 2019, de Ironnet Cybersecurity, Inc: Un sistema de ciberseguridad para procesar eventos para producir puntajes, alertas y acciones de mitigación, el sistema que comprende: una pluralidad de […]

Predicción, diagnóstico y recuperación de fallos de aplicaciones en base a patrones de acceso a recursos, del 1 de Mayo de 2019, de Microsoft Technology Licensing, LLC: Un procedimiento implementado por ordenador, para predecir una posible condición de error en un programa de aplicación que se ejecuta […]

PROCEDIMIENTO PARA CONTROL DE DISPOSITIVOS ELECTRODOMÉSTICOS E INSTALACIÓN PARA LLEVARLO A CABO, del 7 de Febrero de 2019, de NUBE PRINT, S.L: Procedimiento e instalación para el control de dispositivos electrodomésticos que emplea sólo los datos necesarios, evitando la saturación de las memorias de los elementos […]

UN MÉTODO Y UN DISPOSITIVO DE PROCESAMIENTO EN PARALELO DE INSTRUCCIONES DE PROGRAMA E INSTRUCCIONES DE TRAZA, del 24 de Enero de 2019, de UNIVERSIDAD POLITECNICA DE MADRID: Método y dispositivo de sincronización y ejecución paralela de instrucciones de traza sobre un procesador RISC segmentado. La invención consiste en un dispositivo cuya estructura […]