CELDA DE MEMORIA NO VOLATIL BORRABLE Y PROGRAMABLE ELECTRICAMENTE.

CELDA DE MEMORIA NO VOLATIL QUE PUEDE BORRARSE Y PROGRAMARSE ELECTRICAMENTE,

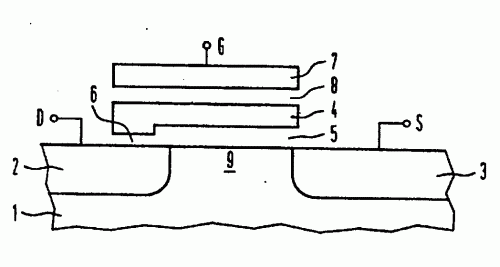

QUE ESTA FORMADA SOLO POR UN TRANSISTOR MOS FORMADO POR UN PASO FUENTE-CANAL-DRENAJE , EN LA QUE EN UN SUSTRATO SEMICONDUCTOR (1) DE UN PRIMER TIPO DE CONDUCTIBILIDAD SE HAN CONFORMADO UNA ZONA DE DRENAJE (2) Y UNA ZONA DE FUENTE (3) DE UN SEGUNDO TIPO DE CONDUCTIBILIDAD CON POLARIDAD OPUESTA, CON UN ELECTRODO DE PUERTA (4) QUE SE ENCUENTRA A UN POTENCIAL FLOTANTE Y QUE SE HA AISLADO ELECTRICAMENTE DE LA ZONA DE DRENAJE (2) MEDIANTE UN OXIDO DE TUNEL (5) Y DE UNA ZONA DE CANAL (9), QUE SE ENCUENTRA ENTRE LA ZONA DE DRENAJE Y LA DE FUENTE (2, 3), MEDIANTE UN OXIDO DE PUERTA (5 ; 10), EXTENDIENDOSE EN LA DIRECCION FUENTE-CANAL-DRENAJE AL MENOS POR UNA PARTE DE LA ZONA DE CANAL (9) Y UNA PARTE DE LA ZONA DE DRENAJE (2) Y ESTANDO AISLADO ELECTRICAMENTE DEL ELECTRODO DE PUERTA (4) MEDIANTE UN OXIDO DE ACOPLAMIENTO (8).

Tipo: Resumen de patente/invención.

Solicitante: SIEMENS AKTIENGESELLSCHAFT.

Nacionalidad solicitante: Alemania.

Dirección: WITTELSBACHERPLATZ 2,80333 MUNCHEN.

Inventor/es: TEMPEL, GEORG, WINNERL, JOSEF.

Fecha de Publicación: .

Fecha Solicitud PCT: 8 de Julio de 1996.

Fecha Concesión Europea: 28 de Abril de 1999.

Clasificación Internacional de Patentes:

- G11C16/04 FISICA. › G11 REGISTRO DE LA INFORMACION. › G11C MEMORIAS ESTATICAS (dispositivos semiconductores para memorias H01L, p. ej. H01L 27/108 - H01L 27/11597). › G11C 16/00 Memorias de sólo lectura programables y borrables (G11C 14/00 tiene prioridad). › utilizando transistores de umbral variable, p. ej. FAMOS.

- H01L29/788 ELECTRICIDAD. › H01 ELEMENTOS ELECTRICOS BASICOS. › H01L DISPOSITIVOS SEMICONDUCTORES; DISPOSITIVOS ELECTRICOS DE ESTADO SOLIDO NO PREVISTOS EN OTRO LUGAR (utilización de dispositivos semiconductores para medida G01; resistencias en general H01C; imanes, inductancias, transformadores H01F; condensadores en general H01G; dispositivos electrolíticos H01G 9/00; pilas, acumuladores H01M; guías de ondas, resonadores o líneas del tipo guía de ondas H01P; conectadores de líneas, colectores de corriente H01R; dispositivos de emisión estimulada H01S; resonadores electromecánicos H03H; altavoces, micrófonos, cabezas de lectura para gramófonos o transductores acústicos electromecánicos análogos H04R; fuentes de luz eléctricas en general H05B; circuitos impresos, circuitos híbridos, envolturas o detalles de construcción de aparatos eléctricos, fabricación de conjuntos de componentes eléctricos H05K; empleo de dispositivos semiconductores en circuitos que tienen una aplicación particular, ver la subclase relativa a la aplicación). › H01L 29/00 Dispositivos semiconductores adaptados a la rectificación, amplificación, generación de oscilaciones o a la conmutación que tienen al menos una barrera de potencial o de superficie; Condensadores o resistencias, que tienen al menos una barrera de potencial o de superficie, p. ej. unión PN, región de empobrecimiento, o región de concentración de portadores de carga; Detalles de cuerpos semiconductores o de sus electrodos (H01L 31/00 - H01L 47/00, H01L 51/05 tienen prioridad; otros detalles de los cuerpos semiconductores o de sus electrodos H01L 23/00; consistentes en una pluralidad de componentes de estado sólido formados en o sobre un sustrato común H01L 27/00). › de puerta flotante.

Países PCT: Austria, Suiza, Alemania, España, Francia, Reino Unido, Italia, Liechtensein, Oficina Europea de Patentes.

Patentes similares o relacionadas:

Memoria dinámica basada en un almacenamiento de un solo electrón, del 3 de Diciembre de 2014, de Conversant Intellectual Property Management Inc: Celda de memoria, que comprende:~ una región de canal situada entre una región de fuente y una región de drenaje , estando formadas dicha […]

Método de fabricación de un dispositivo de memoria de un solo electrón utilizando una máscara submicrónica, del 12 de Noviembre de 2014, de Conversant Intellectual Property Management Inc: Método de fabricación de un dispositivo de memoria de almacenamiento de carga, que comprende: formar una máscara submicrónica mediante las etapas […]

PROCEDIMIENTO PARA CODIFICAR POSICIONES DE ELEMENTOS DE DATOS EN UNA ESTRUCTURA DE DATOS, del 16 de Junio de 2007, de SIEMENS AKTIENGESELLSCHAFT: Procedimiento para codificar posiciones de elementos de datos en una estructura de datos, en el que a los elementos de datos se les asignan códigos de posición en una secuencia […]

METODO DE PROGRAMAR UN DISPOSITIVO SEMICONDUCTOR DE MEMORIA., del 16 de Noviembre de 2000, de INTERUNIVERSITAIR MICROELEKTRONICA CENTRUM VZW: SE PRESENTA UNA ESTRUCTURA DE CELDAS DE EEPROM PROGRAMABLE QUE CONSTA DE UNA ESTRUCTURA DE PUERTAS DIVIDIDAS EN SERIE CON UN CONDENSADOR DE ACOPLAMIENTO ENTRE LA PUERTA […]

ESTRUCTURA DE TRANSISTOR PARA UTILIZAR EN DISPOSITIVOS SEMICONDUCTORES DE MEMORIA BORRABLES Y PROGRAMABLES., del 16 de Febrero de 1997, de INTERUNIVERSITAIR MICROELEKTRONICA CENTRUM VZW: UNA ESTRUCTURA DE TRANSISTOR INCLUYENDO UN SUSTRATO SEMICONDUCTOR INCLUYENDO UNA REGION FUENTE, UN CANAL Y UNA REGION DE DRENAJE. UNA PUERTA MOVIL DE […]

Unidad Flash con forma para utilizar el espacio posterior de un dispositivo móvil, del 25 de Mayo de 2016, de Leef Innovation Ltd: Una unidad flash que proporciona almacenamiento digital expandido para un dispositivo electrónico portátil que permite que la unidad flash […]

Esquema de distribución con umbral multinivel flash, del 8 de Enero de 2014, de MOSAID TECHNOLOGIES INCORPORATED: Un dispositivo de memoria que comprende: Un arreglo de memoria que tiene celdas de memoria dispuestas en filas y columnas caracterizadas porque: cada celda de memoria […]

Método y dispositivo para mejorar la capacidad de escritura flash USB, del 2 de Octubre de 2013, de CYPRESS SEMICONDUCTOR CORPORATION: Un sistema de memoria que comprende: una memoria que requiere una operación de borrado antes de una operación de escritura, estando dicha […]