CIRCUITO DE SINCRONIZACION DE FASE.

SE DESCRIBE UN CIRCUITO DE SINCRONIZACION DE FASE QUE PUEDE UTILIZARSE EN SISTEMAS DIGITALES CON INESTABILIDAD EN LA FRECUENCIA DE LA SEÑAL DE RELOJ.

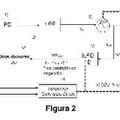

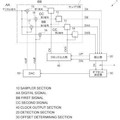

EL CIRCUITO TIENE UN OSCILADOR ANALOGICO (342) CUYA FRECUENCIA SE DETERMINA POR UNA SEÑAL DE CONTROL ANALOGICA. LA SEÑAL OSCILATORIA SE DIGITALIZA (344) Y COMPARA EN FASE (338) CON UNA SEÑAL DE REFERENCIA DIGITAL, CONVIRTIENDOSE LA SALIDA DIGITAL DEL COMPARADOR DE FASE (340) EN UNA SEÑAL ANALOGICA QUE SUMINISTRA LA SEÑAL DE CONTROL DE OSCILADOR. EN LA APLICACION DEL INVENTO A UN RECEPTOR DIGITAL DE TELEVISION QUE TIENE UN RELOJ DE BLOQUEO DE LINEA, EL CIRCUITO DE SINCRONIZACION DE FASE (350) REGENERA DOS SEÑALES DE SUBPORTADORA (COS,SIN) EN CUADRATURA DE FASE, QUE SE UTILIZAN PARA DESMODULAR SINCRONICAMENTE LOS COMPONENTES DE LA SEÑAL DE CROMINANCIA (CB) DE LAS SEÑALES COMPUESTAS DE VIDEO EN DOS SEÑALES DE INFORMACION DE COLOR (I,Q). EL OSCILADOR ANALOGICO DE VOLTAJE CONTROLADO (342) DEL CIRCUITO DE SINCRONIZACION DE FASE (350) GENERA UNA SEÑAL INDEPENDIENTE DE CUALQUIER INESTABILIDAD DE FRECUENCIA EN LA SEÑAL DE RELOJ DE BLOQUEO DE LINEA. EL CONVERTIDOR ANALOGICO-DIGITAL (344) DIGITALIZA ESTA SEÑAL PARA OBTENER UNA DE LAS SEÑALES DE SUBPORTADORA DE LA QUE SE GENERA LA SEÑAL EN CUADRATURA, POR EJEMPLO DE UNA MEMORIA ROM (348). LAS DOS SEÑALES DE INFORMACION DE COLOR (I,Q) SE OBTIENEN MULTIPLICANDO (332,334) LAS SEÑALES DE CROMINANCIA POR LA PRIMERA Y SEGUNDA SEÑALES SUBPORTADORAS. EL COMPARADOR DE FASE (336) DETERMINA LA FASE DEL VECTOR SUMA DE LAS DOS SEÑALES DE INFORMACION DE COLOR Y LA COMPARA CON UN VALOR DESEADO DE FASE A FIN DE GENERAR UNA SEÑAL DE DIFERENCIA DE FASE. ESTA SE FILTRA (338) Y SE APLICA AL CONVERTIDOR DIGITAL-ANALOGICO (340), EL CUAL PROPORCIONA LA SEÑAL DE CONTROL DE FRECUENCIA PARA EL OSCILADOR ANALOGICO (342). UN FILTRO DE SEGUIMIENTO (346) PUEDE INSERTARSE EN EL PUERTO DE SALIDA DEL CONVERTIDOR ANALOGICO-DIGITAL (344) PARA POSIBILITAR QUE SU RESOLUCION DE CUANTIFICACION SE REDUZCA SIN QUE SE VEA AFECTADO EL FUNCIONAMIENTO DEL CIRCUITO DE SINCRONIZACION DE FASE.

Tipo: Resumen de patente/invención.

Solicitante: RCA THOMSON LICENSING CORPORATION.

Nacionalidad solicitante: Estados Unidos de América.

Dirección: 2 INDEPENDENCE WAY, PRINCETON NEW JERSEY 08540.

Inventor/es: PATEL, CHANDRAKANT, BHAILALBHAI, DEMMER, WALTER HEINRICH, HARWOOD, LEOPOLD ALBERT, BALABAN, ALVIN REUBEN.

Fecha de Publicación: .

Fecha Concesión Europea: 21 de Julio de 1993.

Clasificación Internacional de Patentes:

- H03L7/08 ELECTRICIDAD. › H03 CIRCUITOS ELECTRONICOS BASICOS. › H03L CONTROL AUTOMATICO, ARRANQUE, SINCRONIZACION O ESTABILIZACION DE GENERADORES DE OSCILACIONES O DE IMPULSOS ELECTRONICOS (de generadores dinamoeléctricos H02P). › H03L 7/00 Control automático de frecuencia o fase; Sincronización (sintonización de circuitos resonantes en general H03J; sincronización en los sistemas de comunicación digital, ver los grupos apropiados en la clase H04). › Detalles del bucle cerrado en fase.

- H04N9/45 H […] › H04 TECNICA DE LAS COMUNICACIONES ELECTRICAS. › H04N TRANSMISION DE IMAGENES, p. ej. TELEVISION. › H04N 9/00 Detalles de los sistemas de televisión en color. › Generación o recuperación de las subportadoras de color.

- H04N9/455 H04N 9/00 […] › Generación de señales de sincronización cromática; Inserción o separación de las señales de sincronización cromática en las señales de imagen en color (H04N 9/45 tiene prioridad).

- H04N9/89 H04N 9/00 […] › Compensación del error de la base de tiempos.

Patentes similares o relacionadas:

Linealizador de forma de onda, del 12 de Junio de 2019, de MBDA UK LIMITED: Una fuente de barrido de frecuencia para un radar FMCW que comprende un sintetizador de frecuencia de bucle de bloqueo de fase, incluyendo el bucle bloqueado […]

Circuito de generación de reloj y procedimiento de generación de la señal de reloj, del 12 de Junio de 2019, de HUAWEI TECHNOLOGIES CO., LTD.: Un circuito de generación de reloj , que comprende una primera fuente de reloj , una segunda fuente de reloj y un circuito de puerta lógica , […]

Potencia programable para una interfaz de memoria, del 21 de Mayo de 2019, de QUALCOMM INCORPORATED: Un procedimiento para el control de retardo en una interfaz de memoria, que comprende: proporcionar una polarización de voltaje a un circuito […]

Sistema de bloqueo y procedimiento del mismo, del 25 de Febrero de 2015, de ZTE CORPORATION: Sistema de bloqueo, caracterizado por comprender una unidad de discriminación y conversión de fase digital, una unidad de filtro del bucle digital y una unidad de oscilación […]

Procedimiento, circuito de mando de bus CAN y sistema bus CAN para la recuperación de una frecuencia de pulso de reloj de un bus CAN, del 15 de Enero de 2014, de ROBERT BOSCH GMBH: Procedimiento para la recuperación de una frecuencia de pulso de reloj (T) de un bus CAN con un dispositivomaestro con un generador […]

SINTETIZADOR DE FRECUENCIA Y DIVISOR DE FRECUENCIA POR D BASADO EN LA TOPOLOGÍA DE ENGANCHE POR INYECCIÓN, del 1 de Marzo de 2013, de UNIVERSITAT POLITECNICA DE CATALUNYA: Sintetizador de frecuencia y divisor de frecuencia por D basado en la topología de enganche por inyección.

El sintetizador comprende:

- un […]

SINTETIZADOR DE FRECUENCIA Y DIVISOR DE FRECUENCIA POR D BASADO EN LA TOPOLOGÍA DE ENGANCHE POR INYECCIÓN, del 1 de Marzo de 2013, de UNIVERSITAT POLITECNICA DE CATALUNYA: Sintetizador de frecuencia y divisor de frecuencia por D basado en la topología de enganche por inyección.

El sintetizador comprende:

- un […]

Dispositivo de recuperación de datos de reloj, del 30 de Enero de 2013, de Thine Electronics, Inc: Un dispositivo de recuperación de reloj / datos para recuperar una señal de reloj y datos, en base a una señal digital de entrada, que comprende:

un muestreador […]

Dispositivo de recuperación de datos de reloj, del 30 de Enero de 2013, de Thine Electronics, Inc: Un dispositivo de recuperación de reloj / datos para recuperar una señal de reloj y datos, en base a una señal digital de entrada, que comprende:

un muestreador […]

CALIBRACION DEL ANCHO DE BANDA PARA UN BUCLE BLOQUEADO EN FRECUENCIA., del 16 de Marzo de 2006, de TELEFONAKTIEBOLAGET L M ERICSSON (PUBL): Un método para calibrar un bucle bloqueado o fijado en frecuencia, que está destinado a filtrar una señal de referencia extraída de una red de transporte para utilizarla […]