SINTETIZADOR DE FRECUENCIA DE BAJO RUIDO QUE UTILIZA DIVISORES DE NUMEROS SEMI-ENTEROS Y COMPENSACION DE GANANCIA ANALOGICA.

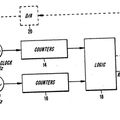

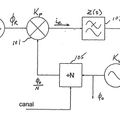

UN SINTETIZADOR 10 DE FRECUENCIAS DE BAJO RUIDO, QUE USA DIVISORES 13,

15 DE FRECUENCIAS, POR LO MENOS UNO DE LOS CUALES (DIVISOR 15) PUEDE INCREMENTARSE Y DISMIUIRSE EN PASO DE SEMIENTEROS, Y COMPENSACION DE GANANCIA ANALOGICA EN UN DETECTOR 17 DE FASE/FRECUENCIA, PARA OBTENER BAJO RUIDO, NIVELES ESPURIOS INFERIORES Y VELOCIDAD DE CONMUTACION MAS RAPIDA QUE LOS METODOS TRADICIONALES DE SINTESIS DE FRECUENCIAS. LAS CARACTERISTICAS PRINCIPALES DE LA PRESENTE INVENCION SON LOS DIVISORES 13, 15 SEMIENTEROS Y LA FACULTAD DE AJUSTAR LA GANANCIA DEL DETECTOR DE FASES PARA COMPENSAR EL BUCLE POR VARIAR LOS NUMEROS DIVISORES. EL SINTETIZADOR 10 COMPRENDE DOS DIVISORES 13, 15, QUE PROPORCIONAN DOS SEÑALES DE FRECUENCIA DE REFERENCIA, QUE SON UNA FUNCION DE UNA SEÑAL DE ENTRADA Y UNA SEÑAL DE SALIDA DEL SINTETIZADOR 10. UN OSCILADOR CON REGULACION DE VOLTAJE (VCO) 18 PROPORCIONA LA SEÑAL DE SALIDA (FO) DEL SINTETIZADOR 10 DE FRECUENCIAS. UN DETECTOR 17 DE FASE/FRECUENCIA COMPARA LAS SEÑALES DE LA FRECUENCIA DE REFERENCIA Y PROPORCIONA UNA SEÑAL DE SALIDA DE ERROR DE FASE O DEFASAJE, QUE ACCIONA EL VCO 18. UN CONTROLADOR DIGITAL, QUE COMPRENDE UNA PROM 11 (PROGRAMMABLE READ ONLY MEMORY NVERTIDOR 12 DIGITAL ANALOGICO, AJUSTA LA GANANCIA DEL DETECTOR 17 DE FASE PARA IGUALAR LA VARIACION DE LOS NUMEROS DIVISORES, Y SELECCIONA ESTOS. EL SINTERIZADOR 10 TIENE UN RUIDO DE FASE INFERIOR, NIVELES ESPURIOS INFERIORES Y CONMUTACION MAS RAPIDA DE CANALES DE FRECUENCIA. PARA GENERAR UNOS PASOS DE FRECUENCIA DE UN VALOR DADO, EL NUMERO DIVISOR ES LA MITAD DEL VALOR DE LOS PASOS. CON UN NUMERO DIVISOR QUE SEA LA MITAD DEL VALOR DE LOS PASOS, LA CONTRIBUCION DE RUIDO DESDE EL DIVISOR SE REDUCE EN ESA CUANTIA. EL MARGEN DE FASE SE PERFECCIONA CON UNA DISMINUCION CORRESPONDIENTE EN PICO DEL BUCLE, EN EL ESPECTRO DE RUIDOS. TAMBIEN SE DESCRIBE UN SISTEMA DE RADAR DE MISILES QUE EMPLEA EL PRESENTE SINTETIZADOR.

Tipo: Resumen de patente/invención.

Solicitante: RAYTHEON COMPANY.

Nacionalidad solicitante: Estados Unidos de América.

Dirección: PO BOX 902, 2000 EL SEGUNDO BLVD., EL SEGUNDO, CALIFORNIA 90245.

Inventor/es: ARNOLD, KEITH P., BLUMKE, JOEL C.

Fecha de Publicación: .

Fecha Concesión Europea: 10 de Noviembre de 2004.

Clasificación Internacional de Patentes:

- H03L7/197 ELECTRICIDAD. › H03 CIRCUITOS ELECTRONICOS BASICOS. › H03L CONTROL AUTOMATICO, ARRANQUE, SINCRONIZACION O ESTABILIZACION DE GENERADORES DE OSCILACIONES O DE IMPULSOS ELECTRONICOS (de generadores dinamoeléctricos H02P). › H03L 7/00 Control automático de frecuencia o fase; Sincronización (sintonización de circuitos resonantes en general H03J; sincronización en los sistemas de comunicación digital, ver los grupos apropiados en la clase H04). › siendo utilizada una diferencia de tiempos para enclavar el bucle, y contando el contador entre dos números variables en el tiempo o dividiendo el divisor de frecuencia por un factor variable en el tiempo, p. ej. para obtener una división de frecuencia fraccionaria.

Patentes similares o relacionadas:

Convertidor de fase a digital en bucle de bloqueo de fase totalmente digital, del 3 de Junio de 2020, de QUALCOMM INCORPORATED: Un procedimiento de conversión de fase a digital, comprendiendo el procedimiento: recibir por medio de un multiplexor de selección de ruta […]

Sintetizador, del 13 de Marzo de 2019, de MITSUBISHI ELECTRIC CORPORATION: Sintetizador que comprende un sintetizador de ajuste aproximado y un sintetizador de ajuste preciso, en el que el sintetizador de ajuste aproximado […]

METODO Y SISTEMA PARA REDUCIR LAS FLUCTUACIONES DE UNA ESTRUCTURA DE PLL (BUCLE DE ENGANCHE DE FASE) CARACTERIZADA POR UNA RAZON RACIONAL ENTRE LAS FRECUENCIAS DE ENTRADA Y SALIDA., del 1 de Abril de 1998, de ALCATEL ALSTHOM COMPAGNIE GENERALE D'ELECTRICITE: SE PRESENTA UN METODO DE CONTROL DE PLL EN QUE LA RAZON ENTRE LA FRECUENCIA DE SALIDA Y LA DE ENTRADA ES UN NUMERO RACIONAL. SE CARACTERIZA POR LA PRESENCIA […]

SINTESIS FRACCIONAL-N DE ACUMULADORES ENGANCHADOS CON REDUCCION DE ERROR RESIDUAL., del 16 de Febrero de 1997, de MOTOROLA, INC.: SINTESIS FRACCIONAL-N DE ACUMULADORES ENGANCHADOS CON REDUCCION DE ERROR RESIDUAL PARA SER UTILIZADO EN TRANSCEPTORES DE RADIO DIGITALES. SE DESCRIBE […]

SINTESIS FRACCIONAL-N DE ACUMULADORES MULTIPLES ENGANCHADOS., del 16 de Febrero de 1997, de MOTOROLA, INC.: SINTESIS FRACCIONAL-N DE ACUMULADORES MULTIPLES ENGANCHADOS PARA SER UTILIZADO EN TRANSCEPTORES DE RADIO DIGITALES. SE DESCRIBE UN SINTETIZADOR […]

"APARATO DIVISOR DE FRECUENCIA PROGRAMABLE", del 16 de Junio de 1994, de NIHON MUSEN KABUSHIKI KAISHA: APARATO DIVISOR DE FRECUENCIA PROGRAMABLE CON UNA RED DIVISORA DE FRECUENCIA CON VARIAS ETAPAS DIVISORAS DE FRECUENCIAS PROGRAMABLES CONECTADAS EN […]

METODO Y APARATO PARA REDUCIR LA CORRIENTE EN MODO DE ESPERA EN EQUIPOS DE COMUNICACIONES, del 16 de Septiembre de 2007, de TELEFONAKTIEBOLAGET L M ERICSSON (PUBL): ESTA INVENCION SE REFIERE A UN PROCEDIMIENTO Y A UN APARATO QUE SIRVEN PARA REDUCIR EL CONSUMO DE ENERGIA DE UN DISPOSITIVO DE COMUNICACIONES. EN MODO DE VIGILIA, […]

METODO Y APARATO PARA REDUCIR LA CORRIENTE EN MODO DE ESPERA EN EQUIPOS DE COMUNICACIONES, del 16 de Septiembre de 2007, de TELEFONAKTIEBOLAGET L M ERICSSON (PUBL): ESTA INVENCION SE REFIERE A UN PROCEDIMIENTO Y A UN APARATO QUE SIRVEN PARA REDUCIR EL CONSUMO DE ENERGIA DE UN DISPOSITIVO DE COMUNICACIONES. EN MODO DE VIGILIA, […]

DETECCION DE FASE DIGITAL, LINEAL, SIN BANDA MUERTA, del 1 de Julio de 2007, de TELEFONAKTIEBOLAGET LM ERICSSON (PUBL): Un bucle de bloqueo de fase fraccionario en N que comprende: un detector de fase que comprende: una primera entrada dispuesta para […]

DETECCION DE FASE DIGITAL, LINEAL, SIN BANDA MUERTA, del 1 de Julio de 2007, de TELEFONAKTIEBOLAGET LM ERICSSON (PUBL): Un bucle de bloqueo de fase fraccionario en N que comprende: un detector de fase que comprende: una primera entrada dispuesta para […]