Retícula de expansión de matriz.

Una matriz de conmutación que comprende:

(a) una multitud de matrices de conmutación de tres etapas (Nodo 1.

..Nodo Q); y

(b) una matriz de expansión (21), en la que una segunda etapa (B) de cada una de las matrices deconmutación de tres etapas (Nodo 1...Nodo Q) incluye una sección de expansión que comprendeconmutadores que facilitan la interconexión de cada matriz de tres etapas (Nodo 1...Nodo Q) a la matrizde conmutación de expansión (21);

(c) en la que cada una de la multitud de matrices de conmutación de tres etapas (Nodo 1...Nodo Q)comprende una matriz de primera etapa (A) que tiene N entradas y K salidas y una matriz de tercera etapa(C) que tiene K entradas y N salidas, cada matriz de segunda etapa (B) de cada matriz de conmutación detres etapas (Nodo 1...Nodo Q) que recibe M entradas locales de la matriz de primera etapa (A) y queproporciona M salidas locales a la matriz de conmutación de tercera etapa (C), cada matriz deconmutación de la segunda etapa (B) que además proporciona P salidas a la matriz de expansión (21) yque recibe P entradas desde la matriz de expansión (21), en las que K, N, M y P son enteros; y

(d) en la que la matriz de conmutación comprende una multitud de nodos y en la que, en cada nodo, hay Kmatrices de segunda etapa (B), M matrices de primera etapa (A) y M matrices de tercera etapa (C), y en laque el número de matrices de conmutación de expansión en la matriz de expansión (21) es igual a K x P.

Tipo: Patente Internacional (Tratado de Cooperación de Patentes). Resumen de patente/invención. Número de Solicitud: PCT/US2007/087604.

Solicitante: Wilson, Kevin.

Nacionalidad solicitante: Estados Unidos de América.

Dirección: 8200 Greenboro Drive Suite 1400 Mclean, VA 22102 ESTADOS UNIDOS DE AMERICA.

Inventor/es: WILSON,KEVIN, NGUYEN,NINH.

Fecha de Publicación: .

Clasificación Internacional de Patentes:

- H04Q3/00 ELECTRICIDAD. › H04 TECNICA DE LAS COMUNICACIONES ELECTRICAS. › H04Q SELECCION (conmutadores, relés, selectores H01H; redes de comunicación inalámbricas H04W). › Dispositivos de selección (H04Q 5/00 - H04Q 11/00 tienen prioridad).

PDF original: ES-2434765_T3.pdf

Fragmento de la descripción:

Retícula de expansión de matriz

Campo de la invención La presente invención se refiere en general a sistemas de conmutación de telecomunicaciones y más particularmente a una gran arquitectura de conmutación de conexión cruzada, rentable y eficiente.

Antecedentes de la invención Los sistemas de conexión cruzada digitales son una parte integral de la moderna red de transporte de telecomunicaciones de hoy. Se utilizan cada vez más por todos los proveedores de servicios, incluidos los operadores de central, los operadores de larga distancia y los operadores de derivación competitivos. Los avances tecnológicos significativos han permitido a los sistemas de conexión cruzada digital evolucionar de aplicaciones de prueba y preparación de banda estrecha a conexión cruzada de señales de red más grandes en banda ancha y dominios de frecuencia de banda ancha.

Se utiliza un sistema de banda ancha normalmente para terminar señales eléctricas y ópticas SONET de alta velocidad con el fin de terminar la ruta y preparar señales de banda ancha de velocidad más baja. El sistema de banda ancha también soporta la monitorización del rendimiento y las funciones de acceso de prueba. Típicamente los sistemas de banda ancha de conexión cruzada utilizan, o arquitectura de una sola etapa o arquitectura de matriz de Clos de tres etapas. En la arquitectura de matriz de tres etapas, la conexión cruzada incluye conmutadores agrupados en una etapa inicial, una etapa central y una etapa de terminación. La arquitectura de matriz de tres etapas es la más adecuada para aplicaciones de máxima capacidad para conexión cruzada de un gran volumen de señales. La arquitectura de matriz de una sola etapa organiza las matrices de una sola etapa en filas y columnas, lo que resulta en un mayor número de conmutaciones que en la arquitectura de tres etapas.

El documento “Adaptive Routing in High-Radix Clos Network”, John Kim et al, de noviembre de 2006, XP031044199 describe unas técnicas de enrutamiento adaptable en redes Clos para reducir la latencia y reducir la varianza en la latencia de los paquetes.

Compendio Si bien la arquitectura Clos de tres etapas ha sido un elemento básico de las matrices de conexión cruzada de alta capacidad, los inventores han reconocido una necesidad de matrices de capacidad incluso más alta. Las realizaciones configuradas según la invención facilitan proporcionar tal capacidad.

Se proporciona una matriz de conmutación que comprende: (a) un multitud de matrices de conmutación de tres etapas; y (b) una matriz de conmutación de expansión, en la que una segunda etapa de cada una de las matrices de conmutación de tres etapas incluye una sección de expansión que comprende conmutadores que facilitan la interconexión de cada matriz de tres etapas a la matriz de conmutación de expansión; (c) en la que cada una de la multitud de matrices de conmutación de tres etapas comprende una matriz de primera etapa que tiene N entradas y K salidas y una matriz de tercera etapa que tiene K entradas y N salidas, cada matriz de segunda etapa de cada matriz de conmutación de tres etapas recibe M entradas locales de la matriz de la primera etapa y proporciona M salidas locales a la matriz de conmutación de la tercera etapa, cada matriz de conmutación de la segunda etapa además proporciona P salidas a la matriz de expansión y recibe P entradas desde la matriz de expansión, en las que K, N, M y P son enteros; y (d) en la que la matriz de conmutación comprende una multitud de nodos y en la que, en cada nodo, hay K matrices de segunda etapa, M matrices de primera etapa y M matrices de tercera etapa y en la que el número de matrices de conmutación de expansión en la matriz de expansión es igual a K x P.

Una selección de las características opcionales de las reivindicaciones se expone en las reivindicaciones dependientes.

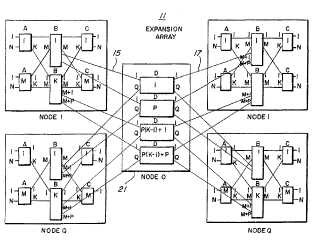

Descripción de los dibujos La Fig. 1 es un diagrama esquemático de una matriz de conmutación según una realización ilustrativa.

La Fig. 2 es un diagrama esquemático de una matriz de identificadores de conmutación según una realización ilustrativa.

La Fig. 3 es un diagrama de bloques de un procesador de ordenador y la memoria asociada según una realización ilustrativa.

La Fig. 4 es un diagrama de flujo de un proceso de selección del conmutador que emplea la realización ilustrativa.

Las Figs. 5 y 6 comprenden un diagrama esquemático del circuito de una matriz de 32 conmutadores según una realización ilustrativa.

Las Figs. 7 y 8 son diagramas de circuitos de los circuitos de control para los conmutadores de control tales como los descritos en las Figs. 5 y 6.

La Fig. 9 es una vista ampliada de uno de los conmutadores de la matriz mostrada en las Figs. 5 y 6.

Las Figs. 10 y 11 son diagramas de forma de onda útiles para ilustrar un método para controlar conmutadores de la 5 matriz de las Figs. 1 y 2 con un número reducido de controladores.

Descripción detallada La Fig. 1 ilustra una red 11 de matrices de conmutación según una realización ilustrativa. El sistema 11 de la Fig. 1 es un sistema relativamente grande que comprende una multitud de Nodos 1…Q y una Matriz de Expansión 21 también identificada como Nodo 0. En la Fig. 1, cada uno de los nodos, por ejemplo el Nodo 1, se dibuja dos veces,

una a la izquierda de la Matriz de Expansión 21 y otra a la derecha de la Matriz 21. Esta representación se emplea de manera que las interconexiones, por ejemplo, 15, 17, a la Matriz de Expansión desde el lado izquierdo y derecho de las matrices "B" en cada uno de los nodos no se superponen a otras partes del dibujo y por lo tanto se muestran más claramente.

Cada uno de los Nodos 1…Q tiene una estructura de tres etapas común formada por matrices de conmutación A, B

y C, interconectadas como se muestra. La Matriz de Expansión comprende una columna de “D” matrices de conmutación. Las matrices A, B, C y D se definen como sigue:

Una matriz de tipo A tiene N entradas y K salidas.

Una matriz de tipo B tiene M+P entradas y M+P salidas.

Una matriz de tipo C tiene K entradas y N salidas.

Una matriz de tipo D tiene Q entradas y Q salidas.

Además, con respecto a la topología de la Fig. 1, puede observarse que el Nodo 1 hasta el Q tienen sólo matrices de tipo A, B y C, mientras que el Nodo 0 sólo tiene matrices de tipo D. En cuanto al número de matrices, hay M matrices de tipo A en cada uno desde el nodo 1 hasta el nodo Q, hay K matrices de tipo B en cada uno desde el Nodo 1 hasta el Nodo Q, hay M matrices de tipo C en cada uno desde el nodo 1 hasta el nodo Q y hay R matrices de tipo D en el

Nodo 0 en el que R = K X P. Las diferentes matrices se pueden identificar como sigue:

A (m) denota una matriz m de tipo A en el nodo q donde m = 1…M; y q = 1…Q.

B (k) denota una matriz k de tipo B en el nodo q donde k = 1…K; y q = 1…Q.

C (m) denota una matriz m de tipo C en el nodo q donde m = 1…M; y q = 1…Q.

D (r) denota una matriz r de tipo D en el nodo 0 donde r = P (k-1) +p; k = 1…K; p = 1…P.

La interconexión de las respectivas matrices A, B, C y D se define como sigue:

1. La salida k de la matriz A (m) en el nodo q se conecta a la entrada m de la matriz B (k) en el mismo nodo q, donde m = 1…M y k = 1…K.

2. La salida m de la matriz B (k) en el nodo q se conecta a la entrada k de la matriz C (m) en el mismo nodo q, donde m = 1…M y k = 1…K.

3. La salida M+p de la matriz B (k) en el Nodo q se conecta a la entrada q de la matriz D (r=P (k-1) +p) en el Nodo 0, donde p = 1…P; k = 1…K; y q = 1…Q.

4. La salida q de la matriz D (r=P (k-1) +p) en el Nodo 0 se conecta a la entrada M+p de la matriz B (k) en el Nodo q, donde q = 1…Q; k = 1…K; y p = 1…P.

Por lo tanto, se observará que las salidas M+1…M+p en cada matriz del Nodo B izquierdo y las entradas M+1…M+p 40 en cada matriz del Nodo B derecho facilitan la implementación de las matrices tipo D de la Matriz de Expansión.

En la matriz de conmutación de la Fig. 1, un conmutador es un dispositivo que se puede activar para conectar una entrada a una salida de la misma matriz. Cada conmutador se representa mediante la notación S (nodo, tipo de matriz, número de matriz, entrada, salida) (S (node, array type, array number, input, output) ) . Por ejemplo, S (1, A, 2, 1, 3) denota el conmutador que conecta la entrada 1 a la salida 3 de la matriz 2 de tipo A en el nodo 1; S (0, D, 3, 2, 5) denota el conmutador que enlaza la entrada 2

con la entrada... [Seguir leyendo]

Reivindicaciones:

1. Una matriz de conmutación que comprende:

(a) una multitud de matrices de conmutación de tres etapas (Nodo 1…Nodo Q) ; y

(b) una matriz de expansión (21) , en la que una segunda etapa (B) de cada una de las matrices de

conmutación de tres etapas (Nodo 1…Nodo Q) incluye una sección de expansión que comprende conmutadores que facilitan la interconexión de cada matriz de tres etapas (Nodo 1…Nodo Q) a la matriz de conmutación de expansión (21) ;

(c) en la que cada una de la multitud de matrices de conmutación de tres etapas (Nodo 1…Nodo Q) comprende una matriz de primera etapa (A) que tiene N entradas y K salidas y una matriz de tercera etapa (C) que tiene K entradas y N salidas, cada matriz de segunda etapa (B) de cada matriz de conmutación de tres etapas (Nodo 1…Nodo Q) que recibe M entradas locales de la matriz de primera etapa (A) y que proporciona M salidas locales a la matriz de conmutación de tercera etapa (C) , cada matriz de conmutación de la segunda etapa (B) que además proporciona P salidas a la matriz de expansión (21) y que recibe P entradas desde la matriz de expansión (21) , en las que K, N, M y P son enteros; y

(d) en la que la matriz de conmutación comprende una multitud de nodos y en la que, en cada nodo, hay K matrices de segunda etapa (B) , M matrices de primera etapa (A) y M matrices de tercera etapa (C) , y en la que el número de matrices de conmutación de expansión en la matriz de expansión (21) es igual a K x P.

2. La matriz de conmutación de la reivindicación 1:

en la que la sección de expansión de cada matriz de segunda etapa (B) de cada matriz de conmutación de tres etapas (Nodo 1…Nodo Q) incluye un multitud de salidas de expansión, cada una conectada como una entrada a una respectiva matriz de conmutación de expansión (21) y en la que cada respectiva matriz de conmutación de expansión (21) proporciona una multitud de salidas de expansión, cada una conectada como un retorno de entrada a una respectiva matriz de conmutación de segunda etapa (B) .

3. La matriz de conmutación de la reivindicación 1 o 2 en la que cada matriz de conmutación de expansión (21) es 25 una matriz cuadrada (D) que tiene Q entradas y Q salidas, donde Q es un entero.

4. La matriz de conmutación de la reivindicación 1 o 2 en la que la matriz de expansión (21) comprende una sola columna de las matrices de conmutación cuadradas (D) .

5. La matriz de conmutación de la reivindicación 1 o 2 en la que la matriz de expansión (21) incluye una multitud de matrices cuadradas (D) , teniendo cada una Q entradas y Q salidas y en las que las segundas etapas (B) de

las matrices de tres etapas (Nodo 1…Nodo Q) incluyen cada una 1…M+1…M+P etapas verticales conectadas a las matrices cuadradas de la matriz de expansión (21) .

6. La matriz de conmutación de la reivindicación 4 en la que cada matriz cuadrada tiene Q entradas y Q salidas y en la que las segundas etapas de las matrices de tres etapas incluyen cada una 1…M+1…M+P etapas verticales que se conectan a las matrices cuadradas de la matriz de expansión.

Patentes similares o relacionadas:

Conmutador multidireccional, sistema de radiofrecuencia y dispositivo de comunicación inalámbrica, del 29 de Julio de 2020, de Guangdong OPPO Mobile Telecommunications Corp., Ltd: Un conmutador multidireccional , que comprende: doce puertos de dirección (T) y cuatro puertos de polo (P); los doce puertos T comprenden cuatro primeros puertos […]

Procedimiento y un dispositivo para asegurar una interfaz de sistema de señalización nº 7, del 6 de Mayo de 2020, de GSMK GESELLSCHAFT FUR SICHERE MOBILE KOMMUNIKATION MBH: Un procedimiento para asegurar una interfaz de sistema de señalización nº 7, interfaz SS7, de un sistema, a través de la cual tiene lugar un acceso a una […]

Transmisión de datos en una red IP con múltiples niveles de red central, del 28 de Agosto de 2019, de DEUTSCHE TELEKOM AG: Método para transmitir datos a través de una red IP con una red central que presenta una pluralidad de nodos de red (31 - 3n) y al menos dos niveles de red independientes […]

Transmisión de datos en una red IP con múltiples niveles de red central, del 28 de Agosto de 2019, de DEUTSCHE TELEKOM AG: Método para transmitir datos a través de una red IP con una red central que presenta una pluralidad de nodos de red (31 - 3n) y al menos dos niveles de red independientes […]

Método, sistema y dispositivo de procesamiento de paquetes, del 3 de Abril de 2019, de HUAWEI TECHNOLOGIES CO., LTD.: Un método de procesamiento de paquetes, que comprende: adquirir , mediante un dispositivo del lado de la red, una descripción de una aplicación y un estado de […]

Procesamiento de llamadas en redes de telecomunicaciones móviles, del 15 de Noviembre de 2018, de Orange: Un método de operación de una red de telefonía móvil, teniendo la red una pluralidad de plataformas para procesar una llamada, […]

Método y elemento para control de servicio, del 30 de Octubre de 2018, de Nokia Technologies OY: Un elemento de control de servicio que implementa una Funcion de Control de Sesion de Llamada de Servicio (SCSCFB), que comprende: medios […]

Sistema autónomo de sensor inalámbrico de antena, del 18 de Octubre de 2018, de Dalmazzo, Enzo: Un método para mantener la solidez de las infraestructuras de comunicaciones inalámbricas que comprende las etapas de: desplegar cerca de […]

Método y aparato para comunicar a través de extensiones telefónicas de oficina virtual, del 3 de Octubre de 2018, de BlackBerry Corporation: Un dispositivo de telecomunicación que comprende:

una unidad de conexión inalámbrica , dicha unidad de conexión inalámbrica para recibir […]

Método y aparato para comunicar a través de extensiones telefónicas de oficina virtual, del 3 de Octubre de 2018, de BlackBerry Corporation: Un dispositivo de telecomunicación que comprende:

una unidad de conexión inalámbrica , dicha unidad de conexión inalámbrica para recibir […]