Alimentación de corriente para un sistema electrónico.

Disposición compuesta de un circuito (11) operado o sincronizado a alta frecuencia,

en particular un microprocesador, circuitos de compensación de variaciones de corriente (10) dinámicas conectados en paralelo como regulador shunt al nivel de chip semiconductor del circuito integrado de la tensión de alimentación, una alimentación de corriente (14.1) del sistema electrónico para la alimentación del circuito integrado, de modo que se produce, dinámicamente, una compensación de variaciones de corriente en proximidad inmediata de los lugares de origen de las variaciones de corriente en el intervalo micrométrico al nivel de chip semiconductor, de modo que el circuito integrado no pueda inducir sobre las líneas de alimentación de corriente y en los condensadores de desacoplamiento del circuito integrado picos de tensión que menoscaben la operación segura del circuito integrado.

Tipo: Patente Internacional (Tratado de Cooperación de Patentes). Resumen de patente/invención. Número de Solicitud: PCT/DE2005/001831.

Solicitante: MK-ELEKTRONIK-GMBH.

Nacionalidad solicitante: Alemania.

Dirección: KIRCHDORFER STR. 1 87748 FELLHEIM ALEMANIA.

Inventor/es: KAUFMANN,MICHAEL.

Fecha de Publicación: .

Clasificación Internacional de Patentes:

- H02M3/335 ELECTRICIDAD. › H02 PRODUCCION, CONVERSION O DISTRIBUCION DE LA ENERGIA ELECTRICA. › H02M APARATOS PARA LA TRANSFORMACION DE CORRIENTE ALTERNA EN CORRIENTE ALTERNA, DE CORRIENTE ALTERNA EN CORRIENTE CONTINUA O DE CORRIENTE CONTINUA EN CORRIENTE CONTINUA Y UTILIZADOS CON LAS REDES DE DISTRIBUCION DE ENERGIA O SISTEMAS DE ALIMENTACION SIMILARES; TRANSFORMACION DE UNA POTENCIA DE ENTRADA EN CORRIENTE CONTINUA O ALTERNA EN UNA POTENCIA DE SALIDA DE CHOQUE; SU CONTROL O REGULACION (transformadores H01F; convertidores dinamoeléctricos H02K 47/00; control de los transformadores, reactancias o bobinas de choque, control o regulación de motores, generadores eléctricos o convertidores dinamoeléctricos H02P). › H02M 3/00 Transformación de una potencia de entrada en corriente continua en una potencia de salida en corriente continua. › utilizando solamente dispositivos semiconductores.

PDF original: ES-2378828_T3.pdf

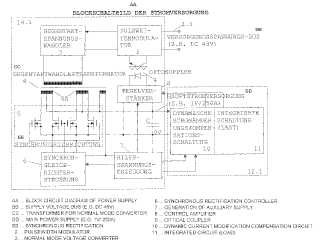

Fragmento de la descripción:

Alimentacion de corriente para un sistema electrónico La invención se refiere a una alimentación de corriente para un sistema electrónico de circuitos integrados electrónicos de alta frecuencia de trabajo. En las últimas décadas, la potencia de cálculo de los ordenadores se duplicó, cada vez, en promedio cada año y medio, de acuerdo con la "Ley de Moore". Este incremento de la potencia se ha conseguido gracias a estructuras de semiconductores cada vez más pequeñas, con el resultado de una cada vez mayor densidad de integración y, de este modo, un aumento constante de la frecuencia de reloj. Esto produjo para la alimentación de corriente de estos sistemas una reducción paulatina de la tensión de trabajo con el aumento correspondiente de la corriente de servicio. Adicionalmente, además, debido al aumento requerido de la precisión de regulación se incrementan, junto con la frecuencia de reloj, considerablemente los requerimientos dinámicos a la alimentación de corriente.

En los procesadores de alto rendimiento actuales que operan con una frecuencia de reloj de 2 a 3 GHz, aproximadamente, en el caso de variaciones dinámicas de la corriente de carga de 350 A/μs, aproximadamente, la tensión de trabajo no deberá sobreoscilar en más de ± 5 % (± 0, 05 a 0, 075 V, aproximadamente) para no menoscabar un funcionamiento impecable del procesador.

Con una longitud de las líneas conductoras de corriente de, por ejemplo, sólo 1, 5 cm, con 1 cm de anchura y una distancia entre conductores de 1, 5 mm (placa de circuito impreso a doble cara) se produce una inductancia de línea de 3 nH, aproximadamente. De este modo, ya una variación de corriente dinámica de 350 Aμs induce en la línea de alimentación de corriente picos de tensión de ± 1 V, aproximadamente, o sea ± 70 %, aproximadamente, de la tensión de trabajo a UB = 1, 5 V.

En el estado actual de la técnica se trata de solucionar estos requerimientos dinámicos mediante transformadores CC/CC de point-of-load de alta frecuencia de trabajo - en la variante actual como transformadores multifase de voltaje descendentes con rectificación sincrónica y control de fases y regulación digital - así como con un mayor número de condensadores de desacoplamiento distribuidos sobre la superficie del chip, minimizando un elevado número de contactos de alimentación de corriente distribuidos sobre todo el chip de memoria la inductancia de la línea de alimentación.

Para poder sustituir condensadores de desacoplamiento altamente capacitivos mediante un número reducido de condensadores pequeños con menor ESR y baja inductancia, también se usan circuitos DRC (Dynamic Load Transient Response Circuit) , por ejemplo, de la Cía. Ericsson o de acuerdo con la patente US 6.472.855 B2.

Pese a la aplicación de dichas técnicas, los esfuerzos para continuar aumentando la frecuencia de reloj se toparon con una límitación física (en las revistas profesionales ha sido expresada como un "problema de potencia") . La frecuencia de reloj de 15 GHz, predicha en diciembre de 2003 para el año 2005, parece inalcanzable a la luz del estado actual de la técnica. Mediante medidas de diseño adicionales a nivel de chip, como la arquitectura X, la división en varias zonas de alimentación de corriente conectadas con condensadores de desacoplamiento externos, y otras medidas se pudo alcanzar, en todo caso, una frecuencia de reloj de 4 GHz, aproximadamente, como frecuencia de corte superior, tampoco ya superable por medio de reducciones adicionales de estructuras.

Ni las frecuencias de corte de células de transistores superiores a 70 GHz, ya alcanzables mediante anchuras características de 90 nm, ni la posible evacuación térmica de calor de 1 kW/cm2 (a ΔT ≈ 5º C entre el chip y la temperatura de vapor) con enfriamiento por evaporación (por ejemplo, tubo termosifón bifásico) pueden ser agotadas al máximo de acuerdo con el estado actual de la técnica.

Los responsables de los fallos que ocasionan caídas de sistema incontrolables en el caso de superar las frecuencias de reloj posibles actualmente son los picos de la tensión de trabajo (transientes) proporcionales a la frecuencia de reloj y a la corriente de servicio, los cuales, pese al número relativamente grande de condensadores de desacoplamiento bondeados al chip superan, a partir de una frecuencia de reloj determinada, considerablemente, el intervalo de la tensión de trabajo todavía seguro de ± 10% o quedan, notablemente, por debajo del mismo. Son las variaciones dinámicas de la corriente de servicio causadas mediante las fluctuaciones de la paridad de bits (ruidos de paridad) dependientes del software y flujo de datos, con la frecuencia de reloj que genera dichos picos de tensión en la inductancia y ESR de los condensadores de desacoplamiento.

Ejemplo de cálculo con los datos operativos de un procesador típico, 1, 5 V de tensión de trabajo UB a 40 A de consumo de corriente, 2 GHz de frecuencia de reloj, 20 condensadores de desacoplamiento del tamaño 1210 (3, 2 x 2, 4 x 2, 5 mm) :

40A/20 → 2A/condensador → a 1% de ruido de corriente con 0, 25 ns de amplitud de impulso resulta una variación dinámica de la corriente de ± 0, 02A/0.25 ns ≈± 8 • 107 A/s en el condensador de desacoplamiento.

Con una distancia media de los condensadores de 2, 5 mm/2 + 0, 25 mm del chip es posible estimar la inductancia formada mediante el chip por medio de la fórmula LC = μ0⋅A/l:

Lc = .0•1, 5 mm•2, 5 mm/2, 5 mm ' 1, 9 nH

De este modo, la tensión inducida en esta inductancia por el ruido de corriente resulta ser:

± 8•107 A/s•1, 9 nH ' ± 0, 15 V

Este valor corresponde a los picos de tensión de trabajo de ± 10% UB apenas todavía admitidos para una operación sin fallos.

Para acentuar el problema es necesario agregar que con el aumento de la densidad de integración (de 130 nm → 90 nm → 65 nm → 45 nm de anchura característica, esta última correspondiente a la longitud de compuerta de C-MOS) la tensión de trabajo debe ser reducida de 2V a 0.9V con el aumento de la corriente de servicio, pudiendo apenas aumentar la cantidad de condensadores de desacoplamiento cuyos tamaños y distancias de chips no pueden ser reducidos. Esto explica la barrera considerada, generalmente, como "límite físico" para un aumento adicional de la frecuencia de reloj.

Por el documento US 6.310.792 B1 se conoce una fuente de alimentación para un sistema electrónico prevista para circuitos integrados operados a alta frecuencia o circuitos integrados sincronizados con compensación de variaciones dinámicas de corriente de servicio. Dicho documento se refiere a suministros de corriente point-of-load de acuerdo con el estado actual de la técnica, en los cuales los elementos para la estabilización dinámica de la tensión de trabajo están separados de los consumidores mediante líneas de conexión de longitud e inductancia insuficientes dados a conocer. Soluciones semejantes también se conocen de los documentos US 2003/039092 A1 y US 2004/174147 A1. El objetivo de la invención es eliminar estas desventajas directamente en el lugar de origen.

De conformidad con la invención, en una alimentación de corriente para sistemas electrónicos del tipo mencionado anteriormente, se consigue y alcanza dicho objetivo emplazando circuitos dinámicos de compensación de variaciones de corriente en la proximidad inmediata de los lugares de origen de las variaciones de corriente, por ejemplo en mecanismos de adición, memorias caché, drivers de bus de datos, entre otros, o integrándolos en el circuito integrado mismo.

El desplazamiento del mantenimiento constante dinámico de la tensión de trabajo (mediante circuitos de compensación de variación de corriente) desde el intervalo milimétrica de la placa de circuito impreso al intervalo micrométrico a nivel de chip semiconductor reduce la inductancia de la conducción de corriente hacia la carga (conexiones a consumidores de corriente) en el mismo factor de escala. De conformidad con la invención, a igual amplitud de tolerancia para los transientes de tensión de trabajo es posible incrementar, teóricamente, la frecuencia de reloj en el factor de escala recíproco.

De este modo, es posible realizar circuitos de compensación de variación de corriente sencillos, por ejemplo, con unos pocos transistores (integrador Miller) acoplados capacitivamente degenerativos por medio de la tensión de trabajo... [Seguir leyendo]

Reivindicaciones:

1. Disposición compuesta de un circuito (11) operado o sincronizado a alta frecuencia, en particular un microprocesador, circuitos de compensación de variaciones de corriente (10) dinámicas conectados en paralelo como regulador shunt al nivel de chip semiconductor del circuito integrado de la tensión de alimentación, una alimentación de corriente (14.1) del sistema electrónico para la alimentación del circuito integrado, de modo que se produce, dinámicamente, una compensación de variaciones de corriente en proximidad inmediata de los lugares de origen de las variaciones de corriente en el intervalo micrométrico al nivel de chip semiconductor, de modo que el circuito integrado no pueda inducir sobre las líneas de alimentación de corriente y en los condensadores de desacoplamiento del circuito integrado picos de tensión que menoscaben la operación segura del circuito integrado.

2. Disposición según la reivindicación 1, caracterizada porque el emplazamiento de la alimentación de corriente principal de baja tensión (14.2 con bloque de refrigeración 13) se realiza, directamente, encima del chip semiconductor (12.2) , de modo que se posibilitan conexiones acortadas de alimentación de corriente para la tensión de alimentación principal al chip semiconductor (12.2) y se prescinda del requerimiento de espacio separado sobre la placa de soporte para dicha alimentación de corriente.

3. Disposición según una de las reivindicaciones precedentes, caracterizada porque el chip semiconductor (12.2) y la alimentación de corriente principal de baja tensión (14.2) son enfriados por medio de un bloque de refrigeración común (13) , que sirve, adicionalmente, como parte mecánica de la alimentación de corriente principal de baja tensión (14.2) como alimentación de corriente al chip semiconductor (12.2) , y como soporte para sus condensadores de desacoplamiento (C) exteriores.

4. Disposición según una de las reivindicaciones precedentes, caracterizada porque la regulación de tensión de la modulación de duración de los impulsos (PWM) sobre la tensión de alimentación de corriente principal (14.1) que se realiza sobre el lado primario antes de la transformación ahorra convertidores de tensión de circuito intermedio de acuerdo con el estado actual de la técnica, y porque, claramente, aumenta el grado de eficacia y fiabilidad con la simultánea reducción considerable de los costes de fabricación.

5. Disposición según una de las reivindicaciones precedentes, caracterizada porque la inductancia de dispersión del transformador de convertidor de frecuencia en contrafase (4) se usa como inductancia de la memoria.

6. Disposición según una de las reivindicaciones precedentes, caracterizada porque la frecuencia de conmutación de los rectificadores sincrónicos es, correspondientemente a la frecuencia del convertidor en contrafase, 20 a 50 veces, aproximadamente, inferior que la frecuencia de modulación de la duración de impulsos del lado primario (múltiples veces mayor) , de modo que, respecto del estado actuali de la técnica, se generan en la rectificación sincrónica pérdidas por conmutación 20 a 50 veces menores.

7. Disposición según una de las reivindicaciones precedentes, caracterizada porque los arrollamientos secundarios en contrafase compuestos, cada uno, de un arrollamiento doble se colocan sobre los núcleos exteriores del transformador (4A) y se conectan en paralelo por medio del rectificador sincrónico (5) , hecho que respecto del estado actual de la técnica permite la reducción a la mitad del número de transistores del rectificador sincrónico (siempre que la carga de corriente sea igual que en el estado actual de la técnica) , con lo cual también se reducen a la mitad la necesidad de espacio y los costes y aumenta el grado de eficiencia, gracias a los semiconductores ahorrados.

8. Disposición según una de las reivindicaciones precedentes, caracterizada porque con el uso de los perfeccionamientos reivindicados bajo las reivindicaciones 2 a 7, inclusive, se posibilita, en sinergia, además del ahorro de espacio un sobredimensionamiento de la potencia (por encima del requerimiento de potencia del chip semiconductor 12.2) , para alimentar de corriente circuitos periféricos adicionales y ahorrar, de este modo, los convertidores de point-of-load necesarios según el estado actual de la técnica y sus requerimientos de espacio sobre la placa de soporte.

9. Disposición según una de las reivindicaciones precedentes, caracterizada porque, respecto del estado actual de la técnica, se reduce en 90 %, aproximadamente, el número de condensadores de desacoplamiento sobre el chip semiconductor y en los contactos de conducción de tensión de alimentación al chip semiconductor, pudiendo realizarse, adicionalmente, un incremento de la potencia en más del factor 10 mediante el aumento de la frecuencia de reloj.

10. Disposición según una de las reivindicaciones precedentes, caracterizada porque la arquitectura del chip está simplificada, lo cual produce una menor superficie de chip y, correspondientemente, un consumo de corriente menor.

Patentes similares o relacionadas:

Convertidor bidireccional de red de a bordo y procedimiento para su funcionamiento, del 1 de Julio de 2020, de Siemens Mobility GmbH: Convertidor bidireccional de red de a bordo con un lado de entrada para el suministro de una tensión de entrada externa, - con un primer tramo de […]

CONVERTIDOR DC/DC EN "L", del 25 de Junio de 2020, de POWER ELECTRONICS ESPAÑA, S.L: La presente invención se refiere a un circuito Convertidor DC/DC en "L" con varias configuraciones para obtener un convertidor tipo Boost (elevador) o tipo Buck […]

Inversor fotovoltaico con convertidores de retroceso conectados con entradas en paralelo y salidas en serie que alimentan un convertidor de red de puente completo, del 1 de Abril de 2020, de MARICI Holdings The Netherlands B.V: Un sistema de conversión de potencia que comprende: un primer convertidor que comprende un primer transformador con un devanado primario y un devanado […]

Fuente de alimentación inductiva adaptativa con comunicación, del 11 de Marzo de 2020, de Philips IP Ventures B.V: Fuente de alimentación sin contacto para proporcionar alimentación por inducción a al menos un dispositivo remoto , que comprende: - un […]

Adaptador y procedimiento de control de carga, del 26 de Febrero de 2020, de Guangdong OPPO Mobile Telecommunications Corp., Ltd: Un adaptador , que comprende: una unidad de conversión de potencia , configurada para convertir una corriente alterna (CA) de entrada para obtener un […]

Sistema de carga, método de carga y adaptador de potencia para terminal, del 19 de Febrero de 2020, de Guangdong OPPO Mobile Telecommunications Corp., Ltd: Un adaptador de potencia , que comprende: un primer circuito rectificador de puente completo , configurado para rectificar una […]

Dispositivo de control y método de control para controlar una carga, del 12 de Febrero de 2020, de Signify Holding B.V: Dispositivo de control para controlar una carga , que comprende: - terminales de entrada para conectar el dispositivo de control a […]

Fuente de alimentación de soldadura con característica de voltaje prolongado, del 5 de Febrero de 2020, de ESAB AB: Un aparato de fuente de alimentación de soldadura configurado para proporcionar potencia de soldadura de corriente continua (CC), que comprende: un componente […]