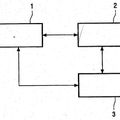

Circuito de muestreo digital para una señal de reloj secundaria que ha de monitorizarse en relación con un fallo de reloj con ayuda de una señal de reloj primaria.

Circuito de muestreo (100) digital para una señal de reloj secundaria (204) que ha de monitorizarse con ayuda de una señal de reloj primaria (202) en relación con un fallo de reloj

* con un biestable (102),

que presenta

- una entrada de reloj (108),

- una entrada de datos (106),

- una salida Q (110) y

- una entrada de reinicio asíncrona (112),

* y con un contador de n bits (104), que presenta

- una entrada de reloj (114),

- una entrada de reinicio asíncrona (128) y

- una salida de valor de recuento (116),

estando el biestable (102) y el contador de n bits (104) interconectados eléctricamente entre sí, y en el que * n ≥ 2,

* la señal de reloj primaria (202) se encuentra en la entrada de reloj (114) del contador de n bits (104),

* la señal de reloj secundaria (204) se encuentra en la entrada de reloj (108) del biestable (102),

* una señal constante se encuentra en la entrada de datos (106) del biestable (102),

* la salida Q (110) del biestable (102) está conectada con la entrada de reinicio (128) del contador de n bits (104), caracterizado porque

* la salida de valor de recuento (116) del contador de n bits (104) está conectada, a través de una puerta lógica (122) interpuesta y un lazo de realimentación (130), con la entrada de reinicio asíncrona (112) del biestable (102) de tal manera que un reinicio del contador de n bits (104) restablece el biestable (102).

Tipo: Patente Internacional (Tratado de Cooperación de Patentes). Resumen de patente/invención. Número de Solicitud: PCT/EP2013/058168.

Solicitante: AREVA GmbH.

Nacionalidad solicitante: Alemania.

Dirección: PAUL-GOSSEN-STRASSE 100 91052 ERLANGEN ALEMANIA.

Inventor/es: HEINEMANN, BERND, AUER,GÜNTHER.

Fecha de Publicación: .

Clasificación Internacional de Patentes:

- H03K21/40 ELECTRICIDAD. › H03 CIRCUITOS ELECTRONICOS BASICOS. › H03K TECNICA DE IMPULSO (medida de las características de los impulsos G01R; modulación de oscilaciones sinusoidales por impulsos H03C; transmisión de información digital, H04L; circuitos discriminadores de detección de diferencia de fase entre dos señales de conteo o integración de ciclos de oscilación H03D 3/04; control automático, arranque, sincronización o estabilización de generadores de oscilaciones o de impulsos electrónicos donde el tipo de generador es irrelevante o esta sin especificar H03L; codificación, decodificación o conversión de código, en general H03M). › H03K 21/00 Detalles de contadores de impulsos o de divisores de frecuencia. › Vigilancia; Detección de errores; Evitación o corrección del funcionamiento incorrecto del contador.

PDF original: ES-2594775_T3.pdf

Patentes similares o relacionadas:

Dispositivo y procedimiento de procesamiento de señales, del 8 de Febrero de 2019, de Korea Aerospace Research Institute: Un dispositivo de procesamiento de señales que recibe, de un sensor que mide una cantidad física y genera un valor acumulado o integrado […]

PROCEDIMIENTO Y DISPOSICION PARA EL FUNCIONAMIENTO DE UN CONTADOR DE ETAPAS MULTIPLES EN UN SENTIDO DE RECUENTO., del 16 de Febrero de 2005, de INFINEON TECHNOLOGIES AG: Procedimiento para el funcionamiento de un contador de etapas múltiples en un solo sentido de recuento, siendo modificado el valor de recuento de un […]

PROCEDIMIENTO Y DISPOSICION PARA EL FUNCIONAMIENTO DE UN CONTADOR DE ETAPAS MULTIPLES EN UN SENTIDO DE RECUENTO., del 16 de Septiembre de 2004, de INFINEON TECHNOLOGIES AG: Procedimiento para el funcionamiento de un contador de etapas múltiples en un solo sentido de recuento con las etapas: - modificación del valor […]

PROCEDIMIENTO PARA DESCUBRIR MANIPULACIONES EN UNA MEDIDA, REALIZADA CON UN EMISOR DE IMPULSOS, DE UN TRAYECTO RECORRIDO POR UN VEHICULO., del 16 de Diciembre de 2001, de MANNESMANN VDO AG: PARA EL RECONOCIMIENTO DE MANIPULACIONES EN LA MEDICION REALIZADA CON UN TRANSMISOR DE IMPULSO DE UN TRAYECTO CORRESPONDIENTE A UN VEHICULO, DONDE EL […]

CIRCUITERIA DE CONTADOR SINCRONO DE ALTA VELOCIDAD., del 16 de Octubre de 2001, de RAYTHEON COMPANY: LAS ETAPAS DEL REGISTRO CONTADOR DIGITAL RCR G(N) ESTAN CONSTRUIDAS COMO REGISTROS MUX DE DOS A UNO, QUE EMPLEA UNA ETAPA MULTIPLEXORA QUE TIENE TRES […]

CONTADOR NO VOLATIL., del 16 de Mayo de 1996, de HUGHES MICROELECTRONICS LIMITED: UN CONTADOR NO VOLATIL COMPUESTO POR: UN CONJUNTO DE CELULAS DE MEMORIA QUE INCORPORA GRUPOS 1 DE CELULAS, CADA GRUPO DE CELULAS 1 DIVIDIDO EN CADENAS DE PALABRA X, X' CAPACES […]

CONTADOR BINARIO CON ALMACENAMIENTO PERMUTADO, del 16 de Marzo de 2008, de NXP B.V.: Disposición para la realización de un contador binario para el decremento o incremento de una palabra de datos permutada parcialmente y almacenada en una memoria […]

CONTADOR BINARIO CON ALMACENAMIENTO PERMUTADO, del 16 de Marzo de 2008, de NXP B.V.: Disposición para la realización de un contador binario para el decremento o incremento de una palabra de datos permutada parcialmente y almacenada en una memoria […]