REGULACIÓN DE TENSIÓN DE SUB-DOMINIO DE PROCESADOR DE GRÁFICOS.

Regulación de tensión de sub-dominios de procesador suministrados por un mismo carril de alimentación de dominio de tensión.

La tensión a determinadas unidades lógicas en el interior del dominio de tensión puede reducirse en relación con otras unidades lógicas del dominio de tensión, reduciendo el tiempo de espera a alta potencia. En una realización, un primer sub-dominio de tensión regulada incluye por lo menos una unidad de ejecución (EU, execution unit) mientras que un segundo sub-dominio de tensión regulada incluye por lo menos un muestreador de texturas para proporcionar flexibilidad en el establecimiento del punto de potencia - rendimiento del núcleo de gráficos más allá de la modulación del recuento de EU activas a través de un control (de control por puerta) de dominio de potencia. En unas realizaciones, una tensión de sub-dominio se regula mediante un DLDO sobre placa para una conmutación de tensión rápida. La frecuencia de reloj y la tensión de sub-dominio pueden conmutarse más rápido que la tensión del carril de alimentación de dominio de tensión, permitiendo una gestión de potencia granulada de manera más fina que puede ser sensible a la demanda de carga de trabajo de EU.

Tipo: Patente de Invención. Resumen de patente/invención. Número de Solicitud: P201431706.

Solicitante: INTEL CORPORATION.

Nacionalidad solicitante: Estados Unidos de América.

Dirección: 2200 Mission College Blvd. 95054 Santa Clara CA -California ESTADOS UNIDOS DE AMERICA.

Inventor/es: MAIYURAN,Subramaniam, KHELLAH,Muhammad M, TSCHANZ,James W.

Fecha de Publicación: .

Clasificación Internacional de Patentes:

- G06F1/26 FISICA. › G06 CALCULO; CONTEO. › G06F PROCESAMIENTO ELECTRICO DE DATOS DIGITALES (sistemas de computadores basados en modelos de cálculo específicos G06N). › G06F 1/00 Detalles no cubiertos en los grupos G06F 3/00 - G06F 13/00 y G06F 21/00 (arquitecturas de computadores con programas almacenados de propósito general G06F 15/76). › Alimentación en energía eléctrica, p. ej. regulación a este efecto (para las memorias G11C).

Fragmento de la descripción:

Estado de la técnica

Un motor de gráficos, unidad de procesamiento de gráficos (GPU, graphics processing unit), o unidad de procesamiento visual (VPU, visual processing unit), es un circuito electrónico especializado diseñado para manipular y alterar con rapidez la memoria para acelerar la creación de imágenes en una memoria intermedia de tramas prevista por lo general para la emisión a un visualizador. Las GPU pueden encontrarse en sistemas embebidos, teléfonos móviles, tabletas, equipos informáticos portátiles ligeros, servidores de cálculo de alto rendimiento (HPC, high performance computation), y consolas de juegos. Además de manipular gráficos de ordenador en particular, una arquitectura sumamente paralela también posibilita que una GPU realice de forma más general el procesamiento de grandes bloques de datos en paralelo.

A pesar de que muchas de las actividades de procesamiento que se manejan por una GPU son intensivas en cuanto al cálculo, existe una necesidad creciente de unas arquitecturas de GPU energéticamente eficientes capaces de ajustar a escala el rendimiento / vatio no solo entre formatos (por ejemplo, servidor de HPC frente a un teléfono inteligente), sino también de manera dinámica dentro de un formato particular para manejar diferentes cargas de trabajo en instantes diferentes. Por ejemplo, en una aplicación de uso interactiva que se está ejecutando en un teléfono inteligente, tal como la apertura de un conjunto de fotos en respuesta a una acción de usuario, un nivel de potencia de una GPU embebida puede incrementarse (es decir, un modo turbo de gráficos) durante unos pocos milisegundos - segundos para proporcionar una percepción de rapidez al usuario. Un modo turbo de este tipo puede disipar una potencia significativamente más alta durante esta corta duración que a lo largo de unas cargas de trabajo sostenidas más prolongadas debido a que está limitada en general por la temperatura de unión. Dependiendo de la potencia de diseño térmico (TDP, thermal design power) para la plataforma dada, la disipación de potencia sostenida de GPU puede restringirse a no más de 1 - 2 W en un formato de tableta a modo de ejemplo, o unos pocos cientos de milivatios en un formato de teléfono inteligente. Además, los limitados recursos de batería de un dispositivo móvil pueden imponer unas limitaciones adicionales sobre la disipación de potencia para garantizar que el dispositivo pueda funcionar durante el tiempo más prolongado posible.

Son ventajosos las arquitecturas de procesador y los modos operativos que facilitan la gestión de potencia de una forma que puede potenciar el punto de potencia - rendimiento del procesador, mejorar la percepción del usuario del rendimiento, y ofrecer una mayor flexibilidad operativa.

Breve descripción de las figuras

El material que se describe en el presente documento se ilustra a modo de ejemplo y no a modo de limitación en las figuras adjuntas. Con fines de simplicidad y de claridad de ilustración, los elementos que se ilustran en las figuras no están dibujados necesariamente a escala. Por ejemplo, las dimensiones de algunos elementos pueden estar exageradas en relación con otros elementos con fines de claridad. Además, cuando se ha considerado apropiado, se han repetido etiquetas de referencia entre las figuras para indicar unos elementos correspondientes o análogos. En las figuras:

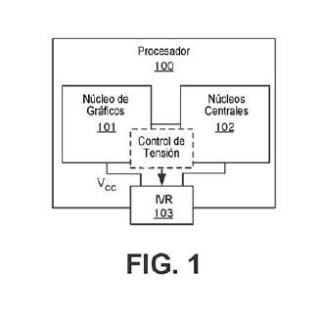

la figura 1 es un diagrama de bloques funcional que ilustra un procesador que emplea un núcleo de procesador de gráficos, un núcleo de procesador central, y un regulador de tensión integrado, de acuerdo con una realización;

la figura 2A es un diagrama de bloques funcional que ilustra una arquitectura de gestión de potencia de procesador de gráficos que emplea una regulación de tensión de sub-dominio, de acuerdo con una realización;

la figura 2B es un diagrama de bloques funcional que ilustra una arquitectura de gestión de potencia de procesador de gráficos que emplea una regulación de tensión de múltiples subdominios de tensión, de acuerdo con una realización;

la figura 3 es un diagrama de flujo que ilustra un método de gestión de potencia que emplea una regulación de tensión de múltiples sub-dominios, de acuerdo con una realización;

la figura 4 es una gráfica de potencia - rendimiento que ilustra un rendimiento de una arquitectura de procesador de gráficos que emplea una regulación de tensión de subdominio de acuerdo con una realización en comparación con dos arquitecturas de procesador alternativas;

la figura 5 es una gráfica de una tensión de dominio regulada y una tensión de sub-dominio regulada como una función del tiempo, de acuerdo con una realización;

la figura 6A es un diagrama esquemático de circuitos que ilustra una regulación de tensión de sub-dominio con un regulador de DLDO integrado, de acuerdo con una realización;

la figura 6B es un diagrama esquemático que ilustra un modelo de una arquitectura de regulación de tensión de sub-dominio que emplea un regulador de DLDO integrado, de acuerdo con una realización;

la figura 6C es un diagrama esquemático de circuitos que ilustra un modo de control por puerta de potencia de sub-dominio, de acuerdo con una realización;

la figura 7A es un diagrama de flujo que ilustra un método de gestión de potencia de procesador que emplea unos modos tanto de control por puerta de potencia como de regulación de tensión, de acuerdo con una realización;

la figura 7B es un diagrama de flujo que ilustra un método de gestión de potencia de procesador de gráficos que emplea unos modos tanto de control por puerta de potencia como de regulación de tensión en el interior del núcleo de procesador, de acuerdo con una realización;

la figura 8 representa de manera gráfica una tensión de dominio de núcleo de gráficos y unas tensiones de sub-dominio de núcleo cuando el método que se ilustra en la figura 7B se realiza de acuerdo con una realización;

las figuras 9A, 9B, 9C, y 9D son unos diagramas de bloques funcionales de unos núcleos de procesador de gráficos que ilustran una delimitación de sub-dominios de núcleo de procesador, de acuerdo con unas realizaciones;

la figura 10 es un diagrama ilustrativo de un sistema a modo de ejemplo, de acuerdo con una realización; y

la figura 11 es un diagrama ilustrativo de un sistema a modo de ejemplo, que está dispuesto de acuerdo con una realización.

Descripción detallada de realizaciones a modo de ejemplo

Una o más realizaciones se describen con referencia a las figuras adjuntas. A pesar de que se representan y se analizan con detalle unas configuraciones y disposiciones específicas, debe entenderse que esto se hace solo para fines ilustrativos. Los expertos en la materia relevante reconocerán que son posibles otras configuraciones y disposiciones sin alejarse del espíritu y el alcance de la descripción. Será evidente para los expertos en la materia relevante que las técnicas y / o disposiciones que se describen en el presente documento pueden emplearse en una diversidad de otros sistemas y aplicaciones más allá de lo que se describe con detalle en el presente documento.

En la siguiente descripción detallada se hace referencia a las figuras adjuntas, que forman una parte de esta e ilustran unas realizaciones a modo de ejemplo. Además, ha de entenderse que pueden utilizarse otras realizaciones y pueden hacerse cambios estructurales y / o lógicos sin alejarse del alcance de la materia objeto que se reivindica. Por lo tanto, la siguiente descripción detallada no ha de tomarse en un sentido limitante y el alcance de la materia objeto que se reivindica se define únicamente por las reivindicaciones adjuntas y sus equivalentes.

En la siguiente descripción, se exponen numerosos detalles, no obstante, será evidente para un experto en la materia, que pueden ponerse en práctica realizaciones sin estos detalles específicos. Se muestran en forma de diagrama de bloques unos métodos y dispositivos bien conocidos, en lugar de con detalle, para evitar complicar aspectos más significativos. Las referencias en la totalidad de la presente memoria descriptiva a "una realización" quieren decir que un rasgo distintivo, estructura, función, o característica particular que se describe en conexión con la realización está incluido en por lo menos una realización. Por lo tanto, las apariciones de la expresión "en una realización" o "en una realización" en diversos lugares en la totalidad de la presente memoria descriptiva no se están refiriendo necesariamente a la misma realización. Además, los rasgos distintivos, estructuras, funciones, o características particulares que se describen en el contexto de una realización pueden combinarse...

Reivindicaciones:

1.- Un núcleo de procesador de gráficos, que comprende:

un primer dominio de tensión acoplado con un carril de alimentación eléctrica accionable a una tensión de dominio;

un primer sub-dominio de tensión del primer dominio de tensión acoplado con el carril de alimentación eléctrica a través de una primera rama de alimentación, incluyendo el primer sub-dominio de tensión por lo menos uno o más muestreador de texturas; y

un segundo sub-dominio de tensión del primer dominio de tensión acoplado con el carril de alimentación eléctrica a través de una segunda rama de alimentación, incluyendo el segundo sub-dominio de tensión por lo menos una o más unidad de ejecución (EU), caracterizado por que:

por lo menos una de la primera y la segunda ramas de alimentación es accionable para convertir la tensión de dominio en sentido descendente hasta una tensión de sub-dominio que mantiene el muestreador o EU en un estado activo y de baja potencia.

2.- El núcleo de procesador de gráficos de la reivindicación 1, caracterizado por que la primera rama de alimentación comprende además un regulador de tensión accionable para proporcionar al primer sub-dominio de tensión una primera tensión de sub-dominio que es menor que una segunda tensión de sub-dominio que se proporciona al segundo sub-dominio de tensión.

3.- El núcleo de procesador de gráficos de la reivindicación 1, caracterizado por que la primera rama de alimentación comprende además un primer regulador de tensión accionable para proporcionar la primera tensión de sub-dominio, y caracterizado por que la segunda rama de alimentación comprende además un segundo regulador de tensión accionable para proporcionar al segundo sub-dominio de tensión una segunda tensión de sub-dominio menor que la tensión de dominio, y suficiente para mantener la EU en un estado activo.

4- El núcleo de procesador de gráficos de la reivindicación 1, caracterizado por que:

la tensión de dominio es modificable entre una tensión alta y una tensión baja;

la primera rama de alimentación comprende además un regulador de tensión accionable para convertir la tensión alta en sentido descendente hasta la tensión baja y para emitir la tensión baja al primer sub-dominio.

5.- El núcleo de procesador de gráficos de la reivindicación 1, caracterizado por que:

la tensión de dominio es modificable a una primera tasa entre una tensión alta y una tensión baja;

la primera rama de alimentación comprende además un regulador de tensión accionable para proporcionar la primera tensión de sub-dominio al primer sub-dominio de tensión; y

el regulador de tensión es accionable además para hacer que varíe la primera tensión de sub-dominio entre la tensión alta y la tensión baja a una segunda tasa que es mayor que la primera tasa.

6.- El núcleo de procesador de gráficos de la reivindicación 1, caracterizado por que por lo menos la segunda rama de alimentación comprende una pluralidad de transistores de potencia accionables en un modo de regulación de tensión para convertir la tensión de dominio a la tensión de sub-dominio reducida, y accionables además en un modo de control por puerta de potencia para desactivar por lo menos una de las EU.

7.- El núcleo de procesador de gráficos de la reivindicación 2, que comprende además: un controlador de tensión de sub-dominio; y

caracterizado por que el regulador de tensión comprende un regulador digital de baja diferencia mínima de tensión entre entrada y salida (DLDO) acoplado con el controlador de tensión de sub-dominio.

8.- El núcleo de procesador de gráficos de la reivindicación 2, que comprende además: un controlador de tensión de sub-dominio; y

caracterizado por que el regulador de tensión comprende un regulador digital de baja

diferencia mínima de tensión entre entrada y salida (DLDO) acoplado con el controlador de tensión de sub-dominio, comprendiendo además el regulador de DLDO:

un sensor de tensión;

una matriz de conmutación que incluye una pluralidad de transistores de potencia acoplados en paralelo a lo largo del carril de alimentación eléctrica y una salida del DLDO; y

un controlador de conmutador digital que tiene unas salidas acopladas con puertas de los transistores de potencia para hacer que varíe el número de transistores habilitados en la matriz de conmutación como una función de una salida del controlador de tensión de subdominio y una salida del DLDO que está acoplada con el sensor de tensión.

9.- El núcleo de procesador de gráficos de la reivindicación 2, que comprende además:

un controlador de tensión de sub-dominio sensible a un parámetro de rendimiento asociado con por lo menos uno del primer y el segundo sub-dominio; y

caracterizado por que el regulador de tensión comprende un regulador digital de baja diferencia mínima de tensión entre entrada y salida (DLDO) acoplado con el controlador de tensión de sub-dominio, comprendiendo además el regulador de DLDO:

una matriz de conmutación que incluye una pluralidad de transistores de potencia acoplados en paralelo a lo largo del carril de alimentación eléctrica y una salida del DLDO;

un comparador para comparar una salida del controlador de tensión de sub-dominio y la salida del DLDO; y

un controlador digital acoplado con puertas de los transistores para hacer que varíe el número de transistores habilitados en la matriz de conmutación sobre la base de una salida del comparador.

10.- El núcleo de procesador de gráficos de la reivindicación 1, caracterizado por que:

el primer sub-dominio de tensión incluye por lo menos el muestreador, una trazadora de exploración por líneas horizontales y una interfaz de memoria; y

el segundo sub-dominio de tensión incluye una pluralidad de EU y es exclusivo del muestreador, la trazadora de exploración por líneas horizontales y la interfaz de memoria.

11.- Un sistema de procesamiento, que comprende: un núcleo de procesador central;

un núcleo de procesador de gráficos; y

un primer regulador de tensión para proporcionar unos carriles de alimentación eléctrica tanto al núcleo de procesador central como al núcleo de procesador de gráficos, caracterizado por que el núcleo de procesador de gráficos comprende además:

un primer dominio de tensión acoplado para recibir una tensión de dominio a partir de uno o más de los carriles de alimentación eléctrica;

un primer sub-dominio de tensión acoplado con el uno o más carriles de alimentación eléctrica a través de una primera rama de alimentación, incluyendo el primer sub-dominio de tensión por lo menos un muestreador de texturas; y

un segundo sub-dominio de tensión acoplado con el uno o más carriles de alimentación eléctrica a través de una segunda rama de alimentación, incluyendo el segundo sub-dominio de tensión por lo menos una unidad de ejecución (EU), caracterizado por que:

por lo menos una de la primera y la segunda ramas de alimentación incluye un segundo regulador de tensión accionable para reducir la tensión de dominio a una tensión de sub- dominio que mantiene el muestreador o EU en un estado activo y de baja potencia.

12.- El sistema de la reivindicación 11, caracterizado por que la primera rama de alimentación comprende además el segundo regulador de tensión accionable para proporcionar la primera tensión de sub-dominio, y caracterizado por que la segunda rama de alimentación comprende además un tercer regulador de tensión accionable para proporcionar al segundo sub-dominio de tensión una segunda tensión de sub-dominio que es menor que la tensión de dominio, y mantiene la EU en un estado activo.

13.- El sistema de la reivindicación 12, caracterizado porque:

el primer sub-dominio de tensión incluye por lo menos el muestreador, una trazadora de exploración por líneas horizontales y una interfaz de memoria;

el segundo sub-dominio de tensión incluye una pluralidad de EU y es exclusivo del muestreador, la trazadora de exploración por líneas horizontales y la interfaz de memoria;

cada uno del segundo y el tercer reguladores de tensión comprende un regulador digital de baja diferencia mínima de tensión entre entrada y salida (DLDO).

14.- El sistema de la reivindicación 12, caracterizado por que cada regulador de DLDO comprende además:

un sensor de tensión;

una matriz de conmutación que incluye una pluralidad de transistores de potencia acoplados en paralelo a lo largo del carril de alimentación eléctrica y una salida del DLDO; y

un controlador de conmutador digital que tiene unas salidas acopladas con puertas de los transistores para hacer que varíe el número de transistores habilitados en la matriz de conmutación desde cero para realizar un control por puerta de potencia de un sub-dominio a más de cero para regular en tensión un sub-dominio como una función de la salida del DLDO acoplado con el sensor de tensión y una señal de control indicativa de una tensión de sub-dominio objetivo.

15.- Un método de gestionar un rendimiento de un núcleo de procesador de gráficos, comprendiendo el método:

suministrar una tensión de dominio a través de un carril de alimentación eléctrica acoplado con un dominio de tensión que incluye uno o más muestreador y una o más unidad de ejecución (EU);

supervisar la demanda de rendimiento sobre el núcleo de procesador de gráficos; y

regular una primera tensión de sub-dominio que se suministra a partir del carril y que se

proporciona al uno o más muestreador, sobre la base de la supervisión, para que esté por debajo de la tensión de dominio con independencia de una segunda tensión de sub-dominio que se suministra a partir del carril y que se proporciona a las una o más EU.

16.- El método de la reivindicación 15, que comprende además:

accionar la EU a una segunda tensión de sub-dominio que es igual a la tensión de dominio a la vez que se acciona el muestreador a la primera tensión de sub-dominio;

regular la segunda tensión de sub-dominio para que esté por debajo de la tensión de dominio; y

accionar la EU a la segunda tensión de sub-dominio reducida.

17.- El método de la reivindicación 16, que comprende además realizar ciclos de por lo menos la segunda tensión de sub-dominio entre la tensión de dominio y una tensión por debajo de la tensión de dominio para modular el rendimiento de la por lo menos una EU con independencia del por lo menos un muestreador.

18.- El método de la reivindicación 16, que comprende además aumentar la tensión de dominio desde una tensión baja hasta una tensión alta a una primera tasa antes de regular la segunda tensión de sub-dominio en sentido descendente desde la tensión alta hasta la tensión baja a una segunda tasa mayor que la primera tasa.

19.- El método de la reivindicación 16, que comprende además:

controlar una pluralidad de transistores de potencia en un modo de regulación de tensión para regular la tensión de dominio en sentido descendente hasta la segunda tensión de subdominio durante un primer periodo de tiempo; y

controlar uno o más de la pluralidad de transistores en un modo de control por puerta de potencia para desactivar por lo menos una de las EU.

20.- El método de la reivindicación 15, caracterizado por que regular una primera tensión de sub-dominio comprende además

recibir una señal de control de tensión de sub-dominio;

realizar una comparación de la señal de control de tensión de sub-dominio con la primera tensión de sub-dominio; y

accionar un controlador digital acoplado con puertas de los transistores para hacer que varíe, sobre la base de la comparación, un número de transistores de potencia habilitados acoplados en paralelo a lo largo del carril de alimentación eléctrica y un carril de salida acoplado con el primer sub-dominio.

21.- Un medio de almacenamiento legible por máquina que incluye unas instrucciones legibles por máquina, caracterizado por que en respuesta a su ejecución en un dispositivo de cálculo, dan lugar a que el dispositivo de cálculo gestione un rendimiento de un núcleo de procesador de gráficos mediante:

la supervisión de la demanda de rendimiento sobre el núcleo de procesador de gráficos; y

sobre la base de la supervisión, la regulación de una primera tensión de sub-dominio que se suministra a uno o más muestreador mediante un carril de alimentación eléctrica acoplado con un dominio de tensión que incluye el muestreador y una o más unidad de ejecución (EU) para que esté por debajo de la tensión de dominio con independencia de una segunda tensión de sub-dominio que se suministra a las una o más EU.

22.- El medio legible por máquina de la reivindicación 21, que comprende además unas instrucciones que en respuesta a su ejecución en el dispositivo de cálculo, dan lugar a que el dispositivo de cálculo gestione un rendimiento de un núcleo de procesador de gráficos mediante:

el accionamiento de la EU a una segunda tensión de sub-dominio que es igual a la tensión de dominio a la vez que se acciona el muestreador a la primera tensión de sub-dominio;

la regulación de la segunda tensión de sub-dominio para que esté por debajo de la tensión de dominio; y

el accionamiento de la EU a la segunda tensión de sub-dominio reducida.

Patentes similares o relacionadas:

Dispositivo de interfaz, procedimiento y programa informático para controlar dispositivos sensores, del 10 de Junio de 2020, de Ubiquiti Inc: Un primer dispositivo de interfaz para su uso en un sistema de domótica , comprendiendo el primer dispositivo de interfaz: un módulo de comunicación […]

Procedimiento para cargar una batería y dispositivo electrónico, del 29 de Abril de 2020, de SAMSUNG ELECTRONICS CO., LTD.: Un dispositivo electrónico que comprende: un conector al que se conecta un dispositivo externo ; un circuito de conversión de voltaje conectado […]

Detectores de encendido/apagado de múltiples voltajes de alimentación, del 25 de Marzo de 2020, de QUALCOMM INCORPORATED: Un dispositivo de múltiples voltajes de alimentación que comprende: una red central operativa a un primer voltaje de alimentación ; y una red de control […]

Dispositivos direccionables de IP auto-configurables que utilizan dos puertos de protocolo de internet de Ethernet, del 5 de Febrero de 2020, de Vertiv Corporation: Un método de monitorización y control de dispositivos direccionables de IP auto-configurables en un sistema de IP conectado, que comprende: conectar […]

Puerto de comunicaciones para dispositivos electrónicos con identificación y autentificación., del 15 de Enero de 2020, de SMARTCITY URBISENS, S.L: Puerto de comunicaciones para dispositivos electrónicos con identificación y autentificación. Constituido a partir de dos líneas de alimentación eléctrica, […]

Resonador acoplado en una cubierta posterior metálica, del 25 de Diciembre de 2019, de QUALCOMM INCORPORATED: Un dispositivo electrónico que comprende componentes electrónicos y una caja metálica (12, 42, 52, 62, 72, 82, […]

Resonador acoplado en una cubierta posterior metálica, del 25 de Diciembre de 2019, de QUALCOMM INCORPORATED: Un dispositivo electrónico que comprende componentes electrónicos y una caja metálica (12, 42, 52, 62, 72, 82, […]

Procedimiento para el bloqueo de una señal de activación, del 4 de Diciembre de 2019, de ROBERT BOSCH GMBH: Procedimiento para el bloqueo de un dispositivo de control que debe ser activado por una senal de activacion, el cual se realiza considerando la temperatura del dispositivo […]

Aparato y método para la gestión de la base de datos en un sistema de gestión de energía, del 20 de Noviembre de 2019, de LSIS Co., Ltd: Un sistema de gestión de energía que comprende un sistema de energía y un aparato de procesamiento de datos, el aparato de procesamiento de datos que comprende: […]