Convertir una interrupción señalada por mensaje en una notificación de evento de adaptador de I/O.

Un método de gestión de peticiones de interrupción en un entorno informático,

caracterizado por comprender los pasos de:

en respuesta a ejecutar una operación de interrupciones de registro de instrucción Modificar los Controles de Función de PCI (MPFC) que especifica un gestor de función de un adaptador, especificar (601) en una tabla localizada en un centro de entrada/salida (I/O) acoplado al adaptador, una ubicación en la memoria del sistema de un vector de bit de interrupción de adaptador (AIBV) del adaptador, el AIBV incluido en una formación de uno o más AIBV y una ubicación en la memoria del sistema de un bit de resumen de interrupción de adaptador (AISB) de una formación de AISB;

recibir (603) desde el adaptador una petición de interrupción; y

en respuesta a la petición recibida, fijar (605) por el centro de I/O un indicador en el AIBV que indica un tipo de evento desde el adaptador y fijar (606) el AISB que indica que un indicador está fijado en el AIBV.

Tipo: Patente Internacional (Tratado de Cooperación de Patentes). Resumen de patente/invención. Número de Solicitud: PCT/EP2010/067023.

Solicitante: INTERNATIONAL BUSINESS MACHINES CORPORATION.

Nacionalidad solicitante: Estados Unidos de América.

Dirección: NEW ORCHARD ROAD ARMONK, NY 10504 ESTADOS UNIDOS DE AMERICA.

Inventor/es: SITTMANN III,GUSTAV, FARRELL,Mark, CRADDOCK,DAVID, GREGG,THOMAS, LAIS,ERIC NORMAN, EASTON,JANET.

Fecha de Publicación: .

Clasificación Internacional de Patentes:

- G06F13/24 FISICA. › G06 CALCULO; CONTEO. › G06F PROCESAMIENTO ELECTRICO DE DATOS DIGITALES (sistemas de computadores basados en modelos de cálculo específicos G06N). › G06F 13/00 Interconexión o transferencia de información u otras señales entre memorias, dispositivos de entrada/salida o unidades de procesamiento (circuitos de interfaz para dispositivos de entrada/salida específicos G06F 3/00; sistemas multiprocesadores G06F 15/16). › utilizando la interrupción (G06F 13/32 tiene prioridad).

- G06F13/38 G06F 13/00 […] › Transferencia de informaciones, p. ej. sobre un bus (G06F 13/14 tiene prioridad).

- G06F9/48 G06F […] › G06F 9/00 Disposiciones para el control por programa, p. ej. unidades de control (control por programa para dispositivos periféricos G06F 13/10). › Inicio de programas; Conmutación de programas, p. ej. mediante una interrupción.

PDF original: ES-2535333_T3.pdf

Fragmento de la descripción:

Convertir una interrupción señalada por mensaje en una notificación de evento de adaptador de l/O Antecedentes

La invención se refiere, en general, a procesamiento de interrupciones dentro de un entorno informático y, en particular, a manejar interrupciones generadas por adaptadores del entorno informático.

Una interrupción señalada por mensaje (MSI) es una manera para que una función de adaptador, tal como una función de Interconexión de Componente Periférico (PCI), genere una interrupción de la unidad central de proceso (CPU) para informar al sistema operativo de la aparición de un evento o la presencia de algún estado. MSI es una alternativa a tener un pin de interrupción dedicado en cada dispositivo. Cuando una función de adaptador se configura para usar una MSI, la función solicita una interrupción realizando una operación de escritura de MSI de un número especificado de bytes de datos en una dirección especial. La combinación de esta dirección especial y un valor de datos único se denomina un vector de MSI.

Algunas funciones de adaptador soportan solamente un vector de MSI; otras funciones de adaptador soportan múltiples vectores de MSI. Para funciones que soportan múltiples vectores de MSI, la misma dirección especial se usa con diferentes valores de datos.

En muchas plataformas informáticas, un controlador de dispositivo se configura a sí mismo como el gestor de interrupciones asociado con un vector de MSI. Este asocia eficazmente un vector de MSI con una entrada en un vector de interrupción de CPU. Por lo tanto, cuando una función de adaptador soporta múltiples vectores de MSI y está configurada para usar múltiples vectores de MSI, consume un número correspondiente de entradas en el vector de interrupción de CPU.

La Publicación de EE.UU. N° 27/271559 A1, publicada el 22 de noviembre de 27, Easton et al., "Virtualization of Infiniband Host Channel Adapter Interruptions," describe un método, sistema, producto de programa y estructura de datos de ordenador para proporcionar dos niveles de virtualización de servidor. Un primer hipervisor habilita múltiples particiones lógicas para compartir un conjunto de recursos y proporciona un primer nivel de virtualización. Un segundo hipervisor habilita múltiples máquinas virtuales independientes para compartir los recursos que se asignan a una partición lógica única y proporciona un segundo nivel de virtualización. Todos los eventos para todas las máquinas virtuales dentro de dicha partición lógica única se agrupan en una cola única de evento propiedad de la partición para recibir notificaciones de evento desde los recursos compartidos para esa partición lógica única. Una petición de una interrupción se señala para los eventos agrupados desde la cola de evento propiedad de la partición para la demultiplexación de eventos agrupados, por la máquina, desde la cola de evento propiedad de la partición en colas de evento individuales, virtualizadas que se asignan sobre una base por máquina virtual.

La Publicación de EE UU. N° 25/289271 A1, publicada el 29 de diciembre de 25, Martínez et al., "Circuitry to Selectively Produce MSI Signáis," describe, en algunas realizaciones, que las invenciones incluyen un circuito integrado que tiene un circuito de registro de estado acoplado a conductores para recibir señales de evento de interrupción para proporcionar señales fuente que corresponden a las señales de evento de interrupción. El circuito integrado también incluye un circuito de registro de control para proporcionar señales de habilitación fuente para las selectivas de las fuentes de interrupción y un circuito de lógica de rearme acoplado a los conductores para recibir las señales de evento de interrupción y proporcionar una señal de rearme. El circuito integrado además incluye un primer circuito lógico para recibir las señales fuente, las señales de habilitación fuente y la señal de rearme para proporcionar una señal de interrupción inicial y la lógica de generación de pulso de señal de interrupción señalada por mensaje (MSI) para recibir la señal de interrupción inicial y proporcionar una señal de MSI en respuesta a la misma. Otras realizaciones se describen y reivindican.

La Patente de EE.UU. N° 7.562.366, expedida el 14 de julio de 29, Pope et al., "Transmit Completion Event Batching," describe un método para gestionar una cola de transmisión de datos, para uso con un ordenador principal y un dispositivo de interfaz de red. Descrita a grandes rasgos, el ordenador principal escribe descriptores de almacenador temporal de datos en una cola de descriptor de transmisión y el dispositivo de interfaz de red escribe eventos para notificar al ordenador principal cuándo ha completado el procesamiento de un almacenador temporal de datos de transmisión. Cada uno de los descriptores de evento de terminación de transmisión informa al ordenador principal de la terminación de una pluralidad de los almacenadores temporales de datos de transmisión.

"Chapter 6: Configuration Space" en: PCI-SIG: "PCI Local Bus Specification Revisión 3.", 3 de febrero de 24, XP2638677, páginas 213-254, describe un dispositivo de PCI que tiene una memoria que almacena un espacio de configuración.

La US 26/195617A1 (Arndt Richard L [US] et al), 31 de agosto de 26 describe el número de Función de Canal Principal-Dispositivo (BDF) bien conocido.

Breve compendio

Según un aspecto de la presente invención, se proporciona una capacidad para facilitar la gestión de peticiones de interrupción desde adaptadores.

Las deficiencias de la técnica anterior se superan y se proporcionan ventajas a través del suministro de un método según la reivindicación 1 y el sistema correspondiente y producto de programa de ordenador para gestionar peticiones de interrupción en un entorno informático.

Breve descripción de las diversas vistas de los dibujos

Uno o más aspectos de la presente invención se indican particularmente y reivindican distintivamente como ejemplos en las reivindicaciones en la conclusión de la especificación. Los precedentes y otros objetos, rasgos y ventajas de la invención serán evidentes a partir de la siguiente descripción detallada tomada en conjunto con los dibujos anexos en los cuales:

La FIG. 1 representa una realización de un entorno informático para incorporar y usar uno o más aspectos de la presente invención;

La FIG. 2 representa una realización de detalles adicionales de una memoria del sistema y el centro de l/O de la FIG. 1, según un aspecto de la presente invención;

Las FIG. 3A-3B representan ejemplos de asignaciones de vectores de bits de interrupción de adaptador, según un aspecto de la presente invención;

Las FIG. 3C-3D representan ejemplos de asignaciones de bits de resumen de interrupción de adaptador, según un aspecto de la presente invención;

La FIG. 4 representa una realización de una vista general de la lógica a ser realizada durante la inicialización para configurar una función de adaptador para notificación de evento de adaptador de l/O, según un aspecto de la presente invención;

La FIG. 5 representa una realización de la lógica para realizar un registro para permitir la conversión de una interrupción señalada por mensaje (MSI) en una notificación de evento de adaptador de l/O, según un aspecto de la presente invención;

La FIG. 6A representa una realización de la lógica para convertir una petición de MSI a una notificación de evento de adaptador de l/O, según un aspecto de la presente invención;

La FIG. 6B representa una realización de la lógica para presentar la notificación de evento de adaptador de l/O a un sistema operativo, según un aspecto de la presente invención;

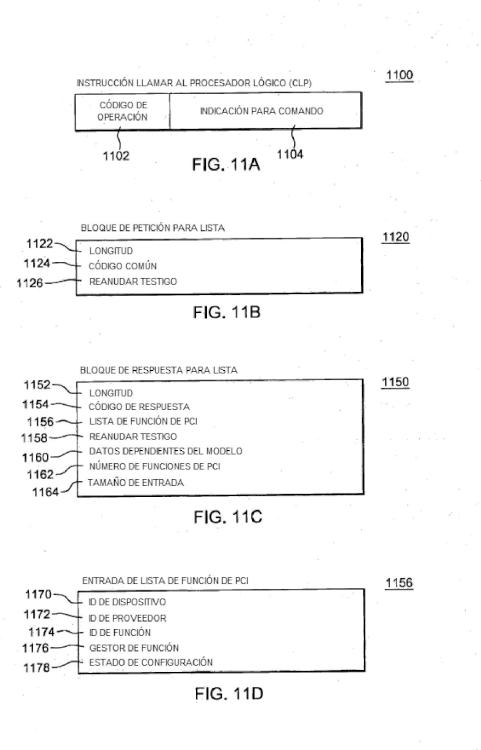

La FIG. 7A representa una realización de una instrucción Modificar los Controles de Función de PCI usada según un aspecto de la presente invención;

La FIG. 7B representa una realización de un campo usado por la instrucción Modificar los Controles de Función de PCI de la FIG. 7A, según un aspecto de la presente invención;

La FIG. 7C representa una realización de otro campo usado por la instrucción Modificar los Controles de Función de PCI de la FIG. 7A, según un aspecto de la presente invención;

La FIG. 7D representa una realización de los contenidos de un bloque de información de función (FIB) usado según un aspecto de la presente invención;

La FIG. 8 representa una realización de una vista general de la lógica de la instrucción Modificar los Controles de Función de PCI, según un aspecto de la presente invención;

La FIG. 9 representa una realización de la lógica asociada con una operación de interrupciones de adaptador... [Seguir leyendo]

Reivindicaciones:

1. Un método de gestión de peticiones de interrupción en un entorno informático, caracterizado por comprender los pasos de:

en respuesta a ejecutar una operación de interrupciones de registro de instrucción Modificar los Controles de Función de PCI (MPFC) que especifica un gestor de función de un adaptador, especificar (61) en una tabla localizada en un centro de entrada/salida (l/O) acoplado al adaptador, una ubicación en la memoria del sistema de un vector de bit de interrupción de adaptador (AIBV) del adaptador, el AIBV incluido en una formación de uno o más AIBV y una ubicación en la memoria del sistema de un bit de resumen de interrupción de adaptador (AISB) de una formación de AISB;

recibir (63) desde el adaptador una petición de interrupción; y

en respuesta a la petición recibida, fijar (65) por el centro de l/O un indicador en el AIBV que indica un tipo de evento desde el adaptador y fijar (66) el AISB que indica que un indicador está fijado en el AIBV.

2. El método de la reivindicación 1, en donde el método además comprende presentar una interrupción a un sistema operativo, la interrupción en respuesta a la petición de interrupción.

3. El método de la reivindicación 2, en donde la petición de interrupción representa una pluralidad de interrupciones señaladas por mensaje y la interrupción al sistema operativo es parte de una notificación de evento de adaptador de entrada/salida para el sistema operativo.

4. El método de la reivindicación 2, en donde el método además comprende obtener, en respuesta a la presentación, una o más indicaciones de AIBV para uno o más adaptadores especificando al menos una razón para la interrupción por adaptador.

5. El método de la reivindicación 4, en donde la obtención comprende obtener una pluralidad de indicaciones de AIBV que especifican una pluralidad de razones para la interrupción, la pluralidad de razones para la interrupción que corresponden a la pluralidad de peticiones de interrupción.

6. El método de la reivindicación 5, en donde la obtención comprende usar el AISB en la obtención de una o más indicaciones de AIBV en la una o más AIBV.

7. El método de la reivindicación 1, en donde el ajuste del indicador en el AIBV comprende:

usar un identificador de la petición desde el adaptador para obtener una entrada de tabla de dispositivo, la entrada de tabla de dispositivo que comprende un valor que especifica un número de interrupciones que se permiten para el adaptador;

determinar si un número de vector proporcionado en la petición está dentro del número de interrupciones permitidas para el adaptador;

en respuesta a determinar que el número de vector está dentro del número permitido de interrupciones, usar uno o más parámetros de la entrada de tabla de dispositivo para localizar una posición de inicio de la AIBV; y

usar el número de vector para fijar el indicador en el AIBV.

8. Un sistema que comprende medios adaptados para llevar a cabo todos los pasos del método según cualquier reivindicación del método precedente.

9. Un programa de ordenador que comprende instrucciones para llevar a cabo todos los pasos del método según cualquier reivindicación del método precedente, cuando dicho programa de ordenador se ejecuta en un sistema informático.

Patentes similares o relacionadas:

Dispositivo electrónico y procedimiento de realización de comunicación híbrida con dispositivo electrónico externo, del 3 de Junio de 2020, de SAMSUNG ELECTRONICS CO., LTD.: Un dispositivo electrónico que comprende: un primer circuito de comunicación que realiza comunicación inalámbrica utilizando un primer protocolo de comunicación; […]

Módulo de interfaz física, del 13 de Mayo de 2020, de NAGRAVISION S.A.: Un sistema en chip (SYS) que comprende un primer módulo (PER) y un segundo módulo (PROC), el primer módulo (PER) que comprende una primera interfaz física […]

Procedimiento, dispositivo y sistema para transferencia de paquetes en NVME sobre tejido, del 22 de Abril de 2020, de HUAWEI TECHNOLOGIES CO., LTD.: Un dispositivo de transferencia y procesamiento en memoria no volátil exprés sobre tejido, NVMe sobre tejido, en el que el dispositivo […]

Dispositivo de conmutación, sistema de interconexión de componentes periféricos rápida y procedimiento de inicialización del mismo, del 13 de Noviembre de 2019, de HUAWEI TECHNOLOGIES CO., LTD.: Un dispositivo de conmutación que comprende: múltiples puertos de Interconexión de Componentes Periféricos rápidos, PCIe, aguas arriba , […]

Método de desconexión de enlace entre un equipo PCIe y un concentrador y dispositivo que utiliza este último, del 14 de Agosto de 2019, de HUAWEI TECHNOLOGIES CO., LTD.: Un método para desconectar un enlace entre un dispositivo de Interconexión de Componente Periférico Exprés, PCIe, y un concentrador, en donde el dispositivo […]

Método y sistema para poner dispositivos funcionales a disposición de participantes de reuniones, del 4 de Julio de 2019, de BARCO N.V.: 1. Un sistema para conectar un dispositivo de procesamiento a un dispositivo funcional conectado a, o en, una unidad base de una red de comunicaciones, teniendo el dispositivo […]

Interfaz serie de capa de enlace a capa física (PHY), del 21 de Marzo de 2019, de QUALCOMM INCORPORATED: Un circuito integrado, IC, que comprende: un circuito de capa de enlace ; un puente de enlace acoplado operativamente al […]

Sistema informático y procedimiento para acceder a un dispositivo de punto extremo del mismo, del 20 de Marzo de 2019, de HUAWEI TECHNOLOGIES CO., LTD.: Un sistema informático , que comprende un subsistema informático y un subsistema de gestión , en el que el subsistema informático comprende una unidad de […]