Procedimiento y circuito para detección de bus y recuperación de sistema.

Circuito para detección y restablecimiento de actividad de bus para circuitos inter-integrados que comprende:

- medios ajustados manualmente (C2, B1, B2, Bn) para establecer una constante de tiempo que selecciona unvalor constante de tiempo de entre una pluralidad de diferentes valores de constante de tiempo dados (B1, B2,Bn);

- medios de detección (Q1, Q2, Q3, Q4) para detectar un estado de actividad o de inactividad en dicho bus,comprendiendo un circuito de entrada (Q1, Q2 y Q3) que determina un valor medio de corriente continua de unaseñal de datos en dicho bus de conexión de circuitos inter-integrados y un circuito de detección de actividad (Q4)que genera una salida de reposición cuando dicho valor medio de corriente continua, indica inactividad en dichobus para un tiempo definido por dicha constante de tiempo establecida, donde dicho circuito de entradacomprende:

- un circuito seguidor de emisor (Q1) que es utilizado como memoria intermedia de entrada;

- un bloque de medición de media que toma la media de corriente continua de la señal de datos;

- una memoria intermedia de salida (Q3) que pone en memoria intermedia e invierte la señal cuya media decorriente continua ha sido tomada, donde valores altos en un colector de transistor de dicha memoria intermediade salida (Q3) activan un diodo (D1) y cargan un condensador (C2); donde la carga y descarga de dichocondensador (C2) son dos funciones temporales con dicha constante de tiempo ajustada como parámetro;

- y donde dicho circuito de detección de actividad comprende un cuarto bloque que genera dicha salida dereposición como señal alta o baja de acuerdo con una tensión de dicho condensador (C2); y

- un puerto de salida de reposición para entregar como salida dicha señal de salida de reposición.

Tipo: Patente Europea. Resumen de patente/invención. Número de Solicitud: E08101530.

Solicitante: VESTEL ELEKTRONIK SANAYI VE TICARET A.S.

Nacionalidad solicitante: Turquía.

Dirección: ORGANIZE SANAYI BÖLGESI 45030 MANISA TURQUIA.

Inventor/es: CETIN,HUSEYIN ERTURK.

Fecha de Publicación: .

Clasificación Internacional de Patentes:

- G06F11/07 FISICA. › G06 CALCULO; CONTEO. › G06F PROCESAMIENTO ELECTRICO DE DATOS DIGITALES (sistemas de computadores basados en modelos de cálculo específicos G06N). › G06F 11/00 Detección de errores; Corrección de errores; Monitorización (detección, corrección o monitorización de errores en el almacenamiento de información basado en el movimiento relativo entre el soporte de registro y el transductor G11B 20/18; monitorización, es decir, supervisión del progreso del registro o reproducción G11B 27/36; en memorias estáticas G11C 29/00). › Respuesta ante la aparición de un defecto, p. ej. tolerancia ante fallos.

PDF original: ES-2410557_T3.pdf

Fragmento de la descripción:

Procedimiento y circuito para detección de bus y recuperación de sistema Ámbito de la técnica [0001] Esta invención se refiere a un procedimiento universal y a un circuito para la detección de actividad de bus y recuperación de sistema, particularmente para sistemas de micro-ordenadores con un bus de comunicación tales como un micro controlador de la placa madre de una televisión.

Estado de la técnica

Se utilizan marcas internas de registro para detectar la actividad de bus no solo en ordenadores, sino también en productos de electrónica de consumo. Por ejemplo, en un conjunto IDTV, la placa madre y la tarjeta de módulo DVB se comunican utilizando un transmisor-receptor asíncrono universal (UART) . En la misma placa madre, el micro-controlador y sus periféricos (sintonizador, procesador de video, etc.) se comunican utilizando un circuito inter-integrado (I2C) .

Cuando se utiliza un (UART) , el micro-controlador tiene una marca de registro dedicada para supervisar la comunicación (UART) . Si la comunicación falla, después de que el sistema haya sido restablecido o reiniciado, esta marca se repone y el micro-controlador se comporta de acuerdo a esta marca: restablecer el microcontrolador (DVB) , retransmitir el último dato, etc.

Cuando se utiliza (I2C) , el micro-controlador, como maestro, supervisa sus periféricos y los periféricos se comunican como esclavos los IC (circuitos integrados) . Si uno de los periféricos falla en responder al comando maestro, el maestro lo restablece.

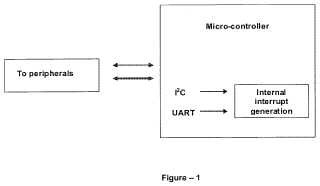

En ambos caso, se asume que el micro-controlador tiene un bloque/registro dedicado a supervisar el bus de comunicación, como puede verse en la figura 1.

Si el micro-controlador no tiene un parte dedicada (registro/bloque) para supervisar la actividad bus, el sistema no puede detectar el fallo de bus y tomar la acción correcta lo que provoca un colapso completo del sistema.

Además, también es posible que cuando la comunicación bus falla, el micro-controlador mismo también falle en hacer su trabajo, tales como el de configurar los puertos de entrada-salida para propósitos generales (GPIO) . En dicho caso, los periféricos que necesitan manejarse por medio de estos puertos (GPIO) , no tienen ni comunicación bus ni acción (GPIO) . Esto significa que el sistema se encuentra en un estado de fallo.

La existencia de fallo en la detección y en el restablecimiento del sistema es conocido a partir del documento US 4434403, donde la señal de sincronismo debe comprobarse periódicamente; mientras que, dentro de sistema anteriormente descrito (al igual que en I2C) la señal de sincronismo puede no ser continua. La tecnología descrita tampoco es compatible con buses de datos unidireccionales.

Otro sistema común para superar las condiciones de fallo que ocurren en los sistemas de transmisión de datos es el sistema perro guardián (también denominado “temporizador perro guardián”) . El sistema proporciona una protección de software y restablece el software en condiciones de fallo; los fallos debidos a colapsos de hardware no pueden ser corregidos por el sistema de perro guardián.

El documento US 4811200, describe el sistema de perro guardián en donde el software y/o el hardware se proporciona para supervisar el funcionamiento del sistema e implementar el restablecimiento del microprocesador en el caso de un funcionamiento no apropiado del sistema. En este documento, los controladores dentro de aquel sistema requieren terminales de respuesta de actividad de bus de datos que no son compatibles con varios tipos de buses, mostrados en la figura 2.

En el documento de patente US 20060242517, se describe una lógica de supervisión que supervisa la actividad de bus de datos entre el procesador de datos y la memoria del aparato procesador de datos. La lógica de supervisión detecta un dato de acceso particular viajando a través del mencionado bus de datos dentro de un tiempo predeterminado. Dicho tiempo predeterminado se computa a través de un contador de la lógica de supervisión y si no se produce una detección de datos de acceso dentro del tiempo predeterminado, el procesador de datos realiza una operación predeterminada. La lógica y procedimiento revelados en el documento US 2006 0242517, de manera diferente a la presente invención, utiliza un contador para computar un tiempo predeterminado y es utilizada solo para supervisar la actividad bus entre procesador de datos y la memoria. Sin embargo, la presente invención puede utilizarse para cualquier tipo de bus que tenga transmisiones de señal periódicas.

El documento US 5864656 revela un sistema que supervisa un bus de datos y mide un tiempo de retardo entre dos transferencias de datos consecutivas. Si dicho retardo de tiempo se encuentra por encima de un límite predeterminado se ejecuta un software y un hardware de recuperación.

Como conclusión, los sistemas de la técnica anterior requieren bloques/registros especializados dentro del micro-controlador para generar una interrupción. Los sistemas existentes para la detección de fallos y la corrección para buses de datos no son compatibles con todo tipo de sistemas de bus. El micro-ordenador principal es responsable de otros periféricos, pero los fallos completos de sistema ocurren cuando el microcontrolador y el periférico fallan al comunicarse.

Resumen de la invención [0014] De acuerdo con la presente invención, el circuito de detección de fallo de actividad de bus universal y restablecimiento comprende:

- medios para establecer una constante de tiempo para detección de fallo a partir de datos de entrada referidos a un periodo de datos del bus y,

- medios de detección para detectar para detectar un estado de actividad o de inactividad en dicho bus, generando dichos medios de detección una salida de reposición a partir de dicha constante de tiempo y dicha condición de inactividad.

De forma preferida el circuito comprende adicionalmente medios para determinar dicho periodo de tiempo del bus, enviando dichos datos de entrada a los mencionado medios de establecimiento de la constante de tiempo.

De manera preferida, los medios para determinación de una constante de tiempo seleccionan un valor de constante de tiempo de entre una pluralidad de diferentes valores de constante de tiempo dados.

De forma preferida, los medios de detección mencionados comprenden un circuito de entrada que determina un valor medio de corriente continua de una señal de datos en dicho bus; un circuito de detección de actividad que recibe en la entrada dicho valor medio a través de dicha constante de tiempo, a fin de generar dicha salida de reposición cuando dicho valor medio es indicativo de inactividad en dicho bus.

De manera preferida, dicho valor medio indicativo de inactividad en dicho bus determina la condición de conductividad de medios de diodo que cambian el nivel de salida de dicho circuito de detección de actividad a través de dicha constante de tiempo para así generar dicha salida de reposición como un estado de conmutación de dicho circuito de detección de actividad.

Preferiblemente, el procedimiento comprende además una etapa de determinación de dichos datos de entrada relativos periodo de datos del bus.

La presente invención proporciona un sistema de detección y corrección que ofrece ventajas sobre el estado de la técnica. Ofrece detección de fallo de bus universal y corrección de sistema para colapso de sistema que es aplicable a todo tipo de buses que tengan transmisión de datos periódica. También, para generar una interrupción en el micro-controlador no se requieren registros/bloques especializados de tipo alguno. Además, la invención no solo ofrece soluciones al colapso de software sin que también resuelve colapsos de hardware.

Objecto de la invención [0021] El objeto de la invención es proporcionar un procedimiento y circuito universales para actividad de bus y un sistema de recuperación mediante supervisión de forma externa de la señal de bus, detectando tipo de bus, estableciendo constantes de tiempo por tipos de buses y generación de una señal de salida para los terminales de interrupción/reposición del mircro-controlador y/o del ICs periférico en una condición de fallo.

Un objeto adicional de la invención es un procedimiento de restablecimiento y detección de fallo de actividad de bus universal, que comprende la etapas de: determinar una constante de tiempo para detección de fallo a partir de datos de entrada relativos a un periodo de datos de bus; detectar una condición actividad o inactividad en dicho bus, generando los mencionados medios de detección una salida de reposición a partir de dicha constante de tiempo y dicha condición... [Seguir leyendo]

Reivindicaciones:

1. Circuito para detección y restablecimiento de actividad de bus para circuitos inter-integrados que comprende:

- medios ajustados manualmente (C2, B1, B2, Bn) para establecer una constante de tiempo que selecciona un valor constante de tiempo de entre una pluralidad de diferentes valores de constante de tiempo dados (B1, B2, Bn) ;

- medios de detección (Q1, Q2, Q3, Q4) para detectar un estado de actividad o de inactividad en dicho bus, comprendiendo un circuito de entrada (Q1, Q2 y Q3) que determina un valor medio de corriente continua de una señal de datos en dicho bus de conexión de circuitos inter-integrados y un circuito de detección de actividad (Q4) que genera una salida de reposición cuando dicho valor medio de corriente continua, indica inactividad en dicho bus para un tiempo definido por dicha constante de tiempo establecida, donde dicho circuito de entrada comprende:

- un circuito seguidor de emisor (Q1) que es utilizado como memoria intermedia de entrada;

- un bloque de medición de media que toma la media de corriente continua de la señal de datos;

- una memoria intermedia de salida (Q3) que pone en memoria intermedia e invierte la señal cuya media de corriente continua ha sido tomada, donde valores altos en un colector de transistor de dicha memoria intermedia de salida (Q3) activan un diodo (D1) y cargan un condensador (C2) ; donde la carga y descarga de dicho condensador (C2) son dos funciones temporales con dicha constante de tiempo ajustada como parámetro;

- y donde dicho circuito de detección de actividad comprende un cuarto bloque que genera dicha salida de reposición como señal alta o baja de acuerdo con una tensión de dicho condensador (C2) ; y

- un puerto de salida de reposición para entregar como salida dicha señal de salida de reposición.

2. Procedimiento para detección y restablecimiento de actividad bus para un bus de conexión de circuitos interintegrados caracterizado por que comprende las siguientes etapas:

- ajustar manualmente una contante de tiempo mediante la selección de un valor de constante de tiempo de entre una pluralidad valores de constante de tiempo dados;

- determinar una valor medio de corriente continua de una señal de datos en dicho bus de conexión de circuitos inter-integrados;

- detectar un estado de actividad o de inactividad para un periodo definido por dicha constante de tiempo ajustada en dicho bus de conexión de circuitos inter-integrados en relación a dicho valor medio de corriente continua determinado; generar un salida de reposición a partir de dicha constante de tiempo cuando el valor medio de corriente continua es indicativo de inactividad en dicho bus.

REFERENCIAS CITADAS EN LA DESCRIPCIÓN

La lista de referencias citada por el solicitante lo es solamente para utilidad del lector, no formando parte de los documentos de patente europeos. Aún cuando las referencias han sido cuidadosamente recopiladas, no pueden excluirse errores u omisiones y la OEP rechaza toda responsabilidad a este respecto.

Documentos de patente citados en la descripción

• US 4434403 A [0008] • US 20060242517 A [0011]

• US 4811200 A [0010] • US 5864656 A [0012]

Patentes similares o relacionadas:

Procedimiento de gestión de módulos de software integrados para una computadora electrónica de un dispositivo de conmutación eléctrica, del 17 de Junio de 2020, de SCHNEIDER ELECTRIC INDUSTRIES SAS: Procedimiento de gestión de módulos de software integrados para una computadora electrónica integrada de un dispositivo eléctrico de conmutación de […]

Transmisión de datos entre unidades computacionales mediante tecnología de señales seguras, del 27 de Mayo de 2020, de Siemens Mobility GmbH: Módulo de entrada y salida para enviar y recibir datos a través de una línea de datos , caracterizado por las siguientes características:

- una máquina […]

Transmisión de datos entre unidades computacionales mediante tecnología de señales seguras, del 27 de Mayo de 2020, de Siemens Mobility GmbH: Módulo de entrada y salida para enviar y recibir datos a través de una línea de datos , caracterizado por las siguientes características:

- una máquina […]

Procedimiento de parada de emergencia y sistema de seguridad asociado, del 20 de Mayo de 2020, de CLEARSY: Procedimiento de parada de emergencia de un elemento de seguridad de un conjunto de seguridad , comprendiendo el conjunto de seguridad […]

Método y dispositivo para procesar información de llamadas de servicio, del 20 de Mayo de 2020, de Advanced New Technologies Co., Ltd: Un método para procesar una cadena de llamadas de servicio, el método que comprende: adquirir una o más cadenas de llamadas de servicio […]

Actualización de software de componentes no críticos en sistemas distribuidos críticos para la seguridad dual, del 13 de Mayo de 2020, de Siemens Mobility GmbH: Procedimiento para el funcionamiento de un sistema crítico para la seguridad con al menos un primer dispositivo de datos con un software aprobado y relevante […]

Dispositivo de vigilancia externo con soporte de regeneración inversa integrado, del 1 de Abril de 2020, de THYSSENKRUPP PRESTA AG: Un aparato de servodirección eléctrica para asistir a la dirección de un vehículo de motor al conferir par generado por un motor eléctrico a un mecanismo […]

Sistemas y métodos para sincronización de datos y gestión de conmutación por error, del 19 de Febrero de 2020, de IEX Group, Inc: Un método para ejecutar una aplicación de forma expeditiva en al menos un procesador informático, comprendiendo el método: ejecutar simultáneamente una pluralidad de instancias […]

Dispensador de fragancias y procedimiento de operación de dicho dispensador de fragancias, del 8 de Enero de 2020, de ZOBELE HOLDING SPA: Dispensador de fragancias que comprende un dispositivo temporizador, comprendiendo dicho dispositivo temporizador un primer temporizador en comunicación […]