Perforación de códigos LDPC en función del esquema de modulación.

Un método para perforar bits de paridad de una palabra de código de comprobación de paridad de baja densidad(LDPC) asociada con una codificación de canal en un sistema de comunicación que utiliza un código LDPC en untransmisor que incluye un aplicador 1580 de patrón de perforación,

involucrando el código LDPC una matriz decomprobación de paridad, comprendiendo la matriz de comprobación de paridad una parte de informacióncorrespondiente a bits de información de una palabra de código LDPC y una parte de paridad correspondiente a bitsde paridad de la palabra de código LDPC, comprendiendo la parte de información grupos de columnas que tienenigual longitud, caracterizado porque el método comprende:

determinar un número Np de bits de paridad para perforación y un esquema de modulación;

formar conjuntos de bits de paridad mediante dividir los bits de paridad en intervalos predeterminados, y estandoformados los conjuntos de bits de paridad mediante la siguiente ecuación:**Fórmula**

Tipo: Patente Europea. Resumen de patente/invención. Número de Solicitud: E09153765.

Solicitante: SAMSUNG ELECTRONICS CO., LTD..

Nacionalidad solicitante: República de Corea.

Dirección: 129, Samsung-ro, Yeongtong-gu Suwon-si, Gyeonggi-do, 443-742 REPUBLICA DE COREA.

Inventor/es: KIM, JAE-YOEL, YANG, KYEONG, CHEOL, KWON,HWAN-JOON, Lee,Hak-Ju, Myung,Seho, Kim,Kyung-Joong, AHN,SEOK-KI.

Fecha de Publicación: .

Clasificación Internacional de Patentes:

- H03M13/11 ELECTRICIDAD. › H03 CIRCUITOS ELECTRONICOS BASICOS. › H03M CODIFICACION, DECODIFICACION O CONVERSION DE CODIGO, EN GENERAL (por medio de fluidos F15C 4/00; convertidores ópticos analógico/digitales G02F 7/00; codificación, decodificación o conversión de código especialmente adaptada a aplicaciones particulares, ver las subclases apropiadas, p. ej. G01D, G01R, G06F, G06T, G09G, G10L, G11B, G11C, H04B, H04L, H04M, H04N; cifrado o descifrado para la criptografía o para otros fines que implican la necesidad de secreto G09C). › H03M 13/00 Codificación, decodificación o conversión de código para detectar o corregir errores; Hipótesis básicas sobre la teoría de codificación; Límites de codificación; Métodos de evaluación de la probabilidad de error; Modelos de canal; Simulación o prueba de códigos (detección o correción de errores para la conversión de código o la conversión analógico/digital, digital/analógica H03M 1/00 - H03M 11/00; especialmente adaptados para los computadores digitales G06F 11/08; para el registro de la información basado en el movimiento relativo entre el soporte de registro y el transductor G11B, p. ej. G11B 20/18; para memorias estáticas G11C). › usando bits de paridad múltiple.

- H03M13/25 H03M 13/00 […] › Detección de errores o corrección de errores transmitidos por codificación espacial de la señal, es decir, añadiendo redundancia en la constelación de la señal, p. ej. modulación codificada de Trellis [TCM].

- H04L1/00 H […] › H04 TECNICA DE LAS COMUNICACIONES ELECTRICAS. › H04L TRANSMISION DE INFORMACION DIGITAL, p. ej. COMUNICACION TELEGRAFICA (disposiciones comunes a las comunicaciones telegráficas y telefónicas H04M). › Disposiciones para detectar o evitar errores en la información recibida.

- H04L27/34 H04L […] › H04L 27/00 Sistemas de portadora modulada. › Sistemas de portadora de modulación de fase y de amplitud, p. ej. en cuadratura de amplitud.

- H04L27/36 H04L 27/00 […] › Circuitos de modulación; Circuitos en el emisor.

PDF original: ES-2439262_T3.pdf

Fragmento de la descripción:

Perforación de códigos LDPC en función del esquema de modulación

ANTECEDENTES DE LA INVENCIÓN

Campo de la Invención La presente invención se refiere a un sistema de comunicación que utiliza códigos de comprobación de paridad de baja densidad (LDPC, Low-Density Parity-Check) . Más en particular, la presente invención se refiere a un método de codificación/descodificación de canal y a un aparato para generar códigos LDPC con varias longitudes de palabra de código y tasas de código a partir de un código LDPC proporcionado en modulación de orden superior.

Descripción de la técnica relacionada En los sistemas de comunicación inalámbricos, el rendimiento del enlace disminuye significativamente debido a diversos ruidos en los canales, al fenómeno de desvanecimiento y a la interferencia entre símbolos (ISI, Inter-Symbol Interference) . Por lo tanto, para conseguir sistemas de comunicación digital de alta velocidad que requieren un caudal de datos y una fiabilidad elevados, tales como la comunicación móvil de siguiente generación, la difusión digital e internet portátil, es necesario desarrollar una tecnología para superar los ruidos de canal, el desvanecimiento y la ISI. Recientemente, se ha llevado a cabo un estudio intensivo sobre los códigos de corrección de errores como método para aumentar la fiabilidad de la comunicación mediante recuperar eficientemente información distorsionada.

El código LDPC, introducido en primer lugar por Gallager en la década de 1960, ha perdido importancia con el tiempo debido a la complejidad de su implementación, que no podía ser solucionada mediante la tecnología de entonces. Sin embargo, dado que el turbo código, que fue descubierto por Berrou, Glavieux, y Thitimajshima en 1993, presenta niveles de rendimiento que se aproximan al límite de Shannon del canal, se han llevado a cabo investigaciones sobre descodificación iterativa y codificación de canal basadas en un grafo, junto con análisis sobre el rendimiento y las características del turbo código. Con esto como impulso, el código LDPC ha vuelto a ser estudiado a finales de la década de 1990, demostrándose que el código LDPC tiene un rendimiento próximo al límite de Shannon del canal, si el código LDPC es sometido a descodificación mediante aplicación de descodificación iterativa en base a un algoritmo suma-producto sobre un grafo de Tanner (un caso especial de un grafo factor) correspondiente al código LDPC.

El código LDPC se representa habitualmente utilizando una técnica de representación de grafos, y muchas características pueden ser analizadas mediante los métodos basados en teoría de grafos, álgebra y teoría de probabilidades. En general, un modelo de grafos de los códigos de canal es útil para la descripción de los códigos, y mediante mapear la información sobre los bits codificados a los vértices en el grafo y mapear las relaciones entre los bits a las aristas en el grafo, es posible considerar el grafo como una red de comunicación en la que los vértices intercambian mensajes predeterminados a través de las aristas, posibilitando de este modo obtener un algoritmo de descodificación natural. Por ejemplo, un algoritmo de descodificación obtenido a partir de un grafo reticulado ("trellis") , que puede ser considerado una clase de grafo, puede incluir el muy conocido algoritmo de Viterbi y un algoritmo de Bahl, Cocke, Jelinek y Raviv (BCJR) .

El código LDPC se define en general como una matriz de comprobación de paridad, y puede ser expresado utilizando un grafo bipartito, que se denomina un grafo de Tanner. El grafo bipartito es un grafo en el que los vértices que constituyen el grafo están divididos en dos tipos diferentes, y el código LDPC está representado por el grafo bipartito que consiste en vértices, de los que unos se denominan nodos variables y los otros nodos de comprobación. Los nodos variables están mapeados uno a uno a los bits codificados.

Se describirá un método de representación de grafos para el código LDPC haciendo referencia a las figuras 1 y 2.

La figura 1 muestra un ejemplo de una matriz de comprobación de paridad H1 de un código LDPC con 4 filas y 8 columnas. Haciendo referencia a la figura 1, debido a que el número de columnas es 8, la matriz de comprobación de paridad H1 significa un código LDPC que genera una palabra de código de longitud 8, y las columnas están mapeadas a 8 bits codificados en una relación de uno a uno.

La figura 2 muestra un grafo de Tanner correspondiente a la matriz de comprobación de paridad H1 de la figura 1.

Haciendo referencia la figura 2, el grafo de Tanner del código LDPC incluye 8 nodos variables x1 (202) , x2 (204) , x3 (206) , x4 (208) , x5 (210) , x6 (212) , x7 (214) y x8 (216) , y 4 nodos de comprobación 218, 220, 222 y 224. Una columna i-ésima y una fila j-estima en la matriz de comprobación de paridad H1 del código LDPC son mapeadas a un nodo variable xi y a un nodo de comprobación j-ésimo, respectivamente. Además, un valor de 1, es decir, un valor distinto 2 5

de cero, en la posición en que se cruzan una columna i-ésima y una fila j-ésima en la matriz de comprobación de paridad H1 del código LDPC, indica que existe una arista entre el nodo variable xi y el nodo de comprobación j-ésimo en el grafo de Tanner que se muestra en la figura 2.

En el grafo de Tanner del código LDPC, el grado del nodo variable y del nodo de comprobación indica el número de aristas contenidas en cada nodo respectivo, y el grado es igual al número de entradas distintas de cero en una columna o fila correspondiente al nodo pertinente en la matriz de comprobación de paridad del código LDPC. Por ejemplo, en la figura 2, los grados de los nodos variables x1 (202) , x2 (204) , x3 (206) , x4 (208) , x5 (210) , x6 (212) , x7

(214) y x8 (216) son 4, 3, 3, 3, 2, 2, 2 y 2, respectivamente, y los grados de los nodos de comprobación 218, 220, 222 y 224 son 6, 5, 5 y 5, respectivamente. Además, los números de las entradas distintas de cero en las columnas de la matriz de comprobación de paridad H1 en la figura 1, que corresponden a los nodos variables en la figura 2, coinciden con sus grados 4, 3, 3, 3, 2, 2, 2 y 2, y los números de las entradas distintas de cero en las filas de la matriz de comprobación de paridad H1 en la figura 1, que corresponden a los nodos de comprobación de la figura 2, coinciden con sus grados 6, 5, 5 y 5.

Para expresar la distribución de grados para los nodos del código LDPC, la relación del número de nodos variables de grado i respecto al número total de nodos variables se define como fi, y la relación del número de nodos de comprobación de grado j respecto al número total de nodos de comprobación se define como gj. Por ejemplo, para el código LDPC correspondiente a las figuras 1 y 2, f2=4/8, f3=3/8, f4=1/8, y fi=0 para in , 3, 4; y g5=3/4, g6=1/4, y gj=0 para jn5, 6. Cuando la longitud del código LDPC, es decir, el número de columnas, se define como N, y el número de filas se define como N/2, la densidad de entradas distintas de cero en toda la matriz de comprobación de paridad que tiene la distribución de grados anterior se calcula tal como se muestra en la ecuación (1) .

En la ecuación (1) , cuando N aumenta, disminuye la densidad de 1's en la matriz de comprobación de paridad. En general, en relación con el código LDPC, dado que la longitud N de la palabra de código es inversamente proporcional a la densidad de entradas distintas de cero, un código LDPC con N grande tiene una densidad muy baja de entradas distintas de cero. El término 'baja densidad' para el código LDPC está originado en la relación mencionada anteriormente.

A continuación, haciendo referencia a la figura 3, se realizará una descripción de características de una matriz de comprobación de paridad de un código LDPC estructurado aplicable a la presente invención. La figura 3 muestra un código LDPC adoptado como la tecnología estándar de transmisión de difusión de señales digitales de videotransmisión por satélite de segunda generación (DVB-S2, Digital Video Broadcasting-Satellite transmission 2nd generation) , que es uno de los estándares europeos de difusión digital.

En la figura 3, N1 y K1 indican una longitud de palabra de código y una longitud de información (una longitud de una palabra de información) de un código LDPC, respectivamente, (N1-K1) proporciona una longitud de paridad. Además, los enteros M1 y q se determinan de manera que satisfacen q= (N1-K1) /M1. Preferentemente, K1/M1 deberá ser asimismo un número entero. La matriz de comprobación de paridad en la figura 3 se denominará en el presente documento una primera matriz de comprobación de paridad H1, sólo para mayor comodidad.

Haciendo... [Seguir leyendo]

Reivindicaciones:

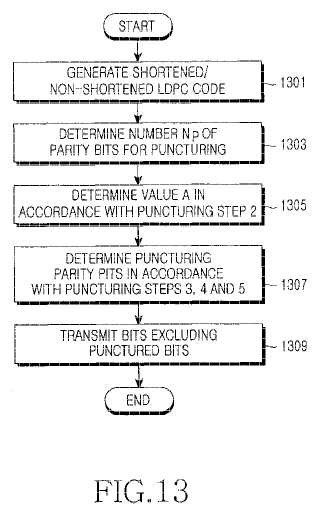

1. Un método para perforar bits de paridad de una palabra de código de comprobación de paridad de baja densidad (LDPC) asociada con una codificación de canal en un sistema de comunicación que utiliza un código LDPC en un transmisor que incluye un aplicador 1580 de patrón de perforación, involucrando el código LDPC una matriz de comprobación de paridad, comprendiendo la matriz de comprobación de paridad una parte de información correspondiente a bits de información de una palabra de código LDPC y una parte de paridad correspondiente a bits de paridad de la palabra de código LDPC, comprendiendo la parte de información grupos de columnas que tienen igual longitud, caracterizado porque el método comprende:

determinar un número Np de bits de paridad para perforación y un esquema de modulación;

formar conjuntos de bits de paridad mediante dividir los bits de paridad en intervalos predeterminados, y estando formados los conjuntos de bits de paridad mediante la siguiente ecuación:

donde Pj indica el j-ésimo conjunto de bits de paridad, N1 indica la longitud de la palabra de código LDPC, K1 indica la longitud de una palabra de información, M1 indica la longitud de un grupo de columnas, q es un valor que satisface q = (N1 - K1) / M1 e indica el intervalo predeterminado, donde K1/M1 es un entero, y 0 : j < q;

determinar el número A de conjuntos de bits de paridad para perforación, a partir del número de bits de paridad para perforación y de la longitud de un grupo de columnas, determinándose el número de conjuntos de bits de paridad mediante la siguiente ecuación:

y

perforar bits de paridad en base al número determinado A de conjuntos de bits de paridad a perforar, y de acuerdo con un orden predeterminado de conjuntos de bits de paridad a perforar,

en el que el orden predeterminado de conjuntos de bits de paridad se determina de acuerdo con el esquema de modulación.

2. El método según la reivindicación 1, que comprende además:

transmitir bits restantes, excepto los bits perforados.

3. Un aparato para perforar bits de paridad de una comprobación de paridad de baja densidad (LDPC) asociada con una codificación de canal en un sistema de comunicación que utiliza un código LDPC en un transmisor que incluye un aplicador 1580 de patrón de perforación, involucrando el código LDPC una matriz de comprobación de paridad, comprendiendo la matriz de comprobación de paridad una parte de información correspondiente a bits de información de una palabra de código LDPC y una parte de paridad correspondiente a bits de paridad de la palabra de código LDPC, comprendiendo la parte de información grupos de columnas que tienen igual longitud, caracterizado porque el aparato comprende:

un aplicador 1580 de patrón de perforación, para:

determinar un número Np de bits de paridad para perforación y un esquema de modulación;

formar conjuntos de bits de paridad mediante dividir los bits de paridad en intervalos predeterminados, y estando formados los conjuntos de bits de paridad mediante la siguiente ecuación:

donde Pj indica el j-ésimo conjunto de bits de paridad, N1 indica la longitud de una palabra de código LDPC, K1 indica la longitud de una palabra de información, M1 indica la longitud de un grupo de columnas, q es un valor que satisface q = (N1 - K1) / M1 e indica el intervalo predeterminado, donde K1/M1 es un entero, y 0 : j < q;

determinar el número A de conjuntos de bits de paridad para perforación, a partir del número de bits de paridad para perforación y de la longitud de un grupo de columnas, determinándose el número de conjuntos de bits de paridad mediante la siguiente ecuación:

y

perforar bits de paridad en base al número determinado de conjuntos de bits de paridad a perforar, y de acuerdo con un orden predeterminado de conjuntos de bits de paridad a perforar,

en el que el orden predeterminado de conjuntos de bits de paridad se determina de acuerdo con el esquema de modulación.

4. El aparato según la reivindicación 3, que comprende además:

un transmisor para transmitir bits de paridad restantes, excepto los bits de paridad perforados.

5. El método según la reivindicación 1, el aparato según la reivindicación 3, respectivamente, en los que el orden de los conjuntos de bits de paridad a perforar se determinan como 6, 4, 13, 9, 18, 8, 15, 20, 5, 17, 2, 22, 24, 7, 12, 1, 16, 23, 14, 0, 21, 10, 19, 11, 3, cuando la longitud de una palabra de código es de 16200 y la longitud de información es de 7200, y el esquema de modulación es 16QAM.

6. El método según la reivindicación 1, el aparato según la reivindicación 3, respectivamente, en los que el orden de los conjuntos de bits de paridad a perforar se determinan como 6, 15, 13, 10, 3, 17, 21, 8, 5, 19, 2, 23, 16, 24, 7, 18, 1, 12, 20, 0, 4, 14, 9, 11, 22, cuando la longitud de una palabra de código es de 16200 y la longitud de información es de 7200, y el esquema de modulación es 64QAM.

7. El método según la reivindicación 1, el aparato según la reivindicación 3, en el que

el orden de los conjuntos de bits de paridad a perforar se determina en base a conexiones entre bits perforados y bits no perforados y a fiabilidades de bits que constituyen un símbolo de modulación de acuerdo con el esquema de modulación.

8. El método según la reivindicación 1, que comprende además:

perforar adicionalmente bits de paridad restantes, excepto los bits de paridad perforados, cuando el número de bits de paridad a perforar no es un múltiplo de la longitud de un grupo de columnas.

9. El aparato según la reivindicación 3, en el que el aplicador 1580 del patrón de perforación perfora adicionalmente bits de paridad restantes, excepto los bits de paridad perforados, cuando el número de bits de paridad a perforar no es un múltiplo de la longitud de un grupo de columnas.

10. El método según la reivindicación 1, el aparato según la reivindicación 3, respectivamente, en los que, cuando el esquema de modulación es 16QAM, un código LDPC con una longitud de palabra de código de 16200, una longitud de información de 7200 y una longitud de un grupo de columnas de 360, el orden de conjuntos de bits de paridad a perforar se determina a partir de la siguiente función de permutación n:

n (0) n (1) n (2) n (3) n (4) n (5) n (6) n (7) n (8)

6 4 13 9 18 8 15 20 5

n (9) n (10) n (11) n (12) n (13) n (14) n (15) n (16) n (17)

(continuación)

17 2 22 24 7 12 1 16 23

n (18) n (19) n (20) n (21) n (22) n (23) n (24)

14 0 21 10 19 11 3

de manera que la perforación se lleva a cabo con respecto a A grupos Pn (0) , Pn (1) , ...Pn (A-1) , que definen el patrón de perforación.

11. El método según la reivindicación 1, el aparato según la reivindicación 3, respectivamente, en los que, cuando el esquema de modulación es 64QAM, un código LDPC con una longitud de palabra de código de 16200, una longitud de información de 7200 y una longitud de un grupo de columnas de 360, el orden de conjuntos de bits de paridad a perforar se determina a partir de la siguiente función de permutación n:

n (0) n (1) n (2) n (3) n (4) n (5) n (6) n (7) n (8)

6 15 13 10 3 17 21 8 5

n (9) n (10) n (11) n (12) n (13) n (14) n (15) n (16) n (17)

19 2 23 16 24 7 18 1 12

n (18) n (19) n (20) n (21) n (22) n (23) n (24)

20 0 4 14 9 11 22

de manera que la perforación se lleva a cabo con respecto a A grupos Pn (0) , Pn (1) , ...Pn (A-1) , que definen el patrón de perforación.

12. El método según la reivindicación 1, el aparato según la reivindicación 3, respectivamente, en los que, el codificador LDPC con una longitud de palabra de código de 16200, una longitud de información de 7200 y una longitud de un grupo de columnas de 360, el orden de los conjuntos de bits de paridad a perforar se determina a partir de la función de permutación n, determinada a partir de las siguientes relaciones:

n (0) n (1) n (2) n (3) n (4) n (5) n (6) n (7) n (8)

n (9) n (10) n (11) n (12) n (13) n (14) n (15) n (16) n (17)

n (18) n (19) n (20) n (21) n (22) n (23) n (24) - -

Relación entre funciones de permutación suboptimizadas en BPSK/QPSK

6 4 18 9 13 8 15 20 5

17 2 24 10 22 12 3 16 23

1 14 0 21 19 7 11 - -

Relación entre funciones de permutación suboptimizadas en 16QAM

6 4 13 9 18 8 15 20 5

(continuación)

17 2 22 24 7 12 1 16 23

14 0 21 10 19 11 3 - -

Relación entre funciones de permutación suboptimizadas en 64QAM

6 15 13 10 3 17 21 8 5

19 2 23 16 24 7 18 1 12

20 0 4 14 9 11 22 - -

de manera que la perforación se lleva a cabo con respecto a A grupos Pn (0) , Pn (1) , ...Pn (A-1) , que definen el patrón de perforación.

Patentes similares o relacionadas:

Aparato de comunicación inalámbrica y procedimiento de generación de señales de referencia, del 29 de Julio de 2020, de Sun Patent Trust: Un aparato de comunicación para una estación base que comprende: un transmisor, el cual, en operación, transmite, a un terminal, información […]

Procedimiento y aparato para inserción de índice de bloque de código en un sistema celular de comunicación inalámbrica, del 29 de Julio de 2020, de SAMSUNG ELECTRONICS CO., LTD.: Un procedimiento de un terminal en un sistema de comunicación inalámbrica, comprendiendo el procedimiento: recibir, de una estación base, un bloque de información maestra, […]

Información de control en un sistema de comunicación inalámbrica, del 15 de Julio de 2020, de QUALCOMM INCORPORATED: Un procedimiento para enviar datos de tráfico e información de control en un sistema de comunicación inalámbrica, que comprende: realizar conformación de haces […]

Detección y comprobación de error de señalización de retroalimentación en sistemas de comunicación inalámbrica de MIMO, del 15 de Julio de 2020, de INTERDIGITAL TECHNOLOGY CORPORATION: Un método implementado en una unidad de transmisión recepción inalámbrica, WTRU, caracterizado por que el método comprende: proporcionar una pluralidad […]

Repetición de transmisiones de señales en sistemas de comunicación, del 15 de Julio de 2020, de SAMSUNG ELECTRONICS CO., LTD.: Un procedimiento para que un equipo de usuario, UE, transmita una señal de acuse de recibo en un sistema de comunicación, comprendiendo el procedimiento: transmitir la señal […]

Método y dispositivo de codificación, del 15 de Julio de 2020, de HUAWEI TECHNOLOGIES CO., LTD.: Un método de codificación, que comprende: realizar (S101), mediante un extremo de transmisión basado en un polinomio de verificación de redundancia cíclica, […]

Método, aparato y sistema para retroalimentar la decodificación de detención temprana, del 1 de Julio de 2020, de ZTE CORPORATION: Un método para retroalimentar un resultado de decodificación de la decodificación de detención temprana, caracterizado porque comprende: en un intervalo de tiempo […]

Tramas Wi-Fi que incluyen extensiones de trama, del 1 de Julio de 2020, de QUALCOMM INCORPORATED: Un procedimiento de comunicación inalámbrica realizado por un aparato, que comprende: generar una trama para activar la transmisión […]