Dispositivo de almacenamiento de imagen y método de acceso.

Dispositivo de almacenamiento adaptado para almacenar una imagen codificada jerárquicamente que presentapor lo menos una primera y una segunda capas de datos de imagen,

proporcionando dicha primera capa ladefinición más alta de la imagen y presentando la segunda capa un número menor de píxeles y proporcionando unadefinición menor que la primera capa de la imagen, en el que 2x2 píxeles en la primera capa de la imagen secorresponden con un píxel en la segunda capa de la imagen, formándose dicho un píxel en la segunda capa de laimagen mediante la suma de los 2x2 píxeles correspondientes en la primera capa de la imagen; comprendiendodicho dispositivo:

una primera área de memoria (2) que presenta una capacidad de memoria para almacenar 3/4 de los píxeles de laprimera capa de la imagen, de tal manera que un píxel en cada uno de dichos 2x2 píxeles en la imagen de primeracapa correspondiente a un píxel en la imagen de segunda capa no se almacena en la primera área de memoria; enel que las direcciones de los píxeles en la primera área de memoria se corresponden con sus posicionesrespectivas en la imagen, dividiéndose dicha primera área de memoria en unos primer y segundo bloques, en elque los primer y segundo bloques son direccionables basándose en cada bloque individual proporcionando unprimer terminal de direcciones en la primera área de memoria para el primer bloque y un segundo terminal dedirecciones en la primera área de memoria para el segundo bloque;

una segunda área de memoria (3) adaptada para almacenar la segunda capa de la imagen, en el que dichasegunda área de memoria está dividida en unos primer y segundo bloques correspondientes respectivamente a losprimer y segundo bloques de la primera área de memoria, en el que los primer y segundo bloques de la segundaárea de memoria son direccionables basándose en cada bloque individual proporcionando un primer terminal dedirecciones en la segunda área de memoria para el primer bloque y un segundo terminal de direcciones en lasegunda área de memoria para el segundo bloque;

en el que el primer y el segundo bloques de la primera área de memoria almacenan cada 2N líneas alternas de laprimera capa de la imagen respectivamente, en el que N es un número natural, y los primer y segundo bloques dela segunda área de memoria almacenan cada N líneas alternas correspondientes de la segunda capa de la imagenrespectivamente.

Tipo: Patente Europea. Resumen de patente/invención. Número de Solicitud: E98306046.

Solicitante: SONY CORPORATION.

Nacionalidad solicitante: Japón.

Dirección: 6-7-35 KITASHINAGAWA SHINAGAWA-KU, TOKYO 141 JAPON.

Inventor/es: KONDO, TETSUJIRO.

Fecha de Publicación: .

Clasificación Internacional de Patentes:

- G09G1/16 FISICA. › G09 ENSEÑANZA; CRIPTOGRAFIA; PRESENTACION; PUBLICIDAD; PRECINTOS. › G09G DISPOSICIONES O CIRCUITOS PARA EL CONTROL DE DISPOSITIVOS DE REPRESENTACION QUE UTILIZAN MEDIOS ESTATICOS PARA PRESENTAR UNA INFORMACION VARIABLE (dispositivos de transferencia de datos entre computadores y pantallas digitales G06F 3/14; dispositivos de representación estáticos realizados por la asociación disociable de varias fuentes individuales o de varias celdas individuales que controlan la luz G09F 9/00; dispositivos de representación estáticos realizados por la asociación constructiva indisociable de varias fuentes de luz H01J, H01K, H01L, H05B 33/12; digitalización, transmisión o reproducción de documentos o similares p. ej. transmisión por fax o detalles del mismo H04N 1/00). › G09G 1/00 Disposiciones o circuitos de control que presenten interés únicamente para la representación utilizando tubos de rayos catódicos. › con trama en coordenadas rectangulares extendiéndose sobre toda la superficie de la pantalla, es decir, con trama de barrido del tipo televisión.

- G09G5/36 G09G […] › G09G 5/00 Disposiciones o circuitos de control de representación comunes a la representación utilizando tubos de rayos catódicos y a la representación utilizando otros medios de visualización. › caracterizados por la presentación de dibujos gráficos individuales utilizando una memoria con mapas de bits (G09G 5/42 tiene prioridad).

PDF original: ES-2399953_T3.pdf

Fragmento de la descripción:

Dispositivo de almacenamiento de imagen y método de acceso.

La presente invención se refiere a dispositivos de almacenamiento y a métodos de acceso a los mismos. Más particularmente, aunque no de forma limitativa, la invención se refiere a un dispositivo de almacenamiento y a un método de acceso que se usan preferentemente en la codificación jerárquica que divide una imagen en una pluralidad de capas que tienen números diferentes de píxeles.

En un método de codificación disponible, se usa una imagen de alta definición (datos de capa jerárquica inferior o de primera capa) para formar datos de imagen de una segunda capa que tiene un número menor de píxeles, a continuación los datos de imagen de la segunda capa se usan para formar datos de imagen de una tercera capa que tiene un número todavía menor de píxeles, y este proceso se repite hasta que se forman datos de imagen de la capa superior. A un método de codificación de este tipo se le denomina codificación jerárquica, en la cual, en un monitor se presentan datos de imagen de cada capa de acuerdo con la definición respectiva (el número de píxeles) . Así un usuario ve los datos de imagen mediante la selección de los datos de imagen que se corresponden con la definición del propio monitor del usuario, de entre los datos de imagen codificados jerárquicamente.

Los datos de imagen de una definición se tratan como datos de imagen de la (primera) capa jerárquica inferior para formar datos de imagen de capas superiores secuencialmente. Cuando todos estos datos se almacenan y transmiten tal como son, se requieren adicionalmente una capacidad de memoria añadida y una capacidad de transmisión de datos añadida para los datos de imagen de las capas superiores en comparación con el caso en el que solamente se almacenan o transmiten datos de imagen de la capa inferior.

En el contexto de la presente invención el objeto es un método de codificación jerárquica para restringir un incremento de la capacidad de memoria.

Por ejemplo, supóngase en este momento que la suma de cuatro píxeles de 2 x 2 (filas x columnas) se trata como un píxel jerárquico superior (un valor de píxel) en una codificación jerárquica de tres capas. Haciendo referencia a la figura 9A, 8 x 8 píxeles se consideran en este momento como una imagen de la capa jerárquica inferior, y se calcula la suma m0 de los cuatro píxeles izquierdos superiores, 2 x 2 píxeles, h00, h10, h01, y h11, y a continuación la suma m0 se trata como el píxel izquierdo superior en una segunda capa. De la misma manera, se calculan respectivamente la suma m1 de los cuatro píxeles derechos superiores h20, h30, h21, y h31, la suma m2 de los cuatro píxeles izquierdos inferiores h02, h12, h03, y h13, y la suma m3 de los cuatro píxeles derechos inferiores h22, h32, h23, y h33 en la capa jerárquica inferior, y estas sumas se tratan respectivamente como los píxeles derechos superiores, izquierdos inferiores y derechos inferiores en la segunda capa. Se calcula la suma q0 de los cuatro píxeles m0, m1, m2, y m3 como 2 x 2 píxeles en la segunda capa, y la suma es un píxel de una imagen en la capa jerárquica superior.

Si se almacenan todos los píxeles h00 a h33, m0 a m3, y q0, se requerirá adicionalmente la capacidad de memoria añadida para los píxeles m0 a m3 en la segunda capa y el píxel q0 en la tercera capa.

Haciendo referencia a la FIG. 9B, el píxel q0 de la tercera capa se posiciona, por ejemplo, en lugar del píxel derecho inferior m3, de entre los píxeles de la segunda capa m0 a m3. Así, la segunda capa se construye con los píxeles m0 a m2 y q0.

Haciendo referencia a la FIG. 9C, el píxel m0 de la segunda capa se posiciona, por ejemplo, en lugar del píxel izquierdo inferior h11, de entre los píxeles de la primera capa h00, h10, h01, y h11, usándose todos ellos para determinar el píxel m0 en la segunda capa. De modo similar, los restantes píxeles m1, m2, y q0 en la segunda capa sustituyen a los píxeles h31, h13, y h33 en la primera capa. Aunque el píxel q0 no se obtiene directamente a partir de los píxeles h22, h32, h23, y h33, el píxel q0 sustituye al píxel m3 que se obtiene directamente a partir de estos píxeles, y así, el píxel q0 se posiciona en lugar del píxel m3 en la posición del píxel h33.

De esta manera, en referencia a la FIG. 9C, el número total de píxeles es 16 de 4 x 4 píxeles, y permanece sin cambios con respecto al número de píxeles en la capa jerárquica inferior mostrada en la FIG. 9A. Se evita así un incremento de la capacidad de memoria.

Los píxeles m3 y h33, sustituidos con el píxel q0, y los píxeles h11, h31 y h13, sustituidos respectivamente con los píxeles m0 a m2, se decodifican de la manera siguiente.

Puesto que q0 es la suma de m0 a m3, se cumple la ecuación q0 = m0 + m1 + m2 + m3. El píxel m3 se determina a partir de la ecuación m3 = q0 - (m0 + m1 + m2) .

m0 es la suma de h00, h10, h01 y h11, se cumple la ecuación m0 = h00 + h10 + h01 + h11. Así, h11 se determina a partir de la ecuación h11 = m0 - (h00 + h10 + h01) . De modo similar, se determinan h31, h13, y h33 se determina después de la determinación de m3.

En la anterior codificación jerárquica, se requería convencionalmente un circuito de retardo para un retardo de línea del píxel de la primera capa (valor de píxel) además de una memoria de propósito general para almacenar los resultados de la codificación jerárquica (tal como una SRAM (Memoria Estática de Acceso Aleatorio) o una DRAM (RAM Dinámica) ) .

Por ejemplo, en referencia a la FIG. 9C, es necesario calcular la ecuación h11 = m0 – (h00 + h10 + h01) para determinar, en la primera capa, el píxel h11, si h11 no se almacena. Los píxeles h00 y h10 en una primera línea y los píxeles h01 y m0 en una segunda línea son necesarios para calcular h11. Supóngase que los datos de imagen se leen de una memoria línea a línea desde la parte superior a la parte inferior, y el cálculo del píxel h11 debe esperar a la línea que comienza con h01, a saber, esperar a los píxeles m0, h00, h10, y h01 requeridos para calcular el píxel h11, con la línea que comienza con h00 retardada una línea.

Además de la memoria para almacenar los resultados de la codificación jerárquica, se requiere un circuito de retardo para el retardo de línea de los datos de imagen, provocando que el dispositivo resulte voluminoso.

El documento GB 2277012 da a conocer un sistema de almacenamiento para datos de imágenes, que comprende una pluralidad de memorias enlosadas (tiled memories) . Al sistema se le alimenta un conjunto individual de direcciones de lectura desde un generador de direcciones de lectura. El aparato puede soportar operaciones simultáneas de lectura y escritura en la memoria enlosada proporcionando dos conjuntos correspondientes de bloques de memoria, en los cuales un conjunto se puede usar para leer mientras que el otro se usa para escribir.

El documento JP 1997 9102951 da a conocer un método para mejorar la eficacia espacial de un circuito de procesado de señales que tiene codificación y decodificación jerárquicas. El método evita tener que incrementar la capacidad de memoria para almacenar los datos jerárquicos, y evita también tener un circuito de retardo de elementos de imagen o un circuito de retardo de línea.

La invención se define en las reivindicaciones adjuntas.

Una forma preferida de implementación de la invención que se describe a continuación en la presente memoria pretende proporcionar un dispositivo de almacenamiento que es compacto.

La invención se describirá a continuación de forma adicional, por medio de un ejemplo ilustrativo y no limitativo, en referencia a los dibujos adjuntos, en los cuales:

la FIG. 1 es un diagrama de bloques que muestra la construcción de un dispositivo de almacenamiento;

la FIG. 2 muestra la organización de una pantalla de visualización para una imagen de la primera capa;

la FIG. 3 es un primer diagrama de bloques funcionales del dispositivo de almacenamiento de la FIG. 1;

la FIG. 4 es un segundo diagrama de bloques funcionales del dispositivo de almacenamiento de la FIG. 1;

la FIG. 5 es un tercer diagrama de bloques funcionales del dispositivo de almacenamiento de la FIG. 1;

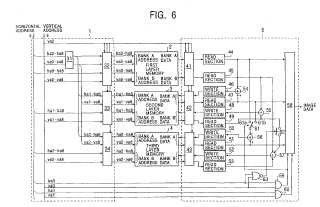

la FIG. 6 es un cuarto diagrama de bloques funcionales del dispositivo de almacenamiento de la FIG. 1 correspondiente a una forma de realización de la presente invención;

la FIG. 7 ilustra una memoria de primera capa 2 de la FIG. 6, que está dividida en un banco A y en un banco B;

la FIG. 8 es un quinto diagrama de bloques funcionales del dispositivo de almacenamiento de la FIG. 1; y

las FIGS. 9A a 9C ilustran un proceso de... [Seguir leyendo]

Reivindicaciones:

1. Dispositivo de almacenamiento adaptado para almacenar una imagen codificada jerárquicamente que presenta por lo menos una primera y una segunda capas de datos de imagen, proporcionando dicha primera capa la definición más alta de la imagen y presentando la segunda capa un número menor de píxeles y proporcionando una definición menor que la primera capa de la imagen, en el que 2x2 píxeles en la primera capa de la imagen se corresponden con un píxel en la segunda capa de la imagen, formándose dicho un píxel en la segunda capa de la imagen mediante la suma de los 2x2 píxeles correspondientes en la primera capa de la imagen; comprendiendo dicho dispositivo:

una primera área de memoria (2) que presenta una capacidad de memoria para almacenar 3/4 de los píxeles de la primera capa de la imagen, de tal manera que un píxel en cada uno de dichos 2x2 píxeles en la imagen de primera capa correspondiente a un píxel en la imagen de segunda capa no se almacena en la primera área de memoria; en el que las direcciones de los píxeles en la primera área de memoria se corresponden con sus posiciones respectivas en la imagen, dividiéndose dicha primera área de memoria en unos primer y segundo bloques, en el que los primer y segundo bloques son direccionables basándose en cada bloque individual proporcionando un primer terminal de direcciones en la primera área de memoria para el primer bloque y un segundo terminal de direcciones en la primera área de memoria para el segundo bloque;

una segunda área de memoria (3) adaptada para almacenar la segunda capa de la imagen, en el que dicha segunda área de memoria está dividida en unos primer y segundo bloques correspondientes respectivamente a los primer y segundo bloques de la primera área de memoria, en el que los primer y segundo bloques de la segunda área de memoria son direccionables basándose en cada bloque individual proporcionando un primer terminal de direcciones en la segunda área de memoria para el primer bloque y un segundo terminal de direcciones en la segunda área de memoria para el segundo bloque;

en el que el primer y el segundo bloques de la primera área de memoria almacenan cada 2N líneas alternas de la primera capa de la imagen respectivamente, en el que N es un número natural, y los primer y segundo bloques de la segunda área de memoria almacenan cada N líneas alternas correspondientes de la segunda capa de la imagen respectivamente;

un módulo de direccionamiento [1] adaptado para direccionar simultáneamente los bloques de dichas primera y segunda áreas de memoria de acuerdo con unas primera y segunda señales de dirección, en el que dicha primera señal de dirección y dicha segunda señal de dirección se corresponden con las posiciones horizontales y verticales de un píxel para dicha imagen de entrada, explorando así el módulo de direccionamiento secuencialmente a través de líneas de los datos de imagen y proporcionando simultáneamente:

(a) una primera y una segunda señal de dirección actual para un píxel en uno de los primer o segundo bloques en la primera área de memoria y simultáneamente una primera y una segunda señal de dirección actual para un píxel correspondiente en el bloque correspondiente de la segunda área de memoria, y (b) una primera y una segunda señal de dirección retardada para un píxel en el otro de los primer o segundo bloques en la primera área de memoria y simultáneamente una primera y una segunda señal de dirección retardada, para un píxel correspondiente en el bloque correspondiente de la segunda área de memoria;

en el que la primera y la segunda señales de dirección para la segunda área de memoria comprenden la parte de la primera y la segunda señales de dirección correspondientes para la primera área de memoria excluyendo el bit menos significativo, y en el que la primera y la segunda señales de dirección retardadas están retardadas en 2N líneas de la exploración secuencial; y

un módulo de lectura y escritura (5) para simultáneamente leer desde o escribir en direcciones, designadas por dichas primera y segunda señales de dirección, en los bloques de dichas primera y segunda áreas de memoria;

en el que dicho módulo de lectura y de escritura está configurado, cuando lee de acuerdo con la primera y la segunda señales de dirección actuales, cada uno sucesivamente de dichos tres de los 2x2 píxeles que están almacenados en la primera área de memoria, para restar el valor de cada píxel leído con respecto al valor del píxel correspondiente en la segunda memoria y para escribir el resultado de nuevo en dicho píxel correspondiente de la segunda área de memoria, formando de este modo, en el píxel de la segunda área de memoria después de que se hayan leído dichos tres píxeles, el valor del píxel para dichos 2x2 píxeles que no está almacenado en la primera área de memoria; y

en el que dicho módulo de lectura y de escritura está configurado, cuando se lee, de acuerdo con las primera y segunda señales de dirección retardadas, cada uno sucesivamente de dichos tres de los 2x2 píxeles que están almacenados en la primera área de memoria, para sumar el valor de cada píxel leído al valor del píxel correspondiente en la segunda memoria y para escribir el resultado de nuevo en la segunda área de memoria, restableciendo de este modo, en el píxel de la segunda área de memoria después de que se hayan leído dichos tres píxeles, el valor original del píxel igual a la suma de los 2x2 píxeles correspondientes en la primera capa de la imagen;

incluyendo además dicho módulo de lectura y de escritura un selector (58) que está configurado para dar salida secuencialmente a los valores de los tres de dichos 2x2 píxeles de la primera capa de la imagen que están almacenados en la primera área de memoria y el valor del píxel correspondiente en la segunda área de memoria para el valor del píxel para dichos 2x2 píxeles de la primera capa de la imagen que no está almacenado en la primera área de memoria.

2. Método de funcionamiento de un dispositivo de almacenamiento para almacenar una imagen codificada jerárquicamente que presenta por lo menos una primera y una segunda capas de datos de imagen, proporcionando dicha primera capa la definición más alta de la imagen y presentando la segunda capa un número menor de píxeles y proporcionando una definición menor que la primera capa de la imagen, en el que 2x2 píxeles en la primera capa de la imagen se corresponden con un píxel en la segunda capa de la imagen, formándose dicho un píxel en la segunda capa de la imagen mediante la suma de los 2x2 píxeles correspondientes en la primera capa de la imagen; comprendiendo dicho dispositivo:

una primera área de memoria (2) que presenta una capacidad de memoria para almacenar 3/4 de los píxeles de la primera capa de la imagen, de tal manera que un píxel en cada uno de dichos 2x2 píxeles en la imagen de primera capa correspondiente a un píxel en la imagen de segunda capa no se almacena en la primera área de memoria; en el que las direcciones de los píxeles en la primera área de memoria se corresponden con sus posiciones respectivas en la imagen, dividiéndose dicha primera área de memoria en unos primer y segundo bloques, en el que los primer y segundo bloques son direccionables basándose en cada bloque individual proporcionando un primer terminal de direcciones en la primera área de memoria para el primer bloque y un segundo terminal de direcciones en la primera área de memoria para el segundo bloque;

una segunda área de memoria (3) adaptada para almacenar la segunda capa de la imagen, en el que dicha segunda área de memoria está dividida en unos primer y segundo bloques correspondientes respectivamente a los primer y segundo bloques de la primera área de memoria, en el que los primer y segundo bloques de la segunda área de memoria son direccionables basándose en cada bloque individual proporcionando un primer terminal de direcciones en la segunda área de memoria para el primer bloque y un segundo terminal de direcciones en la segunda área de memoria para el segundo bloque;

en el que el primer y el segundo bloques de la primera área de memoria almacenan cada 2N líneas alternas de la primera capa de la imagen respectivamente, el que N es un número natural, y los primer y segundo bloques de la segunda área de memoria almacenan cada N líneas alternas correspondientes de la segunda capa de la imagen respectivamente;

un módulo de direccionamiento [1] y un módulo de lectura y de escritura (5) ;

comprendiendo dicho método:

el módulo de direccionamiento que direcciona simultáneamente los bloques de dichas primera y segunda áreas de memoria de acuerdo con unas primera y segunda señales de dirección, en el que dicha primera señal de dirección y dicha segunda señal de dirección se corresponden con las posiciones horizontales y verticales de un píxel para dicha imagen de entrada, explorando así el módulo de direccionamiento secuencialmente a través de las líneas de los datos de imagen y proporcionando simultáneamente:

(a) una primera y una segunda señal de dirección actual para un píxel en uno de los primer o segundo bloques en la primera área de memoria y simultáneamente una primera y una segunda señal de dirección actual para un píxel correspondiente en el bloque correspondiente de la segunda área de memoria, y (b) una primera y una segunda señal de dirección retardada para un píxel en el otro de los primer o segundo bloques en la primera área de memoria y simultáneamente una primera y una segunda señal de dirección retardada, para un píxel correspondiente en el bloque correspondiente de la segunda área de memoria;

en el que la primera y la segunda señales de dirección para la segunda área de memoria comprenden la parte de la primera y la segunda señales de dirección correspondientes para la primera área de memoria excluyendo el bit menos significativo, y en el que las primera y segunda señales de dirección retardadas están retardadas en 2N líneas de la exploración secuencial; y

el módulo de lectura y escritura (5) simultáneamente lee desde o escribe en direcciones, designadas por dichas primera y segunda señales de dirección, en los bloques de dichas primera y segunda áreas de memoria;

en el que cuando dicho módulo de lectura y de escritura lee de acuerdo con la primera y la segunda señales de dirección actuales, cada uno sucesivamente de dichos tres de los 2x2 píxeles que están almacenados en la primera área de memoria, el módulo de lectura y de escritura resta el valor de cada píxel leído con respecto al valor del píxel correspondiente en la segunda memoria y escribe el resultado de nuevo en dicho píxel correspondiente de la segunda área de memoria, formando de este modo, en el píxel de la segunda área de memoria después de que se hayan leído dichos tres píxeles, el valor del píxel para dichos 2x2 píxeles que no está almacenado en la primera área de memoria; y

en el que cuando dicho módulo de lectura y de escritura lee de acuerdo con las primera y segunda señales de dirección retardadas, cada uno sucesivamente de dichos tres de los 2x2 píxeles que están almacenados en la primera área de memoria, el módulo de lectura y de escritura suma el valor de cada píxel leído al valor del píxel correspondiente en la segunda memoria y escribe el resultado de nuevo en la segunda área de memoria, restableciendo de este modo, en el píxel de la segunda área de memoria después de que se hayan leído dichos tres píxeles, el valor original del píxel igual a la suma de los 2x2 píxeles correspondientes en la primera capa de la imagen;

en el que dicho módulo de lectura y de escritura incluye además un selector (58) que da salida secuencialmente a los valores de los tres de dichos 2x2 píxeles de la primera capa de la imagen que están almacenados en la primera área de memoria y el valor del píxel correspondiente en la segunda área de memoria para el valor del píxel para dichos 2x2 píxeles de la primera capa de la imagen que no está almacenado en la primera área de memoria.

Patentes similares o relacionadas:

Dispositivo de procesamiento de información, método de procesamiento de información, y programa de procesamiento de información, del 24 de Junio de 2020, de RAKUTEN, INC: Un servidor de mercado en línea que comprende un controlador de sistema que comprende un extractor , un medio de configuración , un medio de disposición […]

Esquema de carga para registro compartido en GPU, del 19 de Febrero de 2020, de QUALCOMM INCORPORATED: Un procedimiento para almacenar datos, comprendiendo el procedimiento: determinar si los datos de una variable para una pluralidad de ítems gráficos son los mismos, […]

Dispositivo de salida de vídeo, dispositivo de observación de vídeo en 3D, dispositivo de presentación visual de vídeo y método de salida de vídeo, del 20 de Septiembre de 2017, de Sony Interactive Entertainment Inc: Un aparato de salida de vídeo, que comprende: Una unidad de clasificación de objetos configurada para clasificar objetos colocados […]

Dispositivo de presentación de estados y método de presentación de dispositivo de presentación de estados, del 31 de Mayo de 2017, de MITSUBISHI ELECTRIC CORPORATION: Un dispositivo de presentación de estados que comprende: una unidad de presentación de cristal líquido; una unidad de procesamiento […]

Dispositivo de presentación de estados y método de presentación de dispositivos de presentación de estados, del 8 de Marzo de 2017, de MITSUBISHI ELECTRIC CORPORATION: Un dispositivo de presentación de estados que comprende: una unidad de presentación de cristal líquido; y una unidad de […]

Establecimiento de llamada de telecomunicación de medios mixtos, del 18 de Marzo de 2016, de 3G Licensing S.A: Estación móvil apta para videotelefonía en respuesta a una interrupción de una llamada en curso de telecomunicaciones de medios mixtos, comprendiendo […]

Establecimiento de llamada de telecomunicación de medios mixtos, del 18 de Marzo de 2016, de 3G Licensing S.A: Estación móvil apta para videotelefonía en respuesta a una interrupción de una llamada en curso de telecomunicaciones de medios mixtos, comprendiendo […]

Dispositivo de reproducción, método de reproducción y programa para reproducción estereoscópica, del 11 de Marzo de 2015, de PANASONIC CORPORATION: Un aparato de reproducción que realiza reproducción estereoscópica, que comprende: un decodificador de vídeo (5a, 5b) que puede utilizarse para obtener fotogramas de vídeo […]

DISPOSITIVO Y PROCEDIMIENTO DE REPRESENTACION, del 1 de Marzo de 2008, de ROBERT BOSCH GMBH: Dispositivo de representación con una unidad de cálculo , en el que la unidad de cálculo presenta una entrada de datos , a través de la cual se ponen informaciones […]

DISPOSITIVO Y PROCEDIMIENTO DE REPRESENTACION, del 1 de Marzo de 2008, de ROBERT BOSCH GMBH: Dispositivo de representación con una unidad de cálculo , en el que la unidad de cálculo presenta una entrada de datos , a través de la cual se ponen informaciones […]