Método de desmodulación de señal y aparato de desmodulación de señal.

Un método para proporcionar un medio de registro en el cual está almacenada una cadena de códigos basada enN bits convertida a partir de una cadena de datos basada en M bits,

en donde M y N son números enteros que tienenuna relación de M

Tipo: Patente Europea. Resumen de patente/invención. Número de Solicitud: E01120568.

Solicitante: SONY CORPORATION.

Nacionalidad solicitante: Japón.

Dirección: 7-35, KITASHINAGAWA 6-CHOME SHINAGAWA-KU TOKYO JAPON.

Inventor/es: OKAZAKI, TORU, YOSHIMURA, SHUNJI.

Fecha de Publicación: .

Clasificación Internacional de Patentes:

- H03M5/14 ELECTRICIDAD. › H03 CIRCUITOS ELECTRONICOS BASICOS. › H03M CODIFICACION, DECODIFICACION O CONVERSION DE CODIGO, EN GENERAL (por medio de fluidos F15C 4/00; convertidores ópticos analógico/digitales G02F 7/00; codificación, decodificación o conversión de código especialmente adaptada a aplicaciones particulares, ver las subclases apropiadas, p. ej. G01D, G01R, G06F, G06T, G09G, G10L, G11B, G11C, H04B, H04L, H04M, H04N; cifrado o descifrado para la criptografía o para otros fines que implican la necesidad de secreto G09C). › H03M 5/00 Conversión de la forma de la representación de dígitos individuales. › Representación del código, p. ej. transición, dependiendo para un elemento binario dado de la información de uno o varios elementos binarios adyacentes, p. ej. código de modulación de retardo, código de doble densidad.

- H03M7/46 H03M […] › H03M 7/00 Conversión de un código, en el cual la información está representada por una secuencia dada o por un número de dígitos, en un código en el cual la misma información está representada por una secuencia o por un número de dígitos diferentes. › Conversión en o a partir de códigos de coordenada diferencial, es decir, por representación del número de dígitos consecutivos o grupos de dígitos del mismo tipo con ayuda de una palabra código y de un dígito representativo de este tipo.

- H04L25/49 H […] › H04 TECNICA DE LAS COMUNICACIONES ELECTRICAS. › H04L TRANSMISION DE INFORMACION DIGITAL, p. ej. COMUNICACION TELEGRAFICA (disposiciones comunes a las comunicaciones telegráficas y telefónicas H04M). › H04L 25/00 Sistemas de banda base. › con conversión de código al transmisor; con predistorsión; con inserción de intervalos muertos para obtener un espectro de frecuencia deseado; con al menos tres niveles de amplitud.

PDF original: ES-2389937_T3.pdf

Fragmento de la descripción:

Método de desmodulación de señal y aparato de desmodulación de señal.

CAMPO TÉCNICO Esta invención se refiere a un método de desmodulación de señales y a un aparato de desmodulación de señales que se utilizan para reproducir señales digitales, tales como señales de voz digitales, señales de vídeo digitales y datos digitales, en un medio de registro, y, por ejemplo, un método de desmodulación de señales y un aparato de desmodulación de señales que pueden adaptarse a un dispositivo maestro para un disco óptico de sólo lectura o un dispositivo de registro/reproducción para un disco óptico reescribible.

TÉCNICA ANTERIOR Cuando se registran señales digitales, tales como señales de voz digitales, señales de vídeo digitales o datos digitales, se agregan primero datos de código de corrección de errores a las señales digitales, y los datos resultantes son encaminados a un circuito de modulación en donde son convertidos por codificación de canal en el código adecuado a las características de un sistema de registro/reproducción.

Un disco óptico, tal como un disco compacto (CD) , es un medio de registro que tiene un amplio campo de aplicación como medio de empaquetamiento para información de imagen o como dispositivo de almacenaje para un ordenador. El sistema de disco óptico reproduce señales grabadas sobre una superficie reflectante del disco a través de un substrato transparente que tiene un espesor del orden 1, 2 mm. Sobre el disco compacto se registra información, tal como señales de audio digitalizadas, señales de vídeo digitalizadas o datos digitales. En este caso, se agregan los datos de código de corrección de errores a las señales digitales, y los datos resultantes son encaminados a un circuito de modulación en donde son convertidos por una denominada codificación de canal en datos de código adecuados a las características del sistema de registro/reproducción.

El formato de señal del sistema de disco compacto (CD) antes mencionado se resume en la forma siguiente:

frecuencia de muestreo 44, 1 kHz número de bits cuantizadores 16 (lineal) sistema de modulación EFM tasa de bits de canal 4, 3218 Mb/s sistema de corrección de error CIRC tasa de transmisión de datos 2, 034 Mb/s.

El sistema de modulación empleado es un sistema de conversión 8-14 o sistema EFM.

Con el EFM, un código de entrada de 8 bits, denominado seguidamente símbolo, se convierte en un código de 14 bits de canal, al cual se agregan una señal de sincronización de trama de 24 bits de canal y un subcódigo de 14 bits de canal, y los códigos contiguos se interconectan por medio de bits de fusión de 3 bits de canal. Los datos resultantes son registrados por el sistema de modulación NRZI.

La figura 1 muestra una estructura de trama del sistema CD.

Haciendo referencia a la figura 1, datos de 24 símbolos (señales musicales) y paridad de 8 símbolos, que entran en un circuito de modulación desde un codificador de código Reed-Solomon de entrelazamiento cruzado (CIRC) durante una trama de sincronismo (dominios de valor de seis muestras, con seis muestras en cada uno de los canales L y R, siendo cada muestra datos de 16 bits) se transforman en 14 bits de canal y se conectan por medio de bits de fusión de tres bits de canal para dar 588 bits de canal por trama. Los datos resultantes son registrados por el sistema NRZI a una tasa de bits de canal de 4, 3218 Mbps.

Los símbolos respectivos que entran en el circuito de modulación son transformados, con referencia a una tabla de búsqueda compuesta de una ROM, en un patrón de bits de canal en el que el número de “0s” entre “1” y “1” no es menor que 2 ni mayor que 10. El patrón de bits de canal de una señal de sincronización de trama Sf es “100000000001000000000010” en expresión binaria. En cuanto al patrón de bits de fusión, se selecciona uno de entre “000”, “001”, “010” y “100”. Cada trama de subcodificación está constituida por 98 tramas. Como subcódigo para los tramas cero y primera, se agregan las señales de sincronismo de subcódigo SO (= “00100000000001” y S1 (= “00000000010010”) (véase la figura 2) .

La figura 3 muestra, para un valor de muestra típico de datos de entrada, un patrón de bits de canal después de EFM y una variación de suma digital (DSV) .

Cada muestra de 16 bits se divide en 8 bits superiores y 8 bits inferiores, cada uno de los cuales se introduce en el circuito de modulación a través de un codificador CIRC para conversión 8-14 a fin de producir bits de información de 14 bits de canal. No menos de 2 ni más de 10 “0s” están interpuestos entre “1” y “1” de los bits de información, tal como se ha descrito anteriormente. Se selecciona uno de los bits de fusión “000”, “001”, “010” y “100”. Se observa esta regla en todo momento en las porciones de conexión de los 14 bits de información, con lo que se generan señales EFM basadas en 17 bits de canal y se da salida a estas señales desde el circuito de modulación a 4, 3218 Mbps. El número de bits de canal es 27 en el caso de la señal de sincronización de cuadro Sf.

Dado que no menos de 2 y no más de 10 bits de canal están interpuestos entre un bit de canal opcional “1” y el siguiente bit de canal “1”, el período durante el cual continúa el nivel alto o el nivel bajo de la forma de onda de registro NRZI, es decir, la longitud de onda de registro, es necesariamente no menor que 3T y no mayor que 11T (véase la figura 3) .

En este caso, la longitud de onda de registro más corta es 3T y la longitud de onda de registro más larga es 11T, siendo T un período de un reloj de canal de 4, 3218 MHz. Esto se denomina seguidamente regla 3T ~ 11T de la regulación de modulación EFM.

El valor o variación de suma digital (DSV) se considera ahora como un índice del equilibrio de cc de la forma de onda de registro NRZI. La DSV se da como una integral de tiempo de la forma de onda de registro. Es decir, la variante de la DSV, cuando el nivel alto de la forma de onda de registro ha continuado durante un tiempo unidad T, es +1, mientras que la variante de la DSV, cuando el nivel bajo de la forma de onda de registro ha continuado durante un tiempo unidad T, es -1.

El cambio de tiempo de DSV, cuando el valor inicial de DSV en el instante to se supone igual a cero, se da en la porción más inferior de la figura 3. La señal modulada durante el tiempo desde ti hasta t2 no queda determinado de forma singular por el patrón de 17 bits de canal “01000001000001001”, sino que depende del nivel de señales moduladas en el instante t1, es decir, del nivel último de la forma de onda de señal modulada durante el intervalo de tiempo desde el instante to hasta el instante ti (denominado seguidamente CWLL) .

Así, la forma de onda de señal modulada ilustrada es aquella para la que el CWLL en el instante to está a un nivel bajo (CWLL = “0”) . La forma de onda de señal modulada para CWLL = “1” (nivel alto) se invierte respecto del patrón para CWLL = “0”, de modo que los niveles alto y bajo se invierten a niveles bajo y alto, respectivamente.

Análogamente, la DSV se incrementa o disminuye también dependiendo del CWLL, de tal manera que si CWLL = “0” en el instante t0, la variante de DSV con el patrón de información “01000100100010” (denominado seguidamente 14 NWD) , es decir, la variante de DSV durante el período de tiempo desde t0 hasta t0+14, es +2, como se muestra en la figura 3. Recíprocamente, si CWLL = “1” en el instante t0, 14 NWD = -2. La variante de DSV desde el instante t0+14 hasta t1+14 se denomina 17 NWD.

Se explican ahora los bits de fusión insertados desde el instante t0+14 hasta el instante t1. De los cuatro bits de margen “000”, “001”, “010” y “100” no pueden insertarse “001” o “100” conforme a la regla 3T ~ 11T antes mencionada, de tal manera que solamente puede insertarse “010” o “000”. Es decir, si el número de “0s” en el extremo trasero del patrón de bits de información anterior, emitido antes del bit de fusión es B, y el número de “0s” en el extremo delantero del patrón de bits de información en curso... [Seguir leyendo]

Reivindicaciones:

1. Un método para proporcionar un medio de registro en el cual está almacenada una cadena de códigos basada en N bits convertida a partir de una cadena de datos basada en M bits, en donde M y N son números enteros que tienen una relación de M<N, comprendiendo el método:

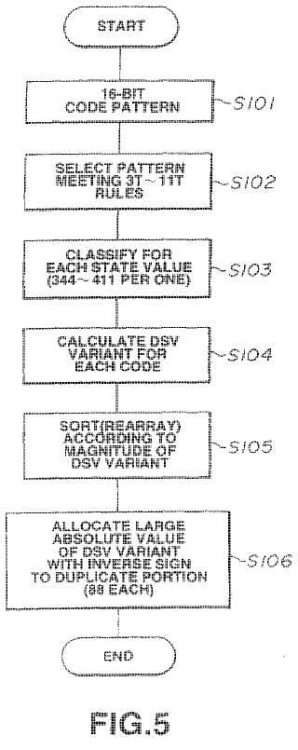

recibir (S1) la cadena de datos basada en M bits como una primera palabra de datos de una pluralidad de palabras de datos; convertir (S2..S12) la primera palabra de datos en una primera palabra de código a partir de una primera tabla de una pluralidad de tablas de palabras de código primarias y secundarias (Ta; Tb) ; determinar (10) si la pluralidad de tablas de palabras de código secundarias (Tb) puede ser utilizada para convertir una segunda palabra de datos en una segunda palabra de código basándose en un valor de la segunda palabra de datos, en donde para los selectores de determinación (11, 12) son instruidos para entrar en el modo de control de la DSV si un valor de señal de la segunda palabra de datos es menor que un valor predeterminado; si la pluralidad de tablas de palabras de código secundarias (Tb) puede ser utilizada para convertir la segunda palabra de datos, entonces determinar (20) sí o no, para disminuir la DSV acumulativa, la pluralidad de tablas de palabras de código primarias (Ta) o la pluralidad de tablas de palabras de código secundarias (Tb) ha de ser utilizada para convertir la segunda palabra de datos en una segunda palabra de código, en donde si la pluralidad de tablas de palabras de código secundarias (Tb) no puede ser utilizada para convertir la segunda palabra de datos, la pluralidad de tablas de código primarias (Ta) se determina que sea utilizada para convertir la segunda palabra de datos en una segunda palabra de código; determinar (21, 26, 27) basándose en un valor de estado (S) asociado con la primera palabra de código, cuál de la pluralidad de tablas de palabras de códigos primarias (Ta) o cuál de la pluralidad de tablas de palabras de código secundarias (Tb) tiene que ser utilizada para convertir la segunda palabra de datos en una segunda palabra de código; y convertir (21, 23) la segunda palabra de datos en una segunda palabra de código a partir de una de la pluralidad de tablas de palabras de código primarias o secundarias (Ta; Tb) , en donde dichas tablas de palabras de código primarias (Ta) que contienen palabras de código en correspondencia una a una con una pluralidad de palabras de datos disponible, en donde, en cada tabla de palabras de código primaria, la palabra de código que tiene la DSV absoluta más grande está dispuesta asociada con una palabra de datos más pequeña; dichas tablas de palabras de código secundarias (Tb) conteniendo palabras de código que se corresponden tan solo con una porción de dicha pluralidad de palabras de datos disponible y cuyos valores de DSV de palabras de código son opuestos en signo del valor de DSV a los valores de DSV asociados con las palabras de código de las tablas de palabras de código primarias (Ta) , en donde, en cada tabla de palabras de código secundaria (Tb) , la palabra de código que tiene la DSV absoluta más grande está dispuesta asociada con una palabra de datos más pequeña, y almacenar la primera y segunda palabra de código como la cadena de códigos basada en N bits en un medio de registro de disco óptico.

2. El método tal como se reivindica en la reivindicación 1, en el que en las tablas de palabras de código primarias y secundarias (Ta; Tb) , el valor de estado asociado a cada palabra de código indica cuál de la pluralidad de tablas de palabras de código primarias (Ta) o cuál de la pluralidad de tablas de palabras de código secundarias (Tb) tiene que ser utilizada para convertir la segunda palabra de datos en una segunda palabra de código, y el paso de determinar (21, 26, 27) cuál de la pluralidad de tablas de palabras de código tiene que ser utilizada por la segunda palabra de datos que comprende identificar (26) el valor de estado (S) asociado con la primera palabra de código.

3. El método tal como se reivindica en la reivindicación 1 ó en la reivindicación 2, que comprende además un paso (S10) de actualizar un valor de variación de suma digital acumulativa.

4. El método tal como se reivindica en cualquiera de las reivindicaciones 1 a 3, en el que cada una de las palabras de código en las tablas de palabras de código primarias y secundarias (Ta; Tb) cumple las reglas de modulación de tener una longitud de onda minima de 3T y una longitud de onda máxima de 11 T, con T representando un ciclo de un reloj de canal.

5. El método tal como se reivindica en cualquiera de las reivindicaciones 1 a 4, en el que la pluralidad de tablas de palabras de código primarias y secundarias (Ta; Tb) está constituida por cuatro grupos de tabla de palabras de código primarias y secundarias (T1a..T4a; T1b..T4b) .

6. El método tal como se reivindica en la reivindicación 5, en el que un primer grupo de las cuatro tablas de palabras de código primarias (T1a..T4a; T1b..T4b) está compuesto de palabras de código que empiezan al menos con dos ceros '00'.

7. El método tal como se reivindica en las reivindicaciones 5 ó 6, en el que un segundo grupo de las cuatro tablas de palabras de código primarias y secundarias (T1a..T4a; T1b..T4b) está compuesto de palabras de códigos que empiezan con un máximo de 5 ceros, “00000”, y un primer bit del más significante bit (MSB) del código y un cuarto bit del menos significante bit (LSB) del código que es cero “0”.

8. El método tal como se reivindica en cualquiera de las reivindicaciones 5 a 7, en el que un tercer grupo de las cuatro tablas de palabras de código primarias y secundarias (T1a..T4b; T1b..T4b) está compuesto de palabras de código que empiezan con un máximo de 5 ceros “00000”, y uno de entre un primer bit del más significante bit (MSB) de la palabra de código y un cuarto bit del menos significante bit (LSB) de la palabra de código que es “1”.

9. El método tal como se reivindica en cualquiera de las reivindicaciones 5 a 8, en el que un cuarto grupo de las cuatro tablas de palabras de código primarias y secundarias (T1a..T4a; T1b..T4b) está compuesto de palabras de código que empiezan con “1” ó “01”.

10. El método tal como se reivindican en la reivindicación 6, en el que el paso de determinar cuál de la pluralidad de las tablas de palabras de código tiene que ser utilizada comprende un paso de seleccionar a partir del primer grupo de códigos siguientes si una palabra de código actual finaliza con “1” ó “10”.

11. El método tal como se reivindica en la reivindicación 8, en el que el paso de determinar cuál de la pluralidad de las tablas de palabras de código tiene que ser utilizada comprende un paso de seleccionar a partir del segundo o tercer grupo de códigos siguientes si un código actual finaliza con dos a cinco ceros “00” a “00000”.

12. El método tal como se reivindica en la reivindicación 9, en el que el paso de determinar cuál de la pluralidad de las tablas de palabras de código tiene que ser utilizada comprende un paso de seleccionar el cuarto grupo de códigos siguiente si un código actual finaliza con seis a nueve ceros “000000” a “000000000”.

13. El método tal como se reivindica en la reivindicación 10, que comprende un paso de seleccionar una palabra de código a partir de primer grupo de la pluralidad de tablas de palabras de código después de recibir un patrón de sincronización.

14. El método tal como se reivindica en cualquiera de las reivindicaciones 1 a 13, en el que cada una de la pluralidad de tablas de palabras de código tiene una porción a la cual se le asigna un mismo código para diferentes datos de entrada, teniendo el mismo código diferentes valores de estado (S) .

15. El método tal como se reivindica en la reivindicación 14, en el que la pluralidad de tablas de palabras de código tienen porciones a las que se le asigna un mismo código para el mismo dato de entrada, teniendo el mismo código asignado el mismo valor de estado.

16. Un dispositivo para proporcionar un medio de registro en el cual está almacenada una cadena de códigos basada en N bits convertida a partir de una cadena de datos basada en M bits, en donde M y N son números enteros que tienen una relación de M<N, comprendiendo el dispositivo:

medios (S1) para recibir la cadena de datos basada en M bits como una primera palabra de datos de una pluralidad de palabras de datos; medios para convertir (S2..S12) la primera palabra de datos en una primera palabra de código a partir de una primera tabla de una pluralidad de tablas de palabras de código primarias y secundarias (Ta; Tb) ; medios (10) para determinar sí o no la pluralidad de tablas de palabras de código secundarias (Tb) puede ser utilizada para convertir una segunda palabra de datos en una segunda palabra de código basándose en un valor de la segunda palabra de datos, en donde para los selectores de determinación (11, 12) son instruidos para entrar en el modo de control DSV si un valor de señal de la segunda palabra de datos es menor que un valor predeterminado; medios (20) para determinar sí o no, para disminuir la DSV acumulativa, la pluralidad de tablas de palabras de código primarias (Ta) o la pluralidad de tablas de palabras de código secundarias (Tb) ha de ser utilizada para convertir la segunda palabra de datos en una segunda palabra de código, si la pluralidad de tablas de palabras de código secundarias (Tb) puede ser utilizada para convertir la segunda palabra de datos, en donde, si la pluralidad de tablas de palabras de código secundarias (Tb) no puede ser utilizada para convertir la segunda palabras de datos, la pluralidad de tablas de código primarias (Ta) se determina que sea utilizada para convertir la segunda palabra de datos en una segunda palabra de código; medios (21, 26, 27) para determinar, basándose en un valor de estado (S) asociado con la primera palabra de código, cuál de la pluralidad de tablas de palabras de códigos primarias (Ta) o cuál de la pluralidad de tablas de palabras de código secundarias (Tb) tiene que ser utilizada para convertir la segunda palabra de datos en una segunda palabra e código;

medios (21, 23) para convertir la segunda palabra de datos en una segunda palabra de código a partir de una de la pluralidad de tablas de palabras de código primarias o secundarias (Ta; Tb) ; en donde dichas tablas de palabras de código primarias (Ta) que contienen palabras de código en correspondencia una a una con una pluralidad de palabras de datos disponible, en donde, en cada tabla de palabras de código primaria, la palabra de código que tiene la DSV absoluta más grande está dispuesta asociada con una palabra de datos más pequeña; dichas tablas de palabras de código secundarias (Tb) que contienen palabras de código las cuales se corresponden tan solo con una porción de dicha pluralidad de palabras de datos disponible y cuyos valores de DSV de palabras de código son opuestos en signo del valor de DSV a los valores de DSV asociados con las palabras de código de las tablas de palabras de código primarias (Ta) , en donde, en cada tabla de palabras de código secundarias (Tb) , la palabra de código que tiene la DSV absoluta más grande está dispuesta asociada con una palabra de datos más pequeña, y medios de grabación para grabar la primera y segunda palabra de código como la cadena de códigos basada en N bits en un medio de registro de disco óptico.

17. El dispositivo tal como se reivindica en la reivindicación 16, en el que en las tablas de palabras de código primarias y secundarias (Ta; Tb) , el valor de estado asociado a cada palabra de código indica cuál de la pluralidad de tablas de palabras de código primarias (Ta) o cuál de la pluralidad de tablas de palabras de código secundarias (Tb) tiene que ser utilizada para convertir la segunda palabra de datos en una segunda palabra de código, y medios (21, 26, 27) para determinar cuál de la pluralidad de tablas de palabras de código tiene que ser utilizada por la segunda palabra de datos que comprende identificar (26) el valor de estado (S) asociado con la primera palabra de código.

18. El dispositivo tal como se reivindica en la reivindicación 16 ó en la reivindicación 17, que comprende además medios (24) para actualizar un valor de variación de suma digital acumulativa.

19. El dispositivo tal como se reivindica en cualquiera de las reivindicaciones 16 a 18, que comprende además medios (26, 27) para mantener y actualizar un valor de estado (S) .

20. El dispositivo tal como se reivindica en cualquiera de las reivindicaciones 16 a 19, en el que las palabras de código en cada una de las tablas de palabras de código primarias y secundarias (Ta; Tb) tienen una longitud de onda minima de 3T y una longitud de onda máxima de 11 T, con T representando un ciclo de un reloj de canal.

21. El dispositivo tal como se reivindica en cualquiera de las reivindicaciones 16 a 20, en el que la pluralidad de tablas de palabras de código primarias y secundarias (Ta; Tb) está constituida por cuatro grupos de tabla de palabras de código primarias y secundarias (T1a..T4a; T1b..T4b) .

22. El dispositivo tal como se reivindica en la reivindicación 21, en el que un primer grupo de códigos (T1a; T1b) está compuesto de palabras de código que empiezan al menos con dos ceros '00'.

23. El dispositivo tal como se reivindica en la reivindicación 21 ó en la reivindicación 22, en el que un segundo grupo de códigos (T2a; T2b) está compuesta de palabras de códigos que empiezan con un máximo de 5 ceros “00000”, un primer bit del más significante bit (MSB) del código y un cuarto bit del menos significante bit (LSB) del código que es cero (0) .

24. El dispositivo tal como se reivindica en cualquiera de las reivindicaciones 21 a 23, en el que un tercer grupo de códigos (T3a; T3b) está compuesto de palabras de código que empiezan con un máximo de 5 ceros “00000”, uno o ambos de entre un primer bit del más significante bit (MSB) de la palabra de código y un cuarto bit del menos significante bit (LSB) de la palabra de código que es “1”.

25. El dispositivo tal como se reivindica en cualquiera de las reivindicaciones 21 a 24, en el que un cuarto grupo (T4a; T4b) está compuesta de códigos que empiezan con “1” ó “01”.

26. El dispositivo tal como se reivindica en cualquiera de las reivindicaciones 21 a 25, en el que cuando un código actual finaliza con “1” ó “01”, el valor de estado (S) se vuelve 1, con un código siguiente que es seleccionado del primer grupo de códigos (T1a; T1b) .

27. El dispositivo tal como se reivindica en cualquiera de las reivindicaciones 21 a 26, en el que cuando un código actual finaliza con dos a cinco ceros, ''00'' a ''00000'', el valor de estado se convierte en 2 'o 3, con un valor de estado (S) que es seleccionado del segundo o tercer grupo de códigos (T2a; T2b, T3a; T3b) .

28. El dispositivo tal como se reivindica en cualquiera de las reivindicaciones 21 a 27, en el que cuando un código actual finaliza con seis a nueve ceros, "000000" a "000000000", el valor de estado (S) se vuelve 4,

con un código siguiente que es seleccionado del cuarto grupo de códigos (T4a; T4b) .

29. El dispositivo tal como se reivindica en cualquiera de las reivindicaciones 21 a 28, en el que una palabra de código que sigue un patrón de sincronización es seleccionado del primer grupo de códigos (T1a; T1b) .

30. El dispositivo tal como se reivindica en cualquiera de las reivindicaciones 21 a 29, en el que cada una de la pluralidad de tablas de palabras de código primarias y secundarias (Ta; Tb) tiene una porción a la cual se le asigna un mismo código para diferentes datos de entrada, teniendo el mismo código diferentes valores de estado (S) .

31. El dispositivo tal como se reivindica en cualquiera de las reivindicaciones 21 a 30, en el que la pluralidad de tablas de palabras de código primarias y secundarias (Ta; Tb) tiene porciones a las que se le asigna el mismo código para el mismo dato de entrada, teniendo el mismo código asignado el mismo valor de estado (S) .

32. Un método para reproducir un medio de registro en el cual está almacenada una cadena de códigos basada en N bits convertida a partir de una cadena de datos basada en M bits, en donde M y N son números enteros que tienen una relación de M<N, comprendiendo el método los pasos de:

reproducir una cadena de códigos de entrada basada en N bits como una primera palabra de código a partir de un medio de registro de disco óptico; convertir inversamente (S22..S29) la primera palabra de código en una primera palabra de datos a partir de una primera tabla de una pluralidad de tablas de palabras de código primarias y secundarias (Ta; Tb) ; y suministrar (S24, S28, S29) una cadena de datos basada en M bits como un resultado de desmodulación; determinar (S23) sí o no la pluralidad de tablas de palabras de código secundarias (Tb) puede ser utilizada para convertir inversamente una segunda palabra de código en una segunda palabra de datos; si la pluralidad de tablas de palabras de código secundarias (Tb) puede ser utilizada para convertir inversamente la segunda palabra de código, entonces determinar (S27, S35) , sí o no la pluralidad de tablas de palabras de código primarias (Ta) o la pluralidad de tablas de palabras de código secundarias (Tb) ha de ser utilizada para convertir inversamente la segunda palabra de código en una segunda palabra de datos, en donde si la pluralidad de tablas de palabras de código secundarias (Tb) no puede ser utilizada para convertir inversamente la segunda palabra de código, la pluralidad de tablas de código primarias (Ta) se determina que sea utilizada para convertir inversamente la segunda palabra de código en una segunda palabra de datos; determinar si la descodificación inequívoca es posible y en caso de que no lo sea, comprobar los bits 1º y 13º y deducir los valores de estado (S) correspondientes; determinar (35) basándose en un valor de estado (s) asociado con la primera palabra de código, cuál de la pluralidad de las tablas de palabras de código primarias (Ta) o cuál de las pluralidad de las tablas de palabras de código secundarias (Tb) tiene que ser utilizada para convertir inversamente la segunda palabra de código en una segunda palabra de datos; y convertir inversamente la segunda palabra de código en una segunda palabra de datos de una de la pluralidad de tablas de palabras de datos primarias o secundarias (Ta; Tb) ; en donde dichas tabla de palabras de código primarias (Ta) contienen palabras de código en correspondencia una a una con una pluralida de palabras de datos disponible, en donde, en cada tabla de palabras de código primaria, la palabra de código que tiene la DSV absoluta más grande es dispuesta asociada con una palabra de datos más pequeña; y dichas tablas de palabras de código secundarias (Tb) contienen, para disminuir la DSV acumulativa, palabras de código que se corresponden solamente con una porción de dicha pluralidad de palabras de datos disponibles y cuyos valores de DSV de palabras de código son puestas en signo de los valores de DSV a los valores de DSV asociados con las palabras de código de las tablas de palabras de código primarias (Ta) , en donde en cada tabla de palabras de código secundaria (Tb) , la palabra de código que tiene la DSV absoluta más grande es dispuesta asociado con una palabra de datos más pequeña.

33. El método tal como se reivindica en la reivindicación 32, en el que las tablas de palabras de código primarias y secundarias (Ta; Tb) incluyen porciones a las que se les asocia diferentes palabras de datos con un mismo código de entrada.

34. El método tal como se reivindica en la reivindicación 33, en el que el mismo código de entrada para el que diferentes palabras de datos son asociadas, pertenece al primer grupo de códigos.

35. El método tal como se reivindica en cualquiera de las reivindicaciones 32 a 34, comprenden además los pasos de:

juzgar (S23) si un código de entrada es inequívocamente descodificable o no; leer (S25) un código siguiente al código de entrada que actualmente está siendo descodificado y comprobar

(S26) un estado del código siguiente cuando se juzga que el código de entrada no es inequívocamente descodificable; y determinar (S27) los datos de suministro para el código de entrada que actualmente está siendo descodificado en base al estado del siguiente código de entrada.

36. El método tal como se reivindica en cualquiera de las reivindicaciones 32 a 35, en el que el código de entrada tiene una longitud de onda minima de 3T y una longitud de onda máxima de 11 T, con T representando un ciclo de un reloj de canal.

37. El método tal como se reivindica en cualquiera de las reivindicaciones 32 a 36, en el que la pluralidad de tablas de palabras de código primarias y secundarias (Ta; Tb) está constituida por cuatro grupos (T1a..T4a; T1b..T4b) .

38. El método tal como se reivindica en la reivindicación 37, en el que las palabras de código en el primer grupo de códigos (T1a; T1b) empiezan al menos con dos ceros “00”.

39. El método tal como se reivindica en la reivindicación 37 ó en la reivindicación 38, en el que las palabras de código en el segundo grupo de códigos (T2a; T2b) empiezan con un máximo de 5 ceros “00000”, un primer bit del más significante bit (MSB) del código y un cuarto bit del menos significante bit (LSB) del código que es cero (0) .

40. El método tal como se reivindica en cualquiera de las reivindicaciones 37 a 39, en el que las palabras de código en el tercer grupo de códigos (T3a; T3b) empiezan con un máximo de 5 ceros “00000”, y uno

o ambos de entre un primer bit del más significante bit (MSB) de la palabra de código y un cuarto bit del menos significante bit (LSB) de la palabra de código que es “1”.

41. El método tal como se reivindica en cualquiera de las reivindicaciones 37 a 39, en el que las palabras de código en el cuarto grupo (T4a; T4b) empiezan con “1” ó “01”.

42. Un dispositivo para reproducir un medio de registro en el cual está almacenada una cadena de códigos basada en N bits convertida a partir de una cadena de datos basada en M bits, en donde M y N son números enteros que tienen una relación de M<N, comprendiendo el dispositivo:

medios para reproducir una cadena de códigos de entrada basada en N bits como una primera palabra de código a partir de un medio de registro de disco óptico; medios (S22..S29) para convertir inversamente la primera palabra de código en una primera palabra de datos a partir de una primera tabla de una pluralidad de tablas de palabras de código primarias y secundarias (Ta; Tb) ; y medios (S24, S28, S29) para suministrar una cadena de datos basada en M bits como un resultado de desmodulacion; medios (S23) para determinar sí o no la pluralidad de tablas de palabras de código secundarias (Tb) puede ser utilizada para convertir inversamente una segunda palabra de código en una segunda palabra de datos; medios (35) para determinar sí o no, la pluralidad de tablas de palabras de código primarias (Ta) o la pluralida de tablas de palabras de código secundarias (Tb) ha de ser utilizada para convertir inversamente la segunda palabra de código en una segunda palabra de datos, si la pluralidad de tablas de palabras de código secundarias (Tb) puede ser utilizada para convertir inversamente la segunda palabra de código, en donde, si la pluralidad de tablas de palabras de código secundarias (Tb) no puede ser utilizada para convertir inversamente la segunda palabra de código, la pluralidad de tablas de código primarias (Ta) se determina que sea utilizada para convertir inversamente la segunda palabra de código en una segunda palabra de datos; medios para determinar si la descodificación inequívoca es posible y en caso de que no lo sea, comprobar los bits 1º y 13º y deducir los valores de estado (S) correspondientes; medios (35) para determinar basándose en un valor de estado (s) asociado con la primera palabra de código, cuál de la pluralidad de las tablas de palabras de código primarias (Ta) o cuál de las pluralidad de las tablas de palabras de código secundarias (Tb) tiene que ser utilizada para convertir inversamente la segunda palabra de código en una segunda palabra de datos; y medios para convertir inversamente la segunda palabra de código en una segunda palabra de datos de una de la pluralidad de tablas de palabras de datos primarias o secundarias (Ta; Tb) ; en donde dichas tablas de palabras de código primarias (Ta) contienen palabras de código en correspondencia una a una con una pluralidad de palabras de datos disponible, en donde, en cada tabla de palabras de código primaria, la palabra de código que tiene la DSV absoluta más grande es dispuesta asociada con una palabra de datos más pequeña; y dichas tablas de palabras de código secundarias (Tb) contienen, para disminuir la DSV acumulativa, palabras de código que se corresponden solamente con una porción de dicha pluralidad de palabras de datos disponibles y cuyos valores de DSV de palabras de código son opuestas en signo de los valores de DSV a los valores de DSV asociados con las palabras de código de las tablas de palabras de código primarias (Ta) , en

donde en cada tabla de palabras de código secundaria (Tb) , la palabra de código que tiene la DSV absoluta más grande es dispuesta asociada con una palabra de datos más pequeña.

43. El dispositivo tal como se reivindica en la reivindicación 42, en el que las tablas de palabras de código primarias y secundarias (Ta; Tb) incluyen porciones a las que se les asocia diferentes palabras de datos con un mismo código de entrada.

44. El dispositivo tal como se reivindica en la reivindicación 43, en el que la pluralidad de tablas de palabras de código primarias y secundarias (Ta; Tb) está constituida por cuatro grupos (T1a..T4a; T1b..T4b) y el mismo código de entrada para el cual los diferentes datos que son asociadas pertenecen al mismo grupo de códigos.

45. El dispositivo tal como se reivindica en cualquiera de las reivindicaciones 42 a 44, que comprende además:

medios (S23) para juzgar si un código de entrada es inequívocamente descodificable o no con referencia a la tabla de conversión inversa; medios (S25) para leer un código siguiente al código de entrada que actualmente está siendo descodificado y comprobar (S26) un estado del código siguiente cuando se juzga que el código de entrada no es inequívocamente descodificable; y medios para determinar los datos de suministro para el código de entrada que actualmente está siendo descodificado en base al estado de un código de entrada siguiente.

46. El dispositivo de desmodulación tal como se reivindica en cualquiera de las reivindicaciones 42 a 45, en el que el código de entrada tiene una longitud de onda minima de 3T y una longitud de onda máxima de 11 T, con T representando un ciclo de un reloj de canal.

47. El dispositivo tal como se reivindica en cualquiera de las reivindicaciones 42 a 46, en el que la pluralidad de tablas de palabras de código primarias y secundarias (Ta; Tb) está constituida por cuatro grupos de tablas de palabras de código (T1a..T4a; T1b..T4b) .

48. El dispositivo tal como se reivindica en la reivindicación 47, en el que las palabras de código en el primer grupo de códigos (T1a; T1b) empiezan al menos con dos ceros “00”.

49. El dispositivo tal como se reivindica en la reivindicación 47 ó en la reivindicación 48, en el que las palabras de código en el segundo grupo de códigos (T2a; T2b) empiezan con un máximo de 5 ceros “00000”, y un primer bit del más significante bit (MSB) del código y el cuarto bit del menos significante bit (LSB) del código que es cero (0) .

50. El dispositivo de desmodulación tal como se reivindica en cualquiera de las reivindicaciones 47 a 49, en el que las palabras de código en el tercer grupo de códigos (T3a; T3b) empiezan con un máximo de 5 ceros “00000”, y uno

o ambos de entre un primer bit del más significante bit (MSB) de la palabra de código y un cuarto bit del menos significante bit (LSB) de la palabra de código que es “1”.

51. El dispositivo de desmodulación tal como se reivindica en cualquiera de las reivindicaciones 47 a 50, en el que las palabras de código en el cuarto grupo (T4a; T4b) empiezan con “1” ó “01”.

18 19 20 21 22 23 24 25 26 27 28 29 30 31 32

Patentes similares o relacionadas:

Ecualización inteligente para un sistema multifásico de tres transmisores, del 29 de Julio de 2020, de QUALCOMM INCORPORATED: Un sistema de tres transmisores para transmitir símbolos multifásicos sucesivos, que comprende:

un codificador configurado para codificar […]

Ecualización inteligente para un sistema multifásico de tres transmisores, del 29 de Julio de 2020, de QUALCOMM INCORPORATED: Un sistema de tres transmisores para transmitir símbolos multifásicos sucesivos, que comprende:

un codificador configurado para codificar […]

Comunicaciones en un sistema de dispositivos médicos, del 24 de Junio de 2020, de CARDIAC PACEMAKERS, INC.: Un dispositivo médico implantable que comprende: uno o más electrodos (114, 114'); un controlador acoplado al uno o más electrodos (114, […]

Método y sistema para una etiqueta de identificación por radiofrecuencia usando un protocolo de comunicación de conjunto reducido, del 3 de Junio de 2020, de SENSORMATIC ELECTRONICS, LLC: Un método para descodificar una señal recibida desde un lector de identificación por radiofrecuencia, RFID , comprendiendo el método: - recibir una señal […]

Recuperación de datos y reloj de doble velocidad de transferencia de datos N-factorial, del 18 de Marzo de 2020, de QUALCOMM INCORPORATED: Un procedimiento de comunicaciones de datos, que comprende: recibir una secuencia de símbolos de una pluralidad de hilos de señal […]

Intercambio energéticamente eficiente de tramas de datos, del 5 de Febrero de 2020, de INOVA SEMICONDUCTORS GMBH: Disposición de comunicación para el intercambio energéticamente eficiente de tramas de datos entre una unidad de mando (BE) y unidades de control […]

Procedimiento de distribución de datos y procedimiento de agregación de datos, y aparatos relacionados a los mismos, del 8 de Enero de 2020, de HUAWEI TECHNOLOGIES CO., LTD.: Un procedimiento de distribución de datos, que comprende: recibir un primer flujo de paquetes; dividir el primer flujo de paquetes […]

Señalización gestionada dúplex de banda base por división de tiempo, del 4 de Diciembre de 2019, de ViaSat, Inc: Un terminal de usuario de satélite configurado para comunicarse con un satélite , comprendiendo el terminal de usuario de satélite: una unidad interior […]

Recuperación de datos de reloj multifásico para una interfaz trifásica, del 20 de Noviembre de 2019, de QUALCOMM INCORPORATED: Un procedimiento de comunicaciones de datos, que comprende: configurar un circuito de recuperación de reloj para proporcionar una primera señal […]