SISTEMA Y METODO PARA LA RECONFIGURACION EN EL TIEMPO DE FUNCIONAMIENTO.

Un sistema de procesamiento digital de señales re-configurable,

que comprende:

un convertidor de serie a paralelo (4) que comprende al menos un bloque de retardo (5) y al menos un bloque de decimación (2) dispuesto para convertir una primera señal serie (x(n)) con una primera tasa de muestreo en una multiplicidad (L) de señales de subbandas en paralelo con una segunda tasa de muestreo, en el que la segunda tasa de muestreo es menor o igual que la primera tasa de muestreo;

bloques de procesamiento (PB0, PB1, PBL-1) dispuestos para procesar las señales de las subbandas para producir señales procesadas;

un controlador de configuración (1) dispuesto para modificar el factor de decimación (M) de cada uno de los bloques de decimación y para cargar una configuración dentro de la memoria (MEM) de un bloque de procesamien-to;

un convertidor de serie a paralelo (6) que comprende al menos un bloque de expansión (3), dispuesto el convertidor de paralelo a serie para recuperar a partir de las señales procesadas una segunda señal serie (y(n)) con una tasa de muestreo sustancialmente igual a la primera tasa de muestreo;

en el que en la operación normal del tiempo de funcionamiento el factor de decimación (M) de cada uno de los bloques de decimación (2) es igual al número (L) de señales de subbandas y cuando se requiere la reconfiguración en el tiempo de funcionamiento el controlador de configuración se dispone a disminuir el factor de decimación de modo que aumenta la segunda tasa de muestreo; cargar la configuración dentro de la memoria de un bloque de procesamiento; y aumentar el factor de decimación de nuevo para que sea igual que el número de señales de subbandas

Tipo: Patente Europea. Resumen de patente/invención. Número de Solicitud: E04253467.

Solicitante: MATSUSHITA ELECTRIC INDUSTRIAL CO., LTD..

Nacionalidad solicitante: Japón.

Dirección: MATSUSHITA IMP BUILDING 19TH FLOOR 1-3-7, SHIROMI CHUO-KU,OSAKA 540-6319.

Inventor/es: AL ADNANI,ADNAN PANASONIC BROADBAND COMMUNICATION.

Fecha de Publicación: .

Fecha Solicitud PCT: 10 de Junio de 2004.

Fecha Concesión Europea: 23 de Diciembre de 2009.

Clasificación Internacional de Patentes:

- H03H17/02F8A

- H03H17/02H

Clasificación PCT:

- G06F15/00 FISICA. › G06 CALCULO; CONTEO. › G06F PROCESAMIENTO ELECTRICO DE DATOS DIGITALES (sistemas de computadores basados en modelos de cálculo específicos G06N). › Computadores digitales en general (detalles G06F 1/00 - G06F 13/00 ); Equipo de procesamiento de datos en general.

Clasificación antigua:

- G06F15/00 G06F […] › Computadores digitales en general (detalles G06F 1/00 - G06F 13/00 ); Equipo de procesamiento de datos en general.

Países PCT: Austria, Bélgica, Suiza, Alemania, Dinamarca, España, Francia, Reino Unido, Grecia, Italia, Liechtensein, Luxemburgo, Países Bajos, Suecia, Mónaco, Portugal, Irlanda, Eslovenia, Finlandia, Rumania, Chipre, Lituania, Letonia, Ex República Yugoslava de Macedonia, Albania.

Fragmento de la descripción:

Sistema y método para la reconfiguración en el tiempo de funcionamiento.

La presente invención se refiere a un sistema y un método para la reconfiguración en el tiempo de funcionamiento de los sistemas de procesamiento digital de señales (DSP).

El concepto básico de un procesamiento re-configurable existe desde hace bastante tiempo. Por ejemplo, incluso los procesadores de propósito general usan algunas de las ideas básicas, tales como la reutilización de componentes de cálculo para cálculos independientes y el uso de multiplexores para controlar el encaminamiento entre estos componentes. Sin embargo, el término "procesamiento re-configurable" como se usa en las investigaciones actuales se refiere a sistemas que incorporan alguna forma de posibilidad de programación del hardware, adaptando la forma de utilización del hardware utilizando varios puntos de control físicos. Estos puntos de control pueden cambiarse a continuación periódicamente para ejecutar diferentes aplicaciones usando el mismo hardware.

El uso de arquitecturas re-configurables está obteniendo un papel importante en plataformas de diseño de un sistema sobre un chip. Aplicando una arquitectura re-configurable para implementar no sólo los intensos cálculos de flujos de datos sino que también la computación orientada al control o la computación basada en el flujo de datos (por ejemplo, el encaminamiento, arrastre e intercalado de los datos) es un enfoque que promete. Sin embargo, la mayor parte del trabajo hasta la fecha se ha centrado en el software de las estaciones base de radio, que no tienen las restricciones de tamaño y potencia de los terminales móviles. Hay aún una necesidad de desarrollar sistemas en los que puedan soportarse las tecnologías de Software de Radio Definido (SDR) sobre un terminal móvil.

La reconfiguración en el tiempo de funcionamiento puede definirse como una reconfiguración en línea de un sistema de procesamiento de señales en tiempo real sin la necesidad de desactivar el sistema durante el proceso de reconfiguración. Para conseguir esto, se requiere un grado de flexibilidad en la arquitectura para permitir que partes del sistema se reconfiguren mientras que otras partes continúan funcionando.

Los sistemas de la técnica anterior que usan la reconfiguración en el tiempo de funcionamiento consisten básicamente en dos bloques de procesamiento 11, 12 que realizan las operaciones de procesamiento de señal (véase la figura 3). Estos bloques de procesamiento 11, 12 pueden ser bloques de grano fino (a nivel de bit), bloques de grano grueso o una cadena de bloques que realizan algoritmos sucesivos como en la capa física de un sistema de comunicaciones. Tales sistemas también tienen un controlador de configuración 14 que selecciona la configuración requerida almacenada en una memoria de configuración 15 y también controla multiplexores o conmutadores 9, 10 que determinan qué bloque de procesamiento procesa la señal y que bloque de procesamiento se configura cargando una nueva configuración dentro de la memoria del bloque de procesamiento 13.

En tales sistemas de la técnica anterior, sólo uno de los bloques de procesamiento está activo durante las operaciones normales, mientras que el otro bloque de procesamiento se configura con la nueva configuración que representa un actualización/mejora del software o un modo de funcionamiento diferente, por ejemplo, para adaptarse a otro sistema de comunicaciones normalizado.

Esta redundancia en los bloques de procesamiento durante el normal funcionamiento no es el uso más eficaz de los recursos. Por ejemplo, la tasa de procesamiento es mayor que la necesaria y por lo tanto el consumo de energía es mayor que el necesario. Por consiguiente, hay una necesidad de un sistema de reconfiguración en el tiempo de funcionamiento con una cantidad mínima de redundancia en el sistema y un consumo reducido de potencia.

El documento US4918637A describe un filtro multi-canal de decimación/interpolación.

De acuerdo con la presente invención se proporciona un sistema de procesamiento digital de señales re-configurable que comprende:

un convertidor de serie a paralelo que comprende al menos un bloque de retardo y al menos un bloque de decimación dispuesto para convertir una primera señal serie con una primera tasa de muestreo a una multiplicidad de señales de subbandas en paralelo con una segunda tasa de muestreo, en el que la segunda tasa de muestreo es menor o igual que la primera tasa de muestreo;

unos bloques de procesamiento dispuestos para procesar las señales de las subbandas para producir señales procesadas;

un controlador de configuración dispuesto para modificar el factor de decimación de cada bloque de decimación y parar cargar una configuración en la memoria del bloque de procesamiento;

un convertidor de paralelo a serie que comprende al menos un bloque de expansión, dispuesto el convertidor de paralelo a serie para recuperar a partir de las señales procesadas una segunda señal serie con una tasa de muestreo sustancialmente igual a la primera tasa de muestreo;

en el que, en la operación en el tiempo de funcionamiento el factor de decimación de cada uno de los bloques de decimación es igual al número de señales de subbandas y cuando se requiere la re-configuración durante el tiempo de funcionamiento el controlador de configuración se dispone para disminuir el factor de decimación de modo que la segunda tasa de muestreo aumenta; carga la configuración en la memoria del bloque de procesamiento; y disminuye el factor de decimación de nuevo para que sea igual al número de señales de subbandas.

De acuerdo con la presente invención también se proporciona un método de procesar una señal digital en un sistema de procesamiento digital re-configurable, comprendiendo el método las etapas de:

convertir de serie a paralelo una primera señal serie con una primera tasa de muestreo a una multiplicidad de señales de subbandas en paralelo con una segunda tasa de muestreo, por medio de un convertidor de serie a paralelo que comprende al menos un bloque de retardo y al menos un bloque de decimación, en el que la segunda tasa de muestreo es menor o igual que la primera tasa de muestreo;

procesar las señales de subbandas para producir las señales procesadas, por medio de bloques de procesamiento;

convertir de paralelo a serie las señales procesadas para recuperar una segunda señal serie con una tasa de muestreo sustancialmente igual que la primera tasa de muestreo a partir de las señales procesadas;

en el que, en la operación normal en el tiempo de funcionamiento el factor de decimación de cada bloque de decimación es igual que el número de señales de subbandas y cuando se requiere la reconfiguración durante el tiempo de funcionamiento el método comprende además las etapas de:

disminuir el factor de decimación del bloque de decimación de modo que aumenta la segunda tasa de muestreo, por medio de un controlador de configuración;

cargar una configuración en la memoria del bloque de procesamiento por medio del controlador de configuración;

aumentar de nuevo el factor de decimación para que sea igual al número de señales de subbandas, por medio del controlador de configuración.

Ahora se describirán ejemplos de la presente invención con referencia a los dibujos adjuntos, en los que:

la Figura 1 muestra un sistema re-configurable de acuerdo con un ejemplo de la presente invención;

la Figura 2 es un diagrama de un ejemplo de decimador de orden M y un ejemplo de expansor de orden M para M = 3, los principios de los cuales se usan en la presente invención;

la Figura 3 muestra un sistema general re-configurable de la técnica anterior;

la Figura 4 muestra un transmisor de OFDM re-configurable de acuerdo con un ejemplo de la presente invención;

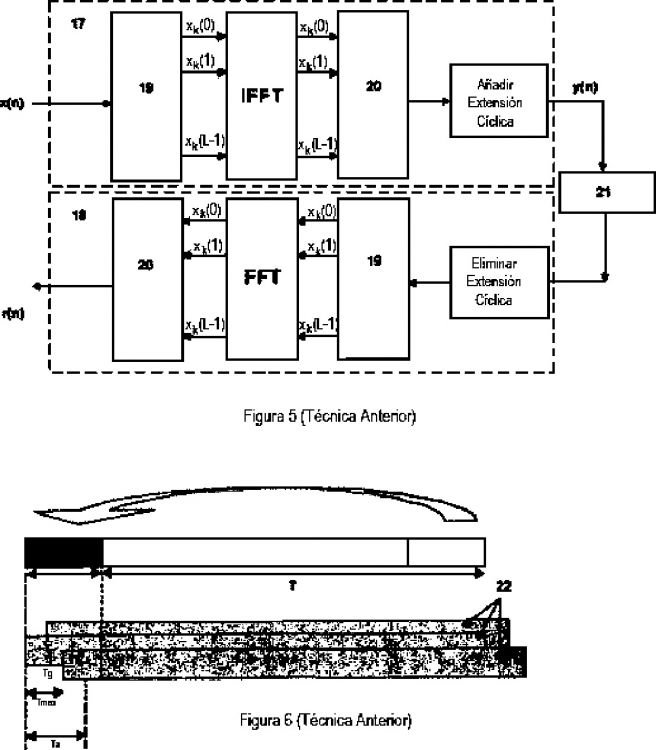

la Figura 5 muestra un transceptor básico de OFDM de una técnica anterior; y

la Figura 6 es un diagrama que ilustra el concepto de un prefijo cíclico en un transceptor de OFDM.

La Figura 1 muestra un ejemplo de la presente invención, que es un sistema de subbandas re-configurable que combina un sistema de procesamiento multi-tasa con un controlador de configuración 1, un conmutador 7 y una memoria de configuración 8. El sistema de procesamiento multi-tasa comprende un convertidor de serie a paralelo, un bloque de procesamiento PB y un convertidor de paralelo a serie 6. El sistema...

Reivindicaciones:

1. Un sistema de procesamiento digital de señales re-configurable, que comprende:

un convertidor de serie a paralelo (4) que comprende al menos un bloque de retardo (5) y al menos un bloque de decimación (2) dispuesto para convertir una primera señal serie (x(n)) con una primera tasa de muestreo en una multiplicidad (L) de señales de subbandas en paralelo con una segunda tasa de muestreo, en el que la segunda tasa de muestreo es menor o igual que la primera tasa de muestreo;

bloques de procesamiento (PB0, PB1, PBL-1) dispuestos para procesar las señales de las subbandas para producir señales procesadas;

un controlador de configuración (1) dispuesto para modificar el factor de decimación (M) de cada uno de los bloques de decimación y para cargar una configuración dentro de la memoria (MEM) de un bloque de procesamien-to;

un convertidor de serie a paralelo (6) que comprende al menos un bloque de expansión (3), dispuesto el convertidor de paralelo a serie para recuperar a partir de las señales procesadas una segunda señal serie (y(n)) con una tasa de muestreo sustancialmente igual a la primera tasa de muestreo;

en el que en la operación normal del tiempo de funcionamiento el factor de decimación (M) de cada uno de los bloques de decimación (2) es igual al número (L) de señales de subbandas y cuando se requiere la reconfiguración en el tiempo de funcionamiento el controlador de configuración se dispone a disminuir el factor de decimación de modo que aumenta la segunda tasa de muestreo; cargar la configuración dentro de la memoria de un bloque de procesamiento; y aumentar el factor de decimación de nuevo para que sea igual que el número de señales de subbandas.

2. Un sistema de procesamiento digital de señales que se puede reconfigurar de acuerdo con la reivindicación 1, en el que el controlador de configuración (1) está dispuesto para realizar disminuciones sucesivas en el factor de decimación (M) para cargar de forma incremental una configuración.

3. Un sistema de procesamiento digital de señales que se puede reconfigurar de acuerdo con la reivindicación 1 ó la reivindicación 2, que comprende además:

un medio de transformada (R(z)) dispuesto para transformar las señales de subbandas antes de que las señales de subbandas se procesen por los bloques de procesamiento (PB0, PB1, PBL-1); y

un medio de transformada inversa (E(z)) dispuesto para transformar inversamente las señales procesadas antes de que las señales procesadas se conviertan de paralelo a serie por el convertidor de paralelo a serie (6).

4. Un sistema de procesamiento digital de señales que se puede reconfigurar de acuerdo con la reivindicación 3, en el que el medio de transformada (R(z)) es un medio de transformada rápida de Fourier y el medio de transformada inversa (E(z)) es un medio de la transformada inversa rápida de Fourier.

5. Un método de procesamiento de una señal digital en un sistema de procesamiento digital que se puede reconfigurar, comprendiendo el método las etapas de:

convertir de serie a paralelo una primera señal serie (x(n)) con una primera tasa de muestreo a una multiplicidad (L) de señales de subbandas en paralelo con una segunda tasa de muestreo, por medio de un convertidor de serie a paralelo (4) comprendiendo al menos un bloque de retardo (5) y al menos un bloque de decimación (2), en el que la segunda tasa de muestreo es menor o igual que la primera tasa de muestreo;

procesar las señales de subbandas para producir señales procesadas, por medio de bloques de procesamiento (PB0, PB1, PBL-1);

convertir de paralelo a serie las señales procesadas para recuperar una segunda señal serie (y(n)) con una tasa de muestreo sustancialmente igual que la primera tasa de muestreo de las señales procesadas;

en el que en la operación normal en el tiempo de funcionamiento el factor de decimación (M) de cada bloque de decimación es igual que el número (L) de señales de subbandas y cuando se requiere la reconfiguración durante el tiempo de muestreo el método comprende además las etapas de:

disminuir el factor de decimación del bloque de decimación de modo que la segunda tasa de muestreo aumenta, por medio de un controlador de configuración (1);

cargar una configuración dentro de la memoria (MEM) de un bloque de procesamiento por medio de un controlador de configuración;

aumentar el factor de decimación para que de nuevo sea igual al número de las señales de subbandas, por medio del controlador de configuración.

6. Un método de procesamiento digital de señales en un sistema de procesamiento digital que se puede reconfigurar de acuerdo con la reivindicación 5, en el que el controlador de reconfiguración (1) realiza sucesivas etapas de disminución del factor de decimación y carga una configuración de forma incremental.

7. Un método de procesamiento digital de señales en un sistema de procesamiento digital que se puede reconfigurar de acuerdo con la reivindicación 5 ó la reivindicación 6, que comprende además las etapas de:

transformar (R(z)) las señales de las subbandas antes de la etapa de procesamiento; y

transformar de forma inversa (E(z)) las señales procesadas antes de la etapa de conversión de paralelo a serie.

8. Un método de procesamiento digital de señales en un sistema de procesamiento digital de señales de acuerdo con la reivindicación 7, en el que la etapa de transformar (R(z)) es una etapa de transformada rápida de Fourier y la etapa de transformar de forma inversa (E(z)) es una etapa de transformada rápida inversa de Fourier.

Patentes similares o relacionadas:

APARATO PARA EVALUAR LA ENERGÍA DE UNA SEÑAL QUE TIENE SEÑALES DE SUBBANDA Y MÉTODO CORRESPONDIENTE, del 9 de Marzo de 2011, de DOLBY INTERNATIONAL AB: Aparato para evaluar la energía de una señal que tiene señales de subbanda generadas filtrando la señal utilizando un banco de filtros de análisis, teniendo el banco de filtros, […]

APARATO PARA CALCULAR VALORES DE AJUSTE DE GANANCIA PARA AJUSTAR LA GANANCIA DE UNA PLURALIDAD DE SEÑALES DE SUBBANDA EN BANCOS DE FILTROS DE VALOR REAL Y MÉTODO CORRESPONDIENTE, del 26 de Enero de 2011, de DOLBY INTERNATIONAL AB: Aparato para calcular valores de ajuste de ganancia para ajustar la ganancia de una pluralidad de señales de subbanda generadas filtrando una […]

APARATO PARA CALCULAR VALORES DE AJUSTE DE GANANCIA PARA AJUSTAR LA GANANCIA DE UNA PLURALIDAD DE SEÑALES DE SUBBANDA EN BANCOS DE FILTROS DE VALOR REAL Y MÉTODO CORRESPONDIENTE, del 26 de Enero de 2011, de DOLBY INTERNATIONAL AB: Aparato para calcular valores de ajuste de ganancia para ajustar la ganancia de una pluralidad de señales de subbanda generadas filtrando una […]

APARATO Y METODO PARA GENERAR VALORES DE SUBBANDA DE AUDIO Y APARATO YMETODO PARA GENERAR MUESTRAS DE AUDIO DE DOMINIO DE TIEMPO, del 10 de Noviembre de 2009, de FRAUNHOFER-GESELLSCHAFT ZUR FORDERUNG DER ANGEWANDTEN FORSCHUNG E.V.: Aparato para generar valores de subbanda de audio en canales de subbanda de audio, que comprende: un divisor en ventanas de análisis para dividir en ventanas una trama […]

APARATO Y METODO PARA GENERAR VALORES DE SUBBANDA DE AUDIO Y APARATO YMETODO PARA GENERAR MUESTRAS DE AUDIO DE DOMINIO DE TIEMPO, del 10 de Noviembre de 2009, de FRAUNHOFER-GESELLSCHAFT ZUR FORDERUNG DER ANGEWANDTEN FORSCHUNG E.V.: Aparato para generar valores de subbanda de audio en canales de subbanda de audio, que comprende: un divisor en ventanas de análisis para dividir en ventanas una trama […]

Servicios sensibles al contexto, del 24 de Junio de 2020, de Nokia Technologies OY: Un método que comprende: recibir, en un dispositivo inalámbrico , señales de sensor que caracterizan una o más condiciones ambientales, […]

Generación de una separación de tinta blanca, del 19 de Febrero de 2020, de ELECTRONICS FOR IMAGING, INC: Procedimiento de impresión con un dispositivo capaz de imprimir tinta blanca, para crear una imagen, como un color de impresión que comprende: calcular un factor […]

Sistema de descodificación para descodificar archivos multimedia, sistema para codificar un archivo multimedia, y archivo multimedia, del 22 de Enero de 2020, de DIVX, LLC: Un sistema de descodificación para descodificar archivos multimedia (30, 30'), comprendiendo el sistema de descodificación: un procesador configurado y al […]

Controlador de sitio con funcionalidad de correlación, del 26 de Junio de 2019, de SIPCO LLC: Un controlador de sitio para su uso en una red de comunicación inalámbrica adaptado para su uso en un sistema de supervisión automático […]

Controlador de sitio con funcionalidad de correlación, del 26 de Junio de 2019, de SIPCO LLC: Un controlador de sitio para su uso en una red de comunicación inalámbrica adaptado para su uso en un sistema de supervisión automático […]

Método y programa de autenticación de usuario, y aparato de formación de imágenes, del 15 de Mayo de 2019, de RICOH COMPANY, LTD.: Un método de autenticación de usuario para un aparato de formación de imágenes que se puede conectar a través de una red a un aparato de […]