PROCESAMIENTO DE AUDIO PARA EQUIPO AUDIOVISUAL.

SE SUMINISTRA UN APARATO DE DECODIFICACION DE AUDIO PARA RECIBIR UNA CORRIENTE DE BITS EN BASE BLOQUE A BLOQUE,

DECODIFICANDO UN BLOQUE DE LA CORRIENTE DE BITS PARA FORMAR DATOS DE AUDIO DECODIFICADOS PARA UNA PLURALIDAD DE CANALES, Y ALMACENANDO LOS DATOS DE AUDIO DECODIFICADOS PARA CADA UNO DE LA PLURALIDAD DE CANALES EN EL DISPOSITIVO DE MEMORIA, MEZCLANDO DE DICHA FORMA EN SU SALIDA LOS DATOS DE AUDIO DECODIFICADOS PARA CADA UNO DE LA PLURALIDAD DE CANALES. EL APARATO DE DECODIFICACION DE AUDIO INCLUYE UNA SECCION DE OPERACION PARA MEZCLAR A LA SALIDA LOS DATOS DE AUDIO DECODIFICADOS PARA CADA UNO DE LA PLURALIDAD DE CANALES CORRESPONDIENTES AL PRIMER BLOQUE DE LA CORRIENTE DE BITS EN LA SECCION DE MEMORIA MIENTRAS QUE SE DECODIFICA UN SEGUNDO BLOQUE DE LA CORRIENTE DE BITS

Tipo: Patente Europea. Resumen de patente/invención. Número de Solicitud: E98106710.

Solicitante: MATSUSHITA ELECTRIC INDUSTRIAL CO., LTD..

Nacionalidad solicitante: Japón.

Dirección: 1006, OAZA-KADOMA,KADOMA-SHI, OSAKA 571-8501.

Inventor/es: MIYASAKA, SHUJI, KATAYAMA, TAKASHI, FUJITA, TAKESHI, MATSUMOTO, MASAHARU, ISHITO,TSUKURU, SUEYOSHI,MASAHIRO, ABE,KAZUTAKA, NAKAMURA,TSUYOSHI, OTOMURA,EIJI, KAWAMURA,AKIHISA.

Fecha de Publicación: .

Fecha Solicitud PCT: 14 de Abril de 1998.

Fecha Concesión Europea: 10 de Marzo de 2010.

Clasificación Internacional de Patentes:

- G10L21/04 FISICA. › G10 INSTRUMENTOS MUSICALES; ACUSTICA. › G10L ANALISIS O SINTESIS DE LA VOZ; RECONOCIMIENTO DE LA VOZ; PROCESAMIENTO DE LA VOZ O EL HABLA; CODIFICACIÓN O DESCODIFICACIÓN DEL AUDIO O LA VOZ. › G10L 21/00 Tratamiento de la señal de la voz para producir otra señal audible o no audible, p. ej. visual o táctil, con el fin de modificar su calidad o su inteligibilidad (G10L 19/00 tiene prioridad). › Compresión o expansión temporales.

- H04B1/66M

- H04N5/60N

- H04N7/52A

Clasificación PCT:

- H03M7/00 ELECTRICIDAD. › H03 CIRCUITOS ELECTRONICOS BASICOS. › H03M CODIFICACION, DECODIFICACION O CONVERSION DE CODIGO, EN GENERAL (por medio de fluidos F15C 4/00; convertidores ópticos analógico/digitales G02F 7/00; codificación, decodificación o conversión de código especialmente adaptada a aplicaciones particulares, ver las subclases apropiadas, p. ej. G01D, G01R, G06F, G06T, G09G, G10L, G11B, G11C, H04B, H04L, H04M, H04N; cifrado o descifrado para la criptografía o para otros fines que implican la necesidad de secreto G09C). › Conversión de un código, en el cual la información está representada por una secuencia dada o por un número de dígitos, en un código en el cual la misma información está representada por una secuencia o por un número de dígitos diferentes.

- H04B14/04 H […] › H04 TECNICA DE LAS COMUNICACIONES ELECTRICAS. › H04B TRANSMISION. › H04B 14/00 Sistemas de transmisión no caracterizados por el medio utilizado para la transmisión (sus detalles H04B 1/00). › que utilizan la modulación por impulsos codificados.

- H04N7/52 H04 […] › H04N TRANSMISION DE IMAGENES, p. ej. TELEVISION. › H04N 7/00 Sistemas de televisión (detalles H04N 3/00, H04N 5/00; métodos y arreglos, para la codificación, decodificación, compresión o descompresión de señales de vídeo digital H04N 19/00; distribución selectiva de contenido H04N 21/00). › Sistema para la transmisión de un impulso codificado modulado con otras señales moduladas por impulsos codificados, p. ej. una señal de audio o una señal de sincronización mediante la combinación de un flujo de video con otros datos de contenido o adicionales (multiplexado de flujos multiplexados, inserción de bits de relleno en un flujo multiplexado, para obtener una tasa de bits constante, ensamblado de flujo elemental en paquetes en el lado del servidor H04N 21/236; Desensamblado de un flujo multiplexado, multiplexación de flujo multiplexado, extracción o procesado de Servicos de Información, desensamblado de un flujo elemental en paquetes H04N 21/434).

Clasificación antigua:

- H03M7/00 H03M […] › Conversión de un código, en el cual la información está representada por una secuencia dada o por un número de dígitos, en un código en el cual la misma información está representada por una secuencia o por un número de dígitos diferentes.

- H04B14/04 H04B 14/00 […] › que utilizan la modulación por impulsos codificados.

- H04N7/52 H04N 7/00 […] › Sistema para la transmisión de un impulso codificado modulado con otras señales moduladas por impulsos codificados, p. ej. una señal de audio o una señal de sincronización mediante la combinación de un flujo de video con otros datos de contenido o adicionales (multiplexado de flujos multiplexados, inserción de bits de relleno en un flujo multiplexado, para obtener una tasa de bits constante, ensamblado de flujo elemental en paquetes en el lado del servidor H04N 21/236; Desensamblado de un flujo multiplexado, multiplexación de flujo multiplexado, extracción o procesado de Servicos de Información, desensamblado de un flujo elemental en paquetes H04N 21/434).

Países PCT: Austria, Bélgica, Suiza, Alemania, Dinamarca, España, Francia, Reino Unido, Grecia, Italia, Liechtensein, Luxemburgo, Irlanda, Finlandia, Chipre.

Fragmento de la descripción:

Procesamiento de audio para equipo audiovisual.

1. Campo de la invención

La presente invención se refiere a un aparato de decodificación de audio usado en equipos AV (audiovisuales) para decodificar en datos PCM un flujo continuo de bits codificados. La presente invención se refiere también a un dispositivo de procesamiento de señales, un dispositivo de localización de imágenes sonoras, un método de control de imágenes sonoras, un dispositivo de procesamiento de señales de audio, y un método de reproducción de alta velocidad de señales de audio usados también en equipos AV.

2. Descripción de la técnica relacionada

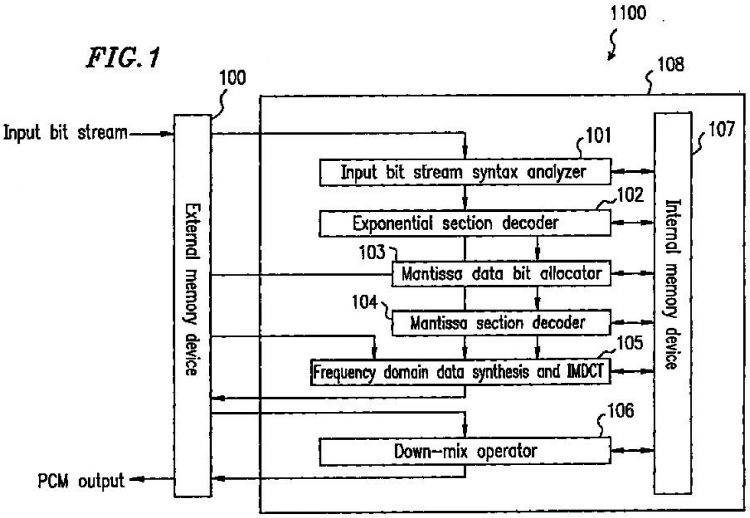

Se describirá un aparato convencional 550 de decodificación de audio haciendo referencia a las Figuras 6, 7 y 8. La Figura 6 es un diagrama de bloques que ilustra una estructura del aparato convencional 550 de decodificación de audio. El aparato 550 de decodificación de audio incluye un dispositivo semiconductor integrado 508. El dispositivo semiconductor integrado 508 incluye un analizador 501 de sintaxis de flujos continuos de bits de entrada, un decodificador 502 de secciones exponenciales, un asignador 503 de bits de datos de mantisa, un decodificador 504 de secciones de mantisa, un IMDCT 505, un operador 506 de mezcla descendente, y un dispositivo 507 de memoria interna. El dispositivo semiconductor integrado 508 intercambia datos con un dispositivo 500 de memoria externa.

En primer lugar un flujo continuo de bits se almacena en el dispositivo 500 de memoria externa y a continuación se introduce en el analizador 501 de sintaxis de flujos continuos de bits de entrada. El analizador 501 de sintaxis de flujos continuos de bits de entrada analiza la sintaxis del flujo continuo de bits y extrae datos requeridos para su decodificación. Dichos datos se envían al decodificador 502 de secciones exponenciales. El decodificador 502 de secciones exponenciales forma datos exponenciales para un dominio de frecuencia a partir de los datos requeridos para la decodificación, y da salida a los datos exponenciales hacia el asignador 503 de bits de datos de mantisa y el IMDCT 505. El asignador 503 de bits de datos de mantisa calcula una magnitud de asignación de bits de datos de mantisa a partir de los datos exponenciales para el dominio de frecuencia y los datos almacenados en el dispositivo 500 de memoria externa, y da salida a la magnitud de asignación de bits de datos de mantisa hacia el decodificador 504 de secciones de mantisa. El decodificador 504 de secciones de mantisa forma datos de mantisa para el dominio de la frecuencia a partir de la magnitud de asignación de bits de datos de mantisa y da salida a los datos de mantisa hacia el IMDCT (dispositivo de transformada de coseno discreta, modificada e inversa) 505. El IMDCT 505 forma datos de audio decodificados en un dominio del tiempo a partir de los datos exponenciales y los datos de mantisa para el dominio de la frecuencia, y almacena los datos de audio decodificados en el dispositivo 500 de memoria externa. El operador 506 de mezcla descendente forma datos PCM a partir de los datos de audio decodificados almacenados en el dispositivo 500 de memoria externa, realiza un entrelazado y a continuación almacena los datos resultantes en el dispositivo 500 de memoria externa. A continuación, a los datos PCM se les da salida desde el dispositivo 500 de memoria externa.

La Figura 7 es un mapa de memoria del aparato 550 de decodificación de audio mostrado en la Figura 6. El mapa de memoria mostrado en la Figura 7 incluye un área 600 para almacenar datos PCM de un bloque, un área 601 para almacenar datos de audio decodificados de un bloque para el canal 0, un área 602 para almacenar datos de audio decodificados de un bloque para el canal 1, un área 603 para almacenar datos de audio decodificados de un bloque para el canal 2, un área 604 para almacenar datos de audio decodificados de un bloque para el canal 3, un área 605 para almacenar datos de audio decodificados de un bloque para el canal 4, y un área 606 para almacenar datos de audio decodificados de un bloque para el canal 5.

La Figura 8 es un diagrama de flujo que ilustra un método para decodificar datos de audio codificados de un bloque para cada canal.

En la etapa S11, se inicializan un registro (no mostrado), el dispositivo 507 de memoria interna (Figura 6), y un dispositivo 500 de memoria externa. En la etapa S12, el flujo continuo de bits almacenado en el dispositivo 500 de memoria externa se introduce en el dispositivo semiconductor integrado 508 (recepción de datos codificados).

A continuación, en la etapa S13, se analiza la sintaxis del flujo continuo de bits, y se extraen datos requeridos para la decodificación (análisis de flujos continuos de bits). En la etapa S14, se forman datos exponenciales para un dominio de frecuencia usando los datos extraídos. En la etapa S15, se calcula una magnitud de asignación de bits de datos de mantisa usando los datos exponenciales para el dominio de frecuencia. En la etapa S16, se forman datos de mantisa para el dominio de frecuencia usando la magnitud de asignación de bits de datos de mantisa. En la etapa S17, se forman datos de audio decodificados usando los datos de mantisa para el dominio de frecuencia y los datos exponenciales para el dominio de frecuencia. En la etapa S18, los datos de audio decodificados resultantes se almacenan en el dispositivo 500 de memoria externa.

Las etapas descritas anteriormente se realizan para el número de canal incluido en un bloque hasta que, en la etapa S19, se confirma que las etapas se repiten las veces requeridas. Como consecuencia, se forma el número de segmentos de datos de audio decodificados correspondiente al número de canales incluidos en un bloque, y el mismo se almacena en el dispositivo 500 de memoria externa.

En la etapa S20, datos de audio decodificados de un bloque para cada canal en el dispositivo 500 de memoria externa se introducen en el dispositivo semiconductor integrado 508. En la etapa S21, los datos de audio decodificados de un bloque para cada canal se convierten en datos PCM de un bloque (cálculo de mezcla descendente). En la etapa S22, a los datos PCM de un bloque se les da salida hacia el dispositivo 500 de memoria externa.

En el decodificador convencional 600 de audio, se calculan datos PCM de un bloque en un cálculo de mezcla descendente. Por consiguiente, la cantidad de datos transferidos para introducir los datos de audio decodificados en el dispositivo 500 de memoria externa antes del cálculo de mezcla descendente y para escribir los datos PCM en el dispositivo 500 de memoria externa después del cálculo de mezcla descendente es suficientemente grande como para ocupar una parte significativa del bus de memoria. Dicha ocupación tiene un efecto negativo sobre otros procesamientos realizados por el dispositivo 500 de memoria externa.

Se describirá un dispositivo convencional de procesamiento de señales. Una parte de los datos codificados de una pluralidad de canales puede ser compartida en común por los canales. Por ejemplo, datos codificados de la banda de alta frecuencia que estén incluidos en por lo menos uno de la pluralidad de canales y compartidos por la pluralidad de canales se decodifican para formar datos decodificados de la banda de alta frecuencia. Datos codificados de la banda de baja frecuencia para cada canal se decodifican para formar datos decodificados de la banda de baja frecuencia. Los datos decodificados de la banda de baja frecuencia se acoplan a los datos decodificados de la banda de alta frecuencia para formar datos decodificados para cada canal.

Dicha decodificación se describirá haciendo referencia a las Figuras 19, 20 y 21.

La Figura 20 es un diagrama de bloques de un procesador convencional 1350 de señales para realizar la decodificación de señales antes descrita. Tal como se muestra en la Figura 20, el flujo continuo de bits se almacena temporalmente en un dispositivo 1301 de memoria interna, y es analizado por un analizador 1300 de sintaxis de flujos continuos de bits. De este modo, se extraen datos requeridos. Se forman datos exponenciales para un dominio de frecuencia por medio de un decodificador 1302 de secciones exponenciales basándose en los datos extraídos. Por medio de un asignador 1303 de bits de datos de mantisa, basándose en los datos exponenciales para el dominio de frecuencia, se determina una magnitud de asignación de bits de datos de mantisa. Por medio de un decodificador 1304 de secciones de mantisa, basándose en la magnitud de asignación de bits de datos de mantisa, se forman datos de mantisa. Por medio de un dispositivo 1305 de formación de datos...

Reivindicaciones:

1. Procesador (3800) de señales de audio, que comprende:

una sección (3006) de control para indicar una velocidad de reproducción;

un procesador (3002) de señales de entrada para procesar una señal (3001) de entrada obtenida como resultado de multiplexar una señal de audio y una señal de vídeo y dar salida a una señal de audio y una señal de vídeo;

una memoria intermedia (3003) de flujos continuos de audio para almacenar temporalmente la señal de audio obtenida a la salida del procesador (3002) de señales de entrada;

una memoria intermedia (3004) de flujos continuos de vídeo para almacenar temporalmente la señal de vídeo obtenida a la salida del procesador (3002) de señales de entrada;

un procesador (3007) de audio para extraer la señal de audio de la memoria intermedia (3003) de flujos continuos de audio y procesar la señal de audio para formar una señal (3009) de audio de salida; y

un procesador (3008) de vídeo para extraer la señal de vídeo de la memoria intermedia (3004) de flujos continuos de vídeo y procesar la señal de vídeo, y realizar una reproducción de alta velocidad de la señal de vídeo en respuesta a una instrucción de la sección (3006) de control para formar una señal (3010) de vídeo de salida,

caracterizado porque comprende además:

un controlador (3005B) de memorias intermedias para supervisar un estado de la memoria intermedia (3004) de flujos continuos de vídeo y, durante la reproducción de alta velocidad, cuando una cantidad de datos restante en la memoria intermedia (3004) de flujos continuos de vídeo se hace menor que un primer nivel preestablecido (V), informar al procesador de audio sobre la cantidad de datos restante en la memoria intermedia de flujos continuos de vídeo de manera que el procesador (3007) de audio realiza una reproducción de alta velocidad de la señal de audio descartando una cantidad preestablecida de la señal de audio y retomando el procesamiento de la señal de audio para formar una señal de audio de salida en una reproducción de velocidad normal.

2. Procesamiento de señales de audio según la reivindicación 1, en el que el controlador (3005C) de memorias intermedias está destinado además a supervisar un estado de la memoria intermedia (3003) de flujos continuos de audio y, cuando una capacidad libre restante de la memoria intermedia de flujos continuos de audio se hace menor que un segundo valor preestablecido (W), informar al procesador de audio sobre la capacidad libre restante de la memoria intermedia de flujos continuos de audio de manera que el procesador de audio realiza la reproducción de alta velocidad de la señal de audio descartando la cantidad preestablecida de la señal de audio y retomando el procesamiento de la señal de audio para formar la señal de audio de salida en la reproducción de velocidad normal.

3. Método de realización de una reproducción de alta velocidad de una señal de audio en el procesador de señales de audio según la reivindicación 1 ó 2, caracterizado porque comprende una etapa que consiste en rebajar la señal de audio evacuando intermitentemente un contenido de la memoria intermedia de flujos continuos de audio para reducir una cantidad de datos de audio que se debe reproducir mientras se realiza la reproducción de alta velocidad de la señal de vídeo.

4. Método de realización de una reproducción de alta velocidad de una señal de audio en el procesador de señales de audio según la reivindicación 1 ó 2, caracterizado porque comprende una etapa que consiste en interrumpir, durante un periodo de tiempo preestablecido, la transferencia de la señal de audio desde el procesador de señales de entrada hacia la memoria intermedia de flujos continuos de audio para reducir una cantidad de datos de audio que se debe reproducir mientras se realiza la reproducción de alta velocidad de la señal de vídeo.

5. Método de realización de una reproducción de alta velocidad de una señal de audio en el procesador de señales de audio según la reivindicación 1 ó 2, caracterizado porque comprende una etapa que consiste en omitir una cantidad preestablecida de datos introducidos desde la memoria intermedia de flujos continuos de audio hacia el procesador de audio para reducir una cantidad de datos de audio que se debe reproducir mientras se realiza la reproducción de alta velocidad de la señal de vídeo.

6. Método de realización de una reproducción de alta velocidad de una señal de audio en el procesador de señales de audio según la reivindicación 1 ó 2, caracterizado porque comprende una etapa que consiste en interrumpir, durante un periodo de tiempo preestablecido, una salida de la señal de audio desde el procesador de audio para reducir una cantidad de datos de audio que se debe reproducir mientras se realiza la reproducción de alta velocidad de la señal de vídeo.

Patentes similares o relacionadas:

Dispositivo y método para manipular una señal de audio que tiene un evento transitorio, del 24 de Julio de 2019, de FRAUNHOFER-GESELLSCHAFT ZUR FORDERUNG DER ANGEWANDTEN FORSCHUNG E.V.: Aparato para manipular una señal de audio que tiene un evento transitorio que comprende: un procesador de señal para procesar una señal de audio reducida […]

Escalador de tiempo, decodificador de audio, procedimiento y programa informático mediante el uso de un control de calidad, del 29 de Mayo de 2019, de FRAUNHOFER-GESELLSCHAFT ZUR FORDERUNG DER ANGEWANDTEN FORSCHUNG E.V.: Un escalador de tiempo para la provisión de una versión de escala de tiempo de una señal de audio de entrada (210; […]

Dispositivo y método para manipular una señal de audio que tiene un evento transitorio, del 22 de Mayo de 2019, de FRAUNHOFER-GESELLSCHAFT ZUR FORDERUNG DER ANGEWANDTEN FORSCHUNG E.V.: Aparato para manipular una señal de audio que comprende un evento transitorio que comprende: un procesador de señal para procesar una señal de […]

Transposición armónica basada en bloque de sub bandas mejorada, del 22 de Mayo de 2019, de DOLBY INTERNATIONAL AB: Un sistema configurado para generar una señal transpuesta en frecuencia y/o extendida en el tiempo a partir de una señal de entrada de audio, […]

Dispositivo y método para manipular una señal de audio que tiene un evento transitorio, del 1 de Mayo de 2019, de FRAUNHOFER-GESELLSCHAFT ZUR FORDERUNG DER ANGEWANDTEN FORSCHUNG E.V.: Aparato para manipular una señal de audio que comprende un evento transitorio en una primera porción de tiempo de la señal de audio, comprendiendo el […]

Transposición armónica basada en bloque de subbanda mejorado de producto cruzado, del 12 de Febrero de 2019, de DOLBY INTERNATIONAL AB: Un sistema configurado para generar una señal extendida en tiempo y/o transpuesta en frecuencia a partir de una señal de entrada, el sistema que comprende: un banco […]

Escalador de tiempo, decodificador de audio, procedimiento y programa informático mediante el uso de un control de calidad, del 31 de Enero de 2018, de FRAUNHOFER-GESELLSCHAFT ZUR FORDERUNG DER ANGEWANDTEN FORSCHUNG E.V.: Un escalador de tiempo para la provisión de una versión de escala de tiempo de una señal de audio de […]

Transposición armónica mejorada, del 26 de Julio de 2017, de DOLBY INTERNATIONAL AB: Un sistema para transponer una señal de audio de entrada según un factor de transposición T, comprendiendo el sistema: - medios para extraer una trama […]