PROCEDIMIENTO Y DISPOSITIVO DE RECEPCION DE UNA SEÑAL DE DATOS COMPUESTA POR BLOQUES DE SIMBOLOS Y PROGRAMA DE ORDENADOR CORRESPONDIENTE.

Procedimiento de recepción de una señal de datos recibida (r) compuesta por al menos un bloque de símbolos recibido y representativo de una señal fuente,

implementando dicho procedimiento una fase de inicialización (I) que comprende una etapa de igualación bloque a bloque (E1) de dicha señal recibida, que suministra para cada bloque de símbolos recibido un bloque de símbolos igualados formados cada uno por un conjunto de bits, comprendiendo el procedimiento al menos una iteración de mejora (II) de una estimación de dicha señal recibida que comprende las etapas siguientes, para un bloque corriente de símbolos igualados:

- obtención (E2) de al menos un bit decodificado, por decodificación bit a bit de un subconjunto corriente de al menos un bit que pertenece a dicho bloque corriente de símbolos igualados;

- actualización (E3) de al menos un símbolo estimado durante dicha fase de inicialización o actualizado durante una iteración de mejora precedente, en función del o de los bits decodificados, que suministra un bloque de símbolos estimados actualizados, constituido por el o los bits decodificados y por al menos un bit decodificado durante al menos una iteración de mejora precedente o durante dicha fase de inicialización;

- determinación (E4) de un bloque mejorado de símbolos igualados por anulación de las interferencias a partir de un igualador de tipo anulador de interferencias cuyos coeficientes se actualizan después de cada bit decodificado, teniendo en cuenta dicho bloque de símbolos estimados actualizados, convirtiéndose dicho bloque mejorado de símbolos igualados en el bloque corriente de símbolos igualados de una posible iteración siguiente

Tipo: Patente Internacional (Tratado de Cooperación de Patentes). Resumen de patente/invención. Número de Solicitud: PCT/FR2007/050904.

Solicitante: FRANCE TELECOM.

Nacionalidad solicitante: Francia.

Dirección: 6 PLACE D'ALLERAY,75015 PARIS.

Inventor/es: HELARD, MARYLINE, BOHER,LAURENT, RABINEAU,RODRIGUE.

Fecha de Publicación: .

Fecha Concesión Europea: 24 de Febrero de 2010.

Clasificación Internacional de Patentes:

- H04L25/03B6

Clasificación PCT:

- H04L25/03 ELECTRICIDAD. › H04 TECNICA DE LAS COMUNICACIONES ELECTRICAS. › H04L TRANSMISION DE INFORMACION DIGITAL, p. ej. COMUNICACION TELEGRAFICA (disposiciones comunes a las comunicaciones telegráficas y telefónicas H04M). › H04L 25/00 Sistemas de banda base. › Redes de formación para emisor o receptor, p. ej. redes de formación adaptables.

Fragmento de la descripción:

Procedimiento y dispositivo de recepción de una señal de datos compuesta por bloques de símbolos y programa de ordenador correspondiente.

1. Campo de la invención

El campo de la invención es el de las comunicaciones digitales. Más en concreto, la invención se refiere, en un sistema de comunicaciones digitales, a una técnica de recepción de una señal de datos recibida compuesta por bloques de símbolos formados cada uno por un conjunto de bits.

La invención se refiere más en particular a una técnica de recepción iterativa que implementa un mecanismo de anulación de interferencias que afecta a uno o varios símbolos de la señal recibida.

Por interferencias, se entiende aquí, y en todo el documento, todo tipo de perturbación (o combinación de perturbaciones) que puede afectar a la señal recibida, como la Interferencia Entre Símbolos ("IES"), la interferencia co-antena, la interferencia debida a una precodificación, etc.

La invención se aplica en particular, pero no exclusivamente, a los sistemas de comunicaciones por vía herciana (transmisión de radio), que presentan una o varias antenas en la emisión y/o en la recepción, como sistemas SIMO ("Single Input Multiple Outputs" en inglés), SISO ("Single Input Single Output" en inglés), MIMO ("Multiple Inputs Multiple Outputs" en inglés), MISO ("Multiple Inputs Single Output" en inglés),..., que implementan una modulación mono o multiportadoras,...

2. Técnica anterior

A continuación se exponen las técnicas de la técnica anterior a través del caso particular de sistemas MIMO-OFDM, es decir, de sistemas de comunicación multiantena que implementan modulaciones de subportadoras ortogonales ("OFDM", "Orthogonal Frequency Division Multiplexing" en inglés).

Los sistemas MIMO-OFDM pueden implementar especialmente técnicas de recepción iterativa, que permiten, en el transcurso de las iteraciones, mejorar la calidad de la estimación de la señal emitida en función de la señal recibida.

Como se verá a continuación, estas técnicas descansan en una implementación sucesiva y repetida de módulos elementales, de manera que estos diferentes módulos se intercambian información sobre la fiabilidad de la operación realizada.

Se conocen técnicas muy numerosas de recepción iterativa para sistemas de antenas múltiples en emisión y/o en recepción.

En el marco de estas técnicas iterativas, se distinguen especialmente:

- los receptores que implementan un algoritmo de tipo Máximo de Verosimilitud (MV, o en inglés "ML" por "Maximum Likelihood"), que presentan el inconveniente de inducir una gran complejidad de tratamiento;

- los receptores a base de filtros lineales, como los que proponen M. Sellathurai y S. Haykin en "Turbo-BLAST for wireless communications: theory and experiments" (en castellano "Turbo-BLAST para comunicaciones inalámbricas: teoría y experiencias"), IEEE Transactions on Signal processing, vol. 50, nº 10, pág. 2538-2546, 2002. Estos receptores se apoyan en técnicas de filtrado de tipo MMSE ("Minimum Mean Square Error", "minimización del error cuadrático medio") y de anulación de interferencias. Presentan la ventaja, con respecto a los receptores de Máximo de Verosimilitud, de ser mucho menos complejos.

Entre los algoritmos implementados en los receptores a base de filtros lineales, algunos, y éste es el caso de la presente invención, descansan en una aproximación que consiste en considerar la estimación de los símbolos perfecta desde la segunda igualación, para el cálculo de los coeficientes del filtro de igualación (también denominado en lo sucesivo bloque de igualación global) que entonces sólo se calculan dos veces para cada bloque.

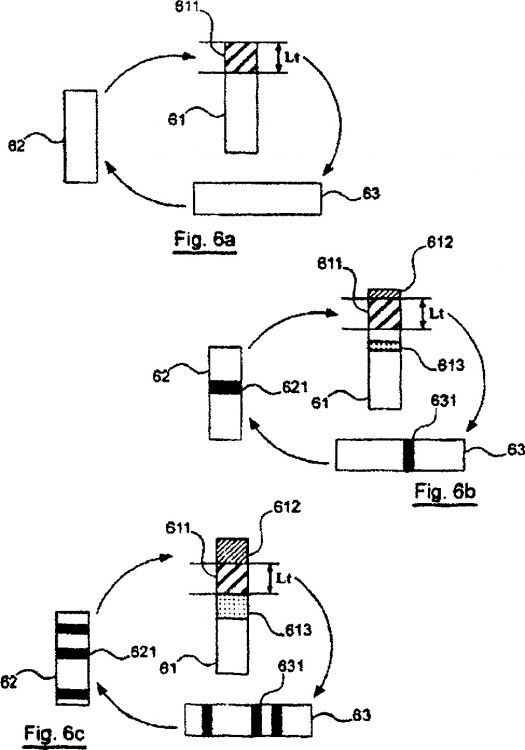

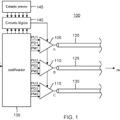

En referencia a la fig. 1 se describe la cadena funcional clásica de un dispositivo 100 de emisión (denominado habitualmente emisor) de una señal fuente 10 compuesta por elementos binarios, en el caso de un contexto de transmisión de tipo MIMO-OFDM.

La señal fuente (binaria) 10 para emisión experimenta una codificación CC 11 de canal, y después un entrelazamiento ? 12. A continuación atraviesa un módulo M 13 de "mapping" (correlación), destinado a convertir elementos binarios en símbolos complejos: un módulo semejante asocia así un grupo de bits a un símbolo complejo que pertenece a una constelación (de tipo QPSK, 16QAM, etc.). La continuación de símbolos suministrada en la salida del módulo M 13 de mapping se denomina actualmente señal M-aria. A continuación se procede a una codificación espacio-tiempo en bloque 14 de cada grupo de Q símbolos, que a continuación se modulan en bloques 151, 152 a 15Nt según una técnica de modulación multiportadora de tipo OFDM, y después se emiten en Nt antenas de emisión 161, 162 a 16Nt.

Como se ilustra en la fig. 2, la cadena funcional clásica de un dispositivo 200 de recepción (habitualmente denominado receptor) de una señal emitida por el dispositivo 100 de emisión citado anteriormente comprende dos etapas, que son un "decodificador de espacio-tiempo" 24 (es decir, un convertidor de símbolos en elementos binarios) y un decodificador 26 de canal, que intercambian informaciones extrínsecas o a posteriori en un bucle iterativo, hasta que el receptor converge. Estas etapas pueden estar separadas especialmente por un entrelazador 221 usado para descorrelacionar las salidas, antes de suministrarlas a la etapa de decodificación siguiente, en otros términos, las informaciones intercambiadas se descorrelacionan de una etapa a la siguiente.

Así, una señal r se recibe en NR antenas de recepción referidas como 251 a 25NR y después se desmodula en bloques 271, 272 a 27NR según una técnica de desmodulación, inversa de la técnica de modulación multiportadora implementada en la emisión. Cada antena 251 a 25NR de recepción recibe una combinación lineal de los símbolos emitidos en cada una de las Nt antenas de emisión. La primera etapa 24 de decodificación comprende un primer bloque 20 de decodificación lineal espacio-tiempo (también denominado en lo sucesivo bloque de igualación global) siguiendo un criterio, por ejemplo, de tipo MMSE o "Zero Forcing" ("ZF", "forzado a cero"). La señal igualada

Al ser el procedimiento iterativo, se hace someter esta señal binaria flexible estimada

Durante la primera iteración, el receptor procede a una igualación clásica de la señal recibida ya que no se dispone de ningún símbolo estimado. Por el contrario, durante las iteraciones siguientes, los símbolos estimados anteriormente son usados por el igualador para anular una o varias interferencias que afectan a la señal recibida.

De forma clásica, los receptores a base de filtros lineales implementan mecanismos de anulación de interferencias que se basan en el uso de bloques de símbolos.

Según esta técnica de recepción iterativa, es necesario que todos los bits que componen los símbolos de un bloque espacio-tiempo se decodifiquen para sustraer las interferencias que afectan a los símbolos que componen la señal recibida.

Más en concreto (en referencia a la fig. 2), el módulo M-1 231 de "demapping", que trabaja símbolo a símbolo, recibe un bloque 201 de símbolos igualados compuesto por Q símbolos igualados (correspondiente a la señal igualada s(p)) y suministra paquetes 202 de nº de bits convertidos.

Reivindicaciones:

1. Procedimiento de recepción de una señal de datos recibida (r) compuesta por al menos un bloque de símbolos recibido y representativo de una señal fuente, implementando dicho procedimiento una fase de inicialización (I) que comprende una etapa de igualación bloque a bloque (E1) de dicha señal recibida, que suministra para cada bloque de símbolos recibido un bloque de símbolos igualados formados cada uno por un conjunto de bits, comprendiendo el procedimiento al menos una iteración de mejora (II) de una estimación de dicha señal recibida que comprende las etapas siguientes, para un bloque corriente de símbolos igualados:

- obtención (E2) de al menos un bit decodificado, por decodificación bit a bit de un subconjunto corriente de al menos un bit que pertenece a dicho bloque corriente de símbolos igualados;

- actualización (E3) de al menos un símbolo estimado durante dicha fase de inicialización o actualizado durante una iteración de mejora precedente, en función del o de los bits decodificados, que suministra un bloque de símbolos estimados actualizados, constituido por el o los bits decodificados y por al menos un bit decodificado durante al menos una iteración de mejora precedente o durante dicha fase de inicialización;

- determinación (E4) de un bloque mejorado de símbolos igualados por anulación de las interferencias a partir de un igualador de tipo anulador de interferencias cuyos coeficientes se actualizan después de cada bit decodificado, teniendo en cuenta dicho bloque de símbolos estimados actualizados, convirtiéndose dicho bloque mejorado de símbolos igualados en el bloque corriente de símbolos igualados de una posible iteración siguiente.

2. Procedimiento de recepción según la reivindicación 1, en el que dicha etapa de obtención comprende las etapas siguientes:

- extracción (E21) de al menos un bit de uno de dichos símbolos igualados, denominados bits extraídos;

- actualización (E22) de dicho subconjunto corriente, a partir de al menos uno de dichos bits extraídos, que suministra un subconjunto actualizado;

- decodificación (E23) de canal de dicho subconjunto actualizado, que suministra el o los bits decodificados.

3. Procedimiento de recepción según las reivindicaciones 1 y 2, en el que dicha etapa de obtención implementa un desentrelazamiento de dichos conjuntos de bits de dichos símbolos igualados de dicho bloque corriente de símbolos igualados, inverso a un entrelazamiento implementado en la emisión.

4. Procedimiento de recepción según la reivindicación 3, en el que dicho desentrelazamiento restituye, en un orden de origen, bits entrelazados en la emisión según un entrelazamiento que distribuye dichos bits uniformemente en dichos bloques de símbolos y que garantiza que dos bits asociados consecutivamente a un bloque de símbolo se transmitirán en dos símbolos distintos.

5. Procedimiento de recepción según las reivindicaciones 3 y 4, en el que dicho desentrelazamiento es de tal forma que dos bits desentrelazados consecutivos provienen de dos posiciones de bits distintas en el seno de dos bloques de símbolos igualados distintos.

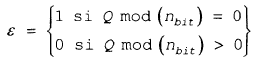

6. Procedimiento de recepción según la reivindicación 5, en el que para un entrelazador de tamaño T = nbloque * Q * nbit y para un bit dado que ocupa, antes de desentrelazamiento, una posición inicial definida por:

siendo dicho desentrelazamiento de tal forma que dicho bit dado ocupa, después de desentrelazamiento, una posición final definida por:

en la que:

nbloque corresponde al número de bloques de símbolos;

Q corresponde al número de símbolos que forman uno de dichos bloques;

nbit corresponde al número de bits que forman uno de dichos símbolos;

?b(b) designa la ley que permite la distribución de los bloques de símbolos;

?s(s, ?b(b)) = (s - ?b(b))mod(Q) designa la ley que permite la distribución de símbolos en el interior de cada bloque de símbolos;

?p(p, s, ?b(b)) = (p - ?b(b)) -

7. Dispositivo (400) de recepción de una señal de datos recibida compuesta por al menos un bloque de símbolos recibido y representativo de una señal fuente, comprendiendo dicho dispositivo medios de inicialización que comprenden medios (20) de igualación bloque a bloque de dicha señal recibida, que suministra para cada bloque de símbolos recibido un bloque de símbolos igualados formados cada uno por un conjunto de bits, comprendiendo el dispositivo medios de mejora de una estimación de dicha señal recibida, que implementa al menos una vez, en forma de una iteración, y para un bloque corriente de símbolos igualados:

- medios de obtención de al menos un bit decodificado, por decodificación bit a bit de un subconjunto de al menos un bit que pertenece a dicho bloque corriente de símbolos igualados;

- medios de actualización de al menos un símbolo estimado durante dicha fase de inicialización o actualizado durante una iteración de mejora precedente, en función del o de los bits decodificados, que suministra un bloque de símbolos estimados actualizados, constituido por el o los bits decodificados y por al menos un bit decodificado durante al menos una iteración de mejora precedente o durante dicha fase de inicialización;

- medios (43) de determinación de un bloque mejorado de símbolos igualados por anulación de las interferencias, a partir de un igualador de interferencias de tipo anulador cuyos coeficientes se actualizan después de cada bit decodificado, teniendo en cuenta dicho bloque de símbolos estimados actualizados, convirtiéndose dicho bloque mejorado de símbolos igualados en el bloque corriente de símbolos igualados de una posible iteración siguiente.

8. Producto de programa de ordenador descargable desde una red de comunicación y/o registrado en un soporte legible por ordenador y/o ejecutable por un procesador (80), comprendiendo el producto instrucciones (82) de código de programa para la ejecución de las etapas del procedimiento de recepción de al menos una de las reivindicaciones 1 a 6, cuando dicho programa se ejecuta en un ordenador.

Patentes similares o relacionadas:

Ecualización inteligente para un sistema multifásico de tres transmisores, del 29 de Julio de 2020, de QUALCOMM INCORPORATED: Un sistema de tres transmisores para transmitir símbolos multifásicos sucesivos, que comprende:

un codificador configurado para codificar […]

Ecualización inteligente para un sistema multifásico de tres transmisores, del 29 de Julio de 2020, de QUALCOMM INCORPORATED: Un sistema de tres transmisores para transmitir símbolos multifásicos sucesivos, que comprende:

un codificador configurado para codificar […]

Información de control en un sistema de comunicación inalámbrica, del 15 de Julio de 2020, de QUALCOMM INCORPORATED: Un procedimiento para enviar datos de tráfico e información de control en un sistema de comunicación inalámbrica, que comprende: realizar conformación de haces […]

Asignación dinámica de recursos ACK en un sistema de comunicación inalámbrica, del 15 de Abril de 2020, de QUALCOMM INCORPORATED: Un procedimiento para comunicación inalámbrica, que comprende: recibir una asignación semipersistente para un recurso de acuse de recibo, ACK, para un equipo de usuario, […]

Asignación dinámica de recursos ack en un sistema de comunicación inalámbrica, del 15 de Abril de 2020, de QUALCOMM INCORPORATED: Un procedimiento para comunicación inalámbrica, que comprende: recibir una asignación semipersistente para un equipo de usuario, UE, siendo válida […]

Señal de sincronización extendida para la detección de índice de símbolos, del 15 de Abril de 2020, de QUALCOMM INCORPORATED: Un procedimiento de comunicación inalámbrica, que comprende: determinar una primera secuencia de señal de sincronización extendida, […]

Método y dispositivo para cuantificar y retroalimentar la información de canal y precodificar datos, del 8 de Abril de 2020, de ZTE CORPORATION: Un método para cuantificar y retroalimentar la información de canal en un sistema polarizado doble, caracterizado porque comprende: recibir una señal piloto de […]

Transmisor con equilibrio de polarización, del 1 de Abril de 2020, de Tianma Micro-Electronics Co., Ltd: Un transmisor que comprende: un generador de datos de señalización L1 (Capa 1), configurado para generar datos de señalización […]

Procedimiento y aparato para la conformación de haces de información de control en un sistema de comunicación inalámbrica, del 25 de Marzo de 2020, de QUALCOMM INCORPORATED: Un procedimiento de envío datos de tráfico e información de control en un sistema de comunicación inalámbrica, que comprende: realizar […]